Fターム[5F033QQ35]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エツチングの速度差の利用 (676)

Fターム[5F033QQ35]に分類される特許

161 - 180 / 676

基板処理方法及び記憶媒体

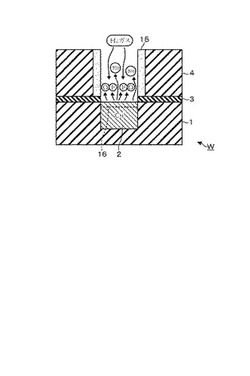

【課題】低誘電率膜であるSiCOH膜とCu配線との夫々の露出面に炭素の脱落したダメージ層及び酸化物が夫々形成された基板に対してダメージ層を回復させ且つ酸化物を還元すること。

【解決手段】SiCOHを含む層間絶縁膜4とCuを含む配線2との夫々の露出面に炭素の脱落したダメージ層15及び酸フッ化層16が夫々形成されたウエハWに対して、H2ガスの供給とシリコン及び炭素を含むTMSDMAガスの供給とを同一の処理容器51においてこの順番で連続して行うことによって、酸フッ化層16の還元処理及びダメージ層15の回復処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、炭化シリコン薄膜の機械強度を高め、膜の消失や剥離を防止する。

【解決手段】 ポーラスな誘電率低誘電率絶縁膜上に−CH2−結合が環状になってSiと結合し且つ二重結合を含む官能基を有する原料を用いて炭化シリコン薄膜を形成する工程と、前記炭化シリコン薄膜を所定パターンにエッチングしてハードマスクを形成する工程と、前記ハードマスクをエッチングマスクとして前記低誘電率絶縁膜をエッチングして配線形成用溝或いはビアホールの少なくとも一方を形成する工程とを設ける。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

パターン形成方法、及び半導体装置の製造方法

【課題】下地の性能を犠牲にすることなく、リフトオフ層が下地から剥離することを防止できるパターン形成方法、及び半導体装置の製造方法を提供すること。

【解決手段】本発明にかかるパターン形成方法は、基板上にカバー絶縁膜22を形成し、第1のレジストパターン104をマスクとして、金属膜パターン形成領域を取り囲むようカバー絶縁膜22に凹部103を形成する工程と、凹部103内に入り込むよう、カバー絶縁膜22上にリフトオフ層となる第2のレジストパターン25を形成する工程と、第2のレジストパターン25をマスクとして、金属膜パターン形成領域のカバー絶縁膜22に開口部を形成する工程と、第2のレジストパターン25の上から基板表面に金属膜を成膜し、第2のレジストパターン25とともに第2のレジストパターン25上の金属膜を除去して金属膜パターンを形成する工程とを備えるものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ダマシン配線形成時に、シード膜を配線用溝の側壁に確実に形成する。

【解決手段】下地絶縁膜1の上にプラズマシリコン窒化膜2、プラズマTEOS酸化膜3を形成する。プラズマTEOS酸化膜3は、高周波電源および低周波電源を用いる2周波励起プラズマCVD装置により、膜密度が上部に行くほど小さくなるように形成される。配線用溝をRIE法により形成した後、ウェットエッチングで膜密度が小さい部分を速くエッチングすることでテーパ形状の配線用溝3aを形成する。スパッタでバリアメタル膜4を形成する際に配線用溝3aの側壁にも確実に形成でき、銅膜5のメッキをボイドなしに形成できる。

(もっと読む)

ドライエッチングガス及びそれを用いたドライエッチング方法

【課題】半導体デバイスの製造プロセスにおいて、シリコン酸化膜、窒化シリコン膜、シリコン含有低誘電率膜等のシリコン含有膜のエッチング速度の低下を防ぎ、レジストや下地のシリコンなどに対して、選択的にエッチングすることができるドライエッチングガス及びそれを用いたエッチング方法を提供する。

【解決手段】CF3CF=CH2を含むドライエッチングガス。CF3CF=CH2の含有率は、流量比5〜100%であることが好ましい。

(もっと読む)

モリブデン系金属膜上の絶縁膜のドライエッチング方法および薄膜トランジスタパネルの製造方法

【課題】モリブデン系金属膜上の絶縁膜をドライエッチングする際に、選択比を比較的大きくする事ができる方法を提供する。

【解決手段】ドライエッチングにより、レジスト膜45の開口部46に対応する部分つまりソース電極9上におけるオーバーコート膜13にコンタクトホール14を形成し、また同時に、レジスト膜45の開口部47に対応する部分つまり金属膜21a上におけるオーバーコート膜13およびゲート絶縁膜4にコンタクトホール22を形成し、さらに同時に、レジスト膜45の開口部48に対応する部分つまり金属膜31a上におけるオーバーコート膜13にコンタクトホール32も形成する場合、エッチングガスとしてフッ素系ガス(SF6、CF4)、酸素ガスおよび窒素ガスからなる混合ガスを用いる事で窒化シリコン等からなるオーバーコート膜13とモリブデン系金属からなる金属膜31aとの選択比を大きくする。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜を備えた半導体装置において、膜剥がれの発生及びリークパスの形成を抑制する。

【解決手段】半導体装置は、複数の空孔を含む層間絶縁膜16を備えている。層間絶縁膜16は、単層構造の膜である。層間絶縁膜16における、下面領域に含まれる空孔の空孔径及び上面領域に含まれる空孔の空孔径は、上面領域と下面領域との間に介在する中央領域に含まれる空孔の空孔径よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

半導体素子の製造方法

【課題】 デュアルダマシンプロセスを同一チャンバ内で行っても、再現性よくビアホールを貫通させる技術が望まれる。

【解決手段】 層間絶縁膜上の第1のマスク膜及び層間絶縁膜に、層間絶縁膜の厚さ方向の途中まで達するビアホールを形成する。第1のマスク膜の上に、下層レジスト膜を形成し、その上に、配線溝に対応する開口を有する第2のマスク膜を形成する。チャンバ内において、O2とCOとのプラズマを用い、下層レジスト膜をエッチングするとともに、ビアホール内の一部には、下層レジスト膜を残す。下層レジスト膜の開口の平面形状が転写された開口を、第1のマスク膜に形成するとともに、下層レジスト膜を除去し、ビアホールをさらに掘り下げて、下層配線を露出させる。層間絶縁膜を厚さ方向の途中までエッチングして配線溝を形成する。配線溝及び前記ビアホール内を、導電部材で埋め込む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】ウエハから複数の半導体装置を分離形成する際に、微小なクラック、微小なチッピング及び微小な応力の発生まで回避できるようにする。

【解決手段】ウエハ100におけるスクライブライン領域101に第1の溝102を形成した後、第1の溝102に、ウエハ構成材料とは異なる材料を充填して充填部103を形成する。ウエハ100上に形成した配線層104を覆うように保持部材106を貼付した後、ウエハ裏面側を研磨し、充填部103の端部を露出させる。その後、充填部103を除去した後、配線層104を貫通すると共に第1の溝102と接続する第2の溝107を形成する。保持部材106を剥離して個片の半導体装置110を得る。

(もっと読む)

半導体装置の製造方法

【課題】 低誘電率膜のエッチング量を制御したデュアルダマシン構造を有する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に絶縁膜を形成する工程と、前記絶縁膜に対しエネルギー線を照射することによって前記絶縁膜を所定の深さまで改質する工程と、前記絶縁膜をエッチングして配線パターンを形成する工程と、前記配線パターン形成後に前記絶縁膜に対しエネルギー線を照射する工程と、配線パターンが形成された前記絶縁膜をエッチングしてホールパターンを形成する工程とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

半導体装置の製造方法

【課題】 今後の素子の微細化に対応できる、貫通電極を備えた半導体装置の製造方法を提供すること。

【解決手段】 半導体装置の製造方法は、第1の主面および該第1の主面に対向する第2の主面を有する半導体基板10と、半導体基板10の第1の主面上に設けられた電極パッド26と、半導体基板10の前記第1の主面と前記第2の主面との間を貫通する貫通孔100内に設けられ、電極パッド26と接続する貫通電極23とを具備してなり、貫通孔100の前記第1の主面側には、電極パッド26と貫通電極23とが直接的に接続する第1の接続部と、電極パッド26と貫通電極23とが間接的に接続する第2の接続部とを含み、前記第1の主面上に電極パッド26を形成する工程と、半導体基板10を加工し、貫通孔100を形成する工程であって、貫通孔100内において電極パッド26の一部が露出する前記工程と、貫通孔100内に貫通電極23を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】微細なパターンを精度良く形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工体1上にCを含む材料からなる芯材2を選択的に形成する工程と、芯材2の上面および側面を覆うように、酸素を含まない材料からなる保護膜3を形成する工程と、保護膜3を介して芯材2と被加工体1を覆うように酸化膜4を形成する工程と、芯材2の側方に少なくとも酸化膜4からなる側壁5を加工形成する工程と、少なくとも芯材2を除去した後、側壁5をマスクとして用いて被加工体1をエッチングし、側壁5のパターンを転写する工程と、を含む。

(もっと読む)

161 - 180 / 676

[ Back to top ]