Fターム[5F033QQ35]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エツチングの速度差の利用 (676)

Fターム[5F033QQ35]に分類される特許

141 - 160 / 676

半導体装置の製造方法

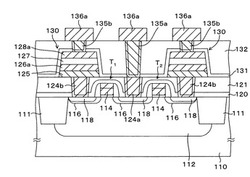

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

集積回路装置及びその製造方法

【課題】チップ面積が小さく、製造コストが低い集積回路装置及びその製造方法を提供する。

【解決手段】集積回路装置の製造方法において、複数の第1絶縁層及び複数の第2絶縁層を1層ずつ交互に積層させて積層体を形成すると共に、少なくとも2層の前記第2絶縁層内に少なくとも2本の配線を形成する工程と、前記積層体における前記積層体の積層方向から見て前記配線から離隔した位置に、前記積層方向に延びるコンタクトホールを形成する工程と、前記第2絶縁層における前記コンタクトホールと前記配線との間の部分を除去する工程と、前記第2絶縁層が除去された部分及び前記コンタクトホールの内部に導電材料を埋め込む工程と、を実施する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上にザッピング素子1のヒューズ層12を形成し、ヒューズ層12を覆う第1の絶縁膜13を形成する。第1の絶縁膜13上にはヒューズ層12を覆うエッチングストッパー膜14を形成し、エッチングストッパー膜14を覆う第2の絶縁膜16を形成する。他の工程を経た後、第1のエッチング工程として、ヒューズ層12上で、第2の絶縁膜16をエッチングストッパー膜14に対して選択的にエッチングすることにより、エッチングストッパー膜14の表面を露出させる。次に、第2のエッチング工程として、ヒューズ層12上で、エッチングストッパー膜14を第1の絶縁膜13に対して選択的にエッチングすることにより、第1の絶縁膜13の表面を露出させる。

(もっと読む)

半導体装置

【課題】小型化が可能な半導体装置を提供する。

【解決手段】半導体装置において、第1の導電性材料からなる第1のコンタクトと、第2の導電性材料からなり、下端部が第1のコンタクトの上端部に接続された第2のコンタクトと、第3の導電性材料からなり、下面が第1のコンタクトの下面よりも上方に位置し、上面が第2のコンタクトの上面よりも下方に位置し、第1及び第2のコンタクトから離隔した中間配線と、を設ける。そして、第2の導電性材料に対する第1の導電性材料の拡散係数は、第2の導電性材料に対する第3の導電性材料の拡散係数よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置および半導体装置の製造方法

【課題】ディッシングを抑制することができる半導体装置の構造を実現する。

【解決手段】半導体装置200は、基板(シリコン基板)と、基板上に設けられた絶縁層(層間絶縁膜201)と、層間絶縁膜201に設けられた第1の配線溝と(配線溝202)、配線溝202に埋め込まれた第1の金属膜(Cuめっき膜206)と、を備え、配線溝202の底部が、凸部形状を有する。

(もっと読む)

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

絶縁膜、積層体、半導体装置および半導体装置の製造方法

【課題】誘電率が低く、半導体装置の製造に適用した際に絶縁不良等の問題を生じにくい絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成されたものであって、フッ素系ガスでエッチングした際のエッチングレートが、SiO膜の0.75倍以下であることを特徴とする。前記重合性反応基は、芳香環と、当該芳香環に直接結合するエチニル基またはビニル基とを有するものであり、前記重合性化合物において、前記芳香環由来の炭素の数は、当該重合性化合物全体の炭素の数に対して、15%以上、38%以下であるのが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】配線間のショートを抑制すること。

【解決手段】半導体基板10上に第1絶縁膜20を形成する工程と、前記第1絶縁膜の上面を研磨する工程と、研磨された前記第1絶縁膜に接続30孔を形成する工程と、前記接続孔の内面および前記第1絶縁膜上に前記第1導電層32を形成する工程と、前記接続孔内の前記第1導電層上に第2導電層34を形成する工程と、前記第1絶縁膜上の前記第1導電層を研磨し前記第1絶縁膜の上面を露出させる工程と、前記第2導電層のエッチングレートより前記第1導電層のエッチングレートが大きいエッチャントを用い、前記接続孔内上部の前記第1導電層をエッチングする工程と、前記絶縁膜上に配線層50を形成する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【目的】ウェット処理を行った場合でも絶縁膜上に庇形状が形成されない半導体装置の製造方法を提供する。

【構成】本発明の一態様の半導体装置の製造方法は、基板上に絶縁膜を形成する工程(S102)と、絶縁膜上に保護膜を形成する工程(S104)と、保護膜に第1の開口部を形成する工程(S114)と、第1の開口部内に保護膜よりもウェットエッチングレートが大きい犠牲膜を形成する工程(S116)と、第1の開口部内の犠牲膜に第1の開口部よりも幅の狭い第2の開口部を形成する工程(S122の一部)と、第2の開口部を転写することで絶縁膜に第3の開口部を形成する工程(S122の一部)と、第3の開口部が形成された後に、ウェット処理を行なう工程(S126)と、ウェット処理後に、第3の開口部内にバリアメタル膜を形成する工程(S128)と、第3の開口部内に導電性材料を埋め込む工程(S132)と、を備えたことを特徴とする。

(もっと読む)

基板処理方法及び記憶媒体

【課題】低誘電率膜であるSiCOH膜とCu配線との夫々の露出面に炭素の脱落したダメージ層及び酸化物が夫々形成された基板に対してダメージ層を回復させ且つ酸化物を還元すること。

【解決手段】SiCOHを含む層間絶縁膜4とCuを含む配線2との夫々の露出面に炭素の脱落したダメージ層15及び酸フッ化層16が夫々形成されたウエハWに対して、H2ガスの供給とシリコン及び炭素を含むTMSDMAガスの供給とを同一の処理容器51においてこの順番で連続して行うことによって、酸フッ化層16の還元処理及びダメージ層15の回復処理を行う。

(もっと読む)

141 - 160 / 676

[ Back to top ]