Fターム[5F033QQ70]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 合金化処理(熱処理を含む) (771) | シリサイド化 (724)

Fターム[5F033QQ70]に分類される特許

201 - 220 / 724

半導体装置及びその製造方法

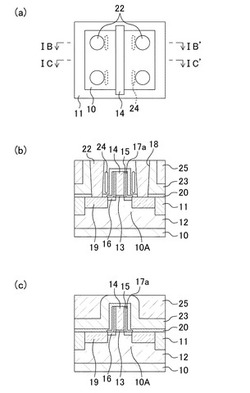

【課題】前記従来のエアーギャップを有するMISトランジスタ及びその製造方法では、ゲート電極の周囲にエアーギャップを設けるため、ゲート電極に近接して応力絶縁膜を形成することができない。

【解決手段】半導体装置は、ゲート絶縁膜13と、ゲート電極14と、ソースドレイン領域19と、コンタクトプラグ22と、応力絶縁膜23とを備えている。ゲート電極14の側方のうちゲート電極14とコンタクトプラグ22との間に位置する領域のみに空洞24が形成されており、応力絶縁膜23は半導体基板10上にゲート電極14を覆うように形成されており、半導体基板10におけるゲート電極14の直下に位置するチャネル領域に対して応力を生じさせる。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

半導体装置及びその製造方法

【課題】容易に製造することができ、トランジスタの性能を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2及びゲート電極3が形成されている。半導体基板1の表面の、平面視でゲート電極3を挟む位置に2個の不純物拡散層4が形成されている。2個の不純物拡散層4の表面に、ゲート絶縁膜2と半導体基板1との界面より低くなった掘り込み部6が設けられている。更に、半導体基板1のゲート絶縁膜2下の領域(チャネル)に応力を付加する応力付加膜が、少なくとも掘り込み部6内に位置している。

(もっと読む)

狭い間隔のフラッシュメモリコンタクト開口部を形成する方法

【課題】スケーリングされたフラッシュメモリ装置で低いビット線コンタクト抵抗を容易にする、改良されたフラッシュメモリ装置の製造技術が必要とされている。

【解決手段】 半導体装置ウェハ上でエッチマスクの一連の開口部をパターニングする際に使用するためにリソグラフィマスク上に光学的特徴を作るための方法(210)が提供され、この方法は、第1の方向に沿ってリソグラフィマスク上で互いから間隔をあけられた一連の光学的特徴を作るステップ(300,310)を含み、個々の光学的特徴は、エッチマスクにパターニングされる開口部に対する所望の第1の寸法より小さい第1の方向に沿った第1のマスク特徴寸法を有する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ誘電体膜の劣化を防止しながら、金属配線間を絶縁膜で所望に埋め込むことができる半導体装置の製造方法を提供すること。

【解決手段】シリコン基板(半導体基板)1の上方に下地絶縁膜9を形成する工程と、キャパシタQ1、Q2を下地絶縁膜9の上に形成する工程と、キャパシタQ1、Q2を覆う第1層間絶縁膜68を形成する工程と、第1、第2配線溝30、33と、該配線溝30、33の底部から下に延びる第1、第2コンタクトホール31、34とを第1層間絶縁膜68に形成する工程と、第1、第2配線溝30、33と第1、第2コンタクトホール31、34とに第1拡散防止膜35と第1銅膜36(第1導電体)とを埋め込む工程と、水素を含まない還元性ガス中において第1銅膜36をアニールする工程とを有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン溝(接続孔)内への異物の残留を回避し、配線接続の信頼性および半導体装置性能の向上を図る。

【解決手段】第4配線層の配線33上に絶縁膜34〜38を順次形成し(絶縁膜34,36,38はシリコン窒化膜からなる。絶縁膜35,37はシリコン酸化膜からなる)、絶縁膜38に溝パターン40a、40bをフォトリソグラフィを用いて転写する。絶縁膜38の溝パターン40を埋め込む反射防止膜41を形成し、さらに孔パターン43を有するレジスト膜42を形成する。レジスト膜42の存在下でエッチング処理を施し、絶縁膜38,37,36および絶縁膜35の一部に孔パターン43を転写する。その後、レジスト膜42,反射防止膜41を除去し、絶縁膜38をマスクとして溝パターン40を絶縁膜37に、孔パターン43を絶縁膜35に転写する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子及びその製造方法を開示する。

【解決手段】本発明は、コア/周辺回路領域でトランジスタの接合領域とメタルラインを、ビットラインを利用して連結せずメタルプラグを利用して連結することにより、コア/周辺回路領域に形成されるビットライン等もセル領域と同様に均一な形態のパターンを有することができるようにする。これを介し、本発明ではコア/周辺回路領域におけるビットラインパターニングの不良を防止し、ビットライン形成時にSPT(Spacer Pattern Technology)を適用することができる。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

温度測定用基板及び熱処理温度測定方法

【課題】熱処理温度470℃〜530℃を測定する温度測定用基板及び熱処理温度測定方法を提供すること。

【解決手段】温度測定用基板は、リンが注入されたp型シリコン基板を備える。熱処理温度は、p型シリコン基板の層抵抗値から測定される。リンのドーズ量は、5×1014atom/cm2〜1×1015atom/cm2である。

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】パッド電極の直下でのクラックの発生を抑制できるようにした半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成されたLOCOS膜3と、LOCOS膜3上に形成されたポリシリコン膜5と、LOCOS膜3上に形成されたILD膜7と、ILD膜7に形成され、ポリシリコン膜5を底面とする第1の開口部と、第1の開口部内に形成され、ポリシリコン膜5と接するパッド電極9と、を有する。ポリシリコン膜5は、ILD膜7よりも強度があり、衝撃に対する耐性が高いため、プローブ検査の際にクラックの発生を抑制することができる。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

コンタクト形成方法、半導体装置の製造方法、および半導体装置

【課題】 低抵抗率のコンタクトを実現した半導体装置の製造方法を提供する。

【解決手段】半導体と接した第1の金属層を酸化防止用の第2の金属層で覆った状態で、第1の金属層のみをシリサイド化し、酸素混入のないシリサイド層を形成する。第1の金属層の材料として、半導体との仕事関数の差が所定の値となるような金属が用いられ、第2の金属層の材料として、アニール温度で第1の金属層と反応しない金属が用いられる。

(もっと読む)

201 - 220 / 724

[ Back to top ]