Fターム[5F033QQ70]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 合金化処理(熱処理を含む) (771) | シリサイド化 (724)

Fターム[5F033QQ70]に分類される特許

41 - 60 / 724

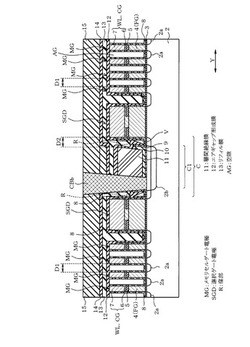

半導体記憶装置および半導体記憶装置の製造方法

【課題】隣接するメモリセルゲート電極間に空隙を形成することで結合容量を抑制し、複数のコンタクト同士の短絡を防止しメモリの信頼性を向上する。

【解決手段】半導体記憶装置は、複数の選択ゲート電極間に形成され、選択ゲート電極に近接した側の側面と当該選択ゲート電極との第2間隔が第1間隔より広い層間絶縁膜11と、複数のメモリセルゲート電極間に空隙AGを備えるよう当該空隙AGの上部を被覆し、複数の選択ゲート電極間においては当該選択ゲート電極の側面および層間絶縁膜11の側面に沿って形成され、その上部に窪部Rを備えて形成されたエアギャップ形成膜12と、複数のメモリセルゲート電極上のエアギャップ形成膜12上に形成され、複数の選択ゲート電極間ではエアギャップ形成膜12の窪部Rの内側に埋込まれたリフィル膜13と、複数の素子領域に接触するように層間絶縁膜11に形成された複数のコンタクトCBa,CBbを備える。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】耐圧確保に有利な構造を提供する。

【解決手段】実施形態の半導体記憶装置は、基板上で所定方向に平行に延伸した複数の素子分離領域と、隣接する素子分離領域に挟まれた素子領域上の第1絶縁膜と、素子領域上の所定方向に間隔を空けて形成され、第1絶縁膜の上に順に積層された電荷蓄積層、第2絶縁膜、及び制御ゲート電極をそれぞれ有する複数のワードラインと、その両側に1つずつ配置され所定方向の幅がワードラインより大きい選択トランジスタと、ワードライン及び選択トランジスタの上面を覆う層間絶縁膜と、ワードライン間に位置し上部を層間絶縁膜に覆われた第1空洞部と、選択トランジスタのワードラインとは反対側の側壁部に形成され上部が層間絶縁膜で覆われた第2空洞部を備える。実施形態の半導体記憶装置は、互いに隣接する選択トランジスタ間の基板表面に酸化膜が形成され、その下の所定方向に垂直方向の断面が凸型形状になっている。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、Si基板の表面にシリサイド層を形成しつつ、Si基板の裏面における低融点金属とSi基板のSiとの相互拡散を防止できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本願の発明に係る半導体素子の製造方法は、Si基板の裏面に低融点金属を形成する工程と、該Si基板の表面に高融点金属層を形成する工程と、該高融点金属層の上にレーザ吸収層を形成する工程と、該レーザ吸収層にレーザ光を照射し、該低融点金属と該Si基板のSiとの相互拡散を防ぐように該低融点金属の温度を低く保ちつつ、該レーザ吸収層と該高融点金属層の界面、及び該高融点金属層と該Si基板の界面にシリサイド層を形成する工程と、該レーザ吸収層をエッチングする工程と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得る。

【解決手段】n型SiC層11上にNi層12が形成される(図1(a))。熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b))。この状態で酸化雰囲気中で熱処理を行う(図1(d))。還元雰囲気中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h))。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法及び半導体ウエハ

【課題】 導電体部を有し、複数の絶縁膜を除去して形成される半導体装置において、金属汚染を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】 導電パターンを有する配線層と、導電パターンの側面を囲む第1の絶縁膜を含む複数の絶縁膜と、を有する半導体装置の製造方法において、半導体ウエハ上に複数の絶縁膜を形成する工程と、配線層を形成する工程と、を有する。そして、半導体ウエハ上に複数の絶縁膜を形成する工程及び配線層を形成する工程の後に、複数の絶縁膜の一部の領域を除去し、開口を形成する工程と、を有する。ここで、第1の絶縁膜は、導電パターンの配置位置のうちウエハの最外周に最も近い位置よりも半導体ウエハの外周に近い位置まで配置されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

41 - 60 / 724

[ Back to top ]