Fターム[5F033QQ76]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱酸化 (553)

Fターム[5F033QQ76]の下位に属するFターム

選択酸化 (17)

Fターム[5F033QQ76]に分類される特許

521 - 536 / 536

半導体装置およびその製造方法

【課題】 コンタクトホール側壁に形成するスペーサ用絶縁膜がシリコン基板と接触しない構成とし、且つRIE加工工数を低減する。

【解決手段】 NANDフラッシュメモリで、メモリセル領域2のゲート電極5、5間のコンタクトホール8と周辺回路領域3の高耐圧トランジスタ6のコンタクトホール9とに、層間絶縁膜20の側壁にスペーサとしてのシリコン窒化膜21を形成する構成である。シリコン窒化膜21の下端部は、シリコン基板1との間に、シリコン酸化膜17もしくは18を介在させている。シリコン基板1へのストレスを緩和してゲート酸化膜の電子トラップを低減する。また、シリコン窒化膜のRIE加工回数を減らすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化された半導体装置において、半導体素子相互間及び配線相互間に層間絶縁膜が十分に埋め込む。

【解決手段】半導体基板1に形成された半導体素子と、半導体素子上及び半導体基板1上に位置し、下地膜としての第1の絶縁膜9aと、第1の絶縁膜9a上に位置し、O3とTEOSを反応させるCVD法により形成された第2の絶縁膜9bと、第2の絶縁膜9b上に位置し、プラズマCVD法により形成され、表面がCMP法により平坦化された第3の絶縁膜9cと、第1乃至第3の絶縁膜に形成され、半導体素子上に位置する接続孔10a,10bと、接続孔10a,10bに埋め込まれた導電体11a,11bと、第3の絶縁膜9c上に形成され、導電体11a,11bを介して半導体素子に接続する配線12a,12bとを具備する。

(もっと読む)

表示装置および表示装置の製造方法

【課題】駆動側基板上の信号線と対向側基板上の透明電極との間に形成される寄生容量が大きいと、信号線によって伝送される映像信号に波形のなまりや遅延が生じたり、あるいは基板外部から映像信号を供給する駆動ICの負荷が増大したりする。

【解決手段】ガラス基板41(駆動側基板)上の第2のガラス基板(対向側基板)42と対向する領域内に信号線33(33R,33G,33B,33P)を配線する配線構造を採る場合において、ガラス基板41上の酸化膜43に凹部45を形成し、この凹部45内に信号線33を配線することにより、透明電極44と信号線33との間の距離を拡大して透明電極44と信号線33との間に形成される寄生容量を低減する。

(もっと読む)

半導体装置の製造方法

【課題】 比較的低い温度で、配線層の良好な埋め込みが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、配線層を略平行に形成する工程と、少なくとも配線層の側壁にシリコン層を形成する工程と、配線層を覆うように絶縁膜を形成し、配線層に挟まれた領域にボイドを残す工程と、シリコン層を酸化して体積膨張させ、絶縁膜の間のボイドを押しつぶす工程とを含む。更に、絶縁層上に、絶縁層の酸化を促進する触媒層を形成する工程を含んでも良い。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】 気密性や耐湿性、耐薬品性に優れた半導体パッケージ構造を得る。

【解決手段】 半導体基材と、該半導体基材の一方の面側に配置された機能素子及び該機能素子に第1の配線を介して電気的に接続されたパッドと、該パッドと電気的に接続され前記半導体基材の一方の面から他方の面に至る微細な孔内に絶縁膜Aを介して第1の導電体を充填してなる貫通電極とを少なくとも備えてなる第1の基板、及び前記機能素子の周囲に配置された封止材を用いて前記第1の基板の一方の面と接合されてなる第2の基板からなる半導体パッケージであって、前記絶縁膜Aは、前記半導体基材の他方の面に配置される絶縁膜B、前記半導体基材の外側面に配置される絶縁膜C及び前記封止材の外側面に配置される絶縁膜Dと連結して形成した半導体パッケージとした。さらに前記絶縁膜の外側を導電体で二重に覆ったものとすればなお良い。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

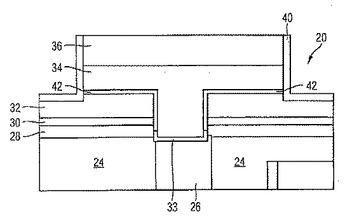

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 誘電体膜の段差被覆性がよく、かつ誘電体物質の廃棄量を少なくする。

【解決手段】 下地膜8上に、パターニングされた下部電極11を形成する工程と、インクジェット方式の塗布機構を用いて、下部電極11上に誘電体物質を塗布する工程と、塗布された誘電体物質を加熱することにより、下部電極11上に誘電体膜12を形成する工程と、誘電体膜12上に上部電極を形成する工程とを具備する。上部電極を形成する工程は、下地膜8上及び誘電体膜12上に層間絶縁膜を形成する工程と、層間絶縁膜に、誘電体膜上に位置する開口部を形成する工程と、開口部の中及び層間絶縁膜上に導電体を堆積する工程と、層間絶縁膜上から導電体を除去することにより上部電極を形成する工程とを具備する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

半導体基板及びその製造方法

【課題】表面上に引っ張り応力を有する層間絶縁膜等の絶縁膜が形成された半導体基板において、反りを抑制しうる半導体基板及びその製造方法を提供する。

【解決手段】シリコンウェーハ10と、シリコンウェーハ10の表面上に形成された層間絶縁膜に埋め込まれた多層配線12と、シリコンウェーハ10の裏面に形成され、引っ張り応力を有する絶縁膜であるシリコン窒化膜16bとを有している。シリコン窒化膜16bにより、多層配線12が埋め込まれた層間絶縁膜によりシリコンウェーハ10に与えられる応力が緩和され、シリコンウェーハ10の反りが抑制される。したがって、半導体基板の搬送系における吸着不良の発生を防止することができる。

(もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

強誘電体キャパシタデバイスおよびFeRAMデバイス

1つ以上のコンタクトプラグが通過して延びている基板と、上記基板上に形成された第1の層間絶縁膜とから、強誘電体キャパシタデバイス(例えばFeRAMデバイス)が形成されている。上記第1の層間絶縁膜上にはスペーサ層が形成されていて、このスペーサ層上には第1の酸素バリア層が形成されていて、この第1の酸素バリア層上にはバッファ層が形成されている。上記バッファ層上において、上記バッファ層と上記コンタクトプラグとの間に下地材料の層が形成されていて、第1の電極と第2の電極との間に誘電体層が挟まれている。上記デバイスに第2の酸素バリア層が塗布される。上記スペーサ層があれば、上記下地材料と上記コンタクトプラグとの界面まで酸化が及ぶことが抑制される。なぜなら、上記界面が、上記第1の酸素バリア層の下に位置しているからである。この結果、電気コンタクトが破損することはない。  (もっと読む)

(もっと読む)

配線基板の製造方法、半導体装置及びめっき装置

【課題】 導体層の研磨中に導体層の剥がれを防止できる配線基板の製造方法を提供することを目的とする。

【解決手段】 基板10の一方の面10aに少なくとも孔10bを形成する工程と、基板10の一方の面10a上、他方の面10e上及び側面10f上と、孔10bの内面上とに、めっき給電層14を形成する工程と、電解めっきにより、めっき給電層14を介して、基板10の一方の面10a上、他方の面10e上及び側面10f上に形成され、かつ孔10bを埋め込む金属層18を形成する工程と、金属層18を研磨することにより、孔10bに金属層18が埋め込まれた金属層のパターン17a,17bを形成する工程とを有する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

高周波用伝送線路およびその製造方法

【課題】 比抵抗の低い半導体基板の上であっても、その上に形成した高周波用伝送線路の伝送損失を抑制できるようにする。

【解決手段】 信号線103およびグランド線104と半導体基板101との間に介在する絶縁膜102と、信号線103の両側の半導体基板101に形成された溝105とを備え、信号線103およびグランド線105は、半導体基板101に接している辺より半導体基板101に垂直な隣辺の方が長い長方形状の断面を有する。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

521 - 536 / 536

[ Back to top ]