Fターム[5F033QQ95]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803) | 除去対象 (877) | フッ化物、フッ素 (62)

Fターム[5F033QQ95]に分類される特許

1 - 20 / 62

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

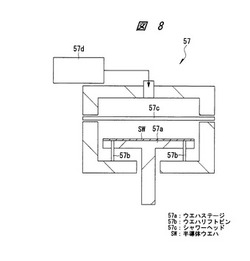

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

アッシュ後の側壁の回復

【課題】有効誘電率を増大させ、デバイスの性能を制限する可能性がある環境に低K薄膜を曝した後、より低い有効誘電率を維持する新しいプロセスを提供する。

【解決手段】集積回路の2つの導電性構成要素の間に存在する、有効誘電率を低下させる方法。その方法は、低K誘電体層の酸素が豊富な部分に対して選択的な気相エッチの使用を伴う。エッチング速度は、エッチプロセスが比較的高Kの酸素が豊富な部分を通過し、低K部分に達すると減じる。気相エッチプロセスが望ましい低K部分を容易に除去することはないため、エッチプロセスのタイミングを簡単に合わせることができる。

(もっと読む)

半導体装置の製造方法及び処理装置

【課題】薬液の除去性能を高く維持することができる半導体装置の製造方法及び処理装置を提供する。

【解決手段】レジストパターン3をマスクとして絶縁膜2をドライエッチングすることにより開口部4を形成する。絶縁膜2のドライエッチングの際に開口部4の内面に付着した反応生成物5に波長が200nm以下の紫外線を照射して、反応生成物5に含まれる有機成分を分解する。薬液を用いて、有機成分の分解後に開口部4の内面に残存している付着物6を除去する。付着物6が除去された開口部4内に導電膜7を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

ラジカルクリーニング方法及びラジカルクリーニング装置

【課題】Si基板上に形成されたSiO2膜を除去するラジカルクリーニング方法であって、ラジカルクリーニングを行う際に生成する残留生成物も除去することができるラジカルクリーニング方法を提供する。

【解決手段】プラズマによりHラジカル生成用ガスを分解してHラジカルを生成させ、このHラジカルとNF3ガスを反応させてN、F及びHからなるラジカルを生成するNFHラジカル生成工程と、真空槽内で、Si基板上に形成されたSiO2膜に前記N、F及びHからなるラジカルを照射することにより前記SiO2膜を除去するエッチング工程と、真空槽内で、前記エッチング工程で前記Si基板上に生成した残留生成物にマイクロ波を照射することにより、前記残留生成物を加熱して蒸発させて除去する残留生成物除去工程とを有する。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

エッチング方法及び装置

【課題】基板に形成された絶縁膜をエッチングするとき、絶縁膜の下地に酸素プラズマの悪影響が生ずるのを防止できるエッチング方法を提供する

【解決手段】本発明のエッチング方法は、絶縁膜222をプラズマ化させた処理ガスに晒し、絶縁膜222を厚さ方向に途中までエッチングする第一のエッチング工程と、第一のエッチング工程の終了後に残存する絶縁膜222を酸素プラズマに晒し、残存する絶縁膜222の表面に堆積した堆積物を除去する堆積物除去工程と、残存する絶縁膜222をプラズマ化させた処理ガスに晒し、残存する絶縁膜222をエッチングする第二のエッチング工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトの抵抗値のばらつきを抑え、歩留りを安定させることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に形成された導電層上に、絶縁膜を形成し、ハロゲンガスを含む第1のガスを用いて絶縁膜をドライエッチングして、導電層の表面を露出させ、露出した導電層に対しハロゲンガスを還元可能な第2のガスを用いて第1のプラズマ処理を行い、露出した導電層に対しC元素及びO元素を含みハロゲン元素を含まない第3のガスを用いて、第2のプラズマ処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、下層配線としてCu配線を含む多層配線と、前記Cu配線を形成するために用いられるCuアクセサリとが形成された半導体基板を、ポリイミド膜で覆う工程と、前記多層配線の最上層配線の表面および前記Cuアクセサリの表面を露出させる工程と、前記半導体基板をCu腐食防止剤の蒸気にさらして、前記最上層配線の表面および前記Cuアクセサリの表面にCu腐食防止膜を形成する工程と、前記最上層配線の表面に形成されたCu腐食防止膜を選択的に除去する工程と、前記Cuアクセサリの表面にCu腐食防止膜が形成された状態で、前記ポリイミド膜をベーク処理する工程とを有する。

(もっと読む)

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

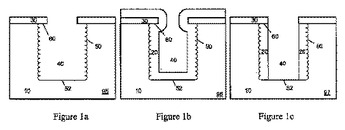

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

シリコン基板上のパターン修復方法及びシリコン基板上のパターン修復装置

【課題】シリコン基板上にエッチングによって形成されたパターンの間に成長した異物を除去して当該パターンの形状を回復させることのできるシリコン基板上のパターン修復方法及びシリコン基板上のパターン修復装置を提供する。

【解決手段】シリコン基板上にエッチングによって形成されたパターンの間に成長した異物を除去して当該パターンの形状を回復させるシリコン基板上のパターン修復方法であって、シリコン基板をチャンバー内に収容し、シリコン基板を160℃以上に加熱する加熱工程を有する。

(もっと読む)

基板処理方法及び記憶媒体

【課題】低誘電率膜であるSiCOH膜とCu配線との夫々の露出面に炭素の脱落したダメージ層及び酸化物が夫々形成された基板に対してダメージ層を回復させ且つ酸化物を還元すること。

【解決手段】SiCOHを含む層間絶縁膜4とCuを含む配線2との夫々の露出面に炭素の脱落したダメージ層15及び酸フッ化層16が夫々形成されたウエハWに対して、H2ガスの供給とシリコン及び炭素を含むTMSDMAガスの供給とを同一の処理容器51においてこの順番で連続して行うことによって、酸フッ化層16の還元処理及びダメージ層15の回復処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

半導体装置の製造方法

【課題】スタックされるプラグ同士の接続を良好に行う。

【解決手段】半導体基板上に第1の層間絶縁膜を形成し、第1の層間絶縁膜に第1のホールを形成し、第1のホール内にバリア膜を形成し、第1のホール内に導電材を充填して第1のプラグを形成し、第1の層間絶縁膜上に第2の層間絶縁膜を形成し、第2の層間絶縁膜に第1のプラグに達する第2のホールを形成し、第2のホール内で前記バリア膜上端部を選択エッチングし、第2のホール内に、第1のプラグに接続する第2のプラグを形成する、半導体装置の製造方法。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン酸化膜に対して、高選択比にシリコン窒化膜をエッチングすることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、フルオロカーボンガスを含むエッチングガスを用いて、シリコン窒化膜5の上に設けられた層間絶縁膜6をドライエッチングする第一の工程と、第一の工程に引き続き、酸化性ガスを供給してプラズマを発生させて、サイドウォール4の上に設けられたシリコン窒化膜5をドライエッチングする第二の工程と、を含み、第二の工程は、フルオロカーボンガスを供給しないことを特徴とする。

(もっと読む)

1 - 20 / 62

[ Back to top ]