Fターム[5F033RR02]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040)

Fターム[5F033RR02]の下位に属するFターム

Fターム[5F033RR02]に分類される特許

21 - 40 / 103

半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜の膜強度を十分に確保する。

【解決手段】第1の配線層絶縁膜と、第1の配線層絶縁膜に埋め込み形成されている複数の第1の銅配線8と、第1の銅配線8上及び第1の配線層絶縁膜上に形成されている層間絶縁膜(第2の低誘電率膜10)と、を有する。層間絶縁膜上に形成されている第2の配線層絶縁膜と、第2の配線層絶縁膜に埋め込み形成されている複数の第2の銅配線16と、を有する。第1、第2の配線層絶縁膜は、第1、第2の低誘電率膜(第1の低誘電率膜4、第3の低誘電率膜11)を含む。層間絶縁膜は、第1及び第2の配線層絶縁膜よりも高強度である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】上層の配線が導電体や不純物拡散層からずれていても、上層の配線を導電体や不純物拡散層に接続することができるようにする。

【解決手段】第1プラグ210は第1絶縁層200に埋め込まれており、不純物拡散層110に接続している。第2プラグ310は第2絶縁層300に埋め込まれており、第1プラグ210に接続している。第3プラグ410は第3絶縁層400に埋め込まれており、第2プラグ310に接続している。第1配線510は第3絶縁層400の表面に位置しており、第3プラグ410に接続している。平面視において、第2プラグ310は、上面及び底面の幅が第1プラグ210及び第3プラグ410の上面及び底面の幅がより大きく、かつ中心が、第1プラグ210の中心及び第3プラグ410の中心の少なくとも一方からずれている。そして第1プラグ210の中心は第3プラグ410の中心からずれている。

(もっと読む)

半導体装置

【課題】内部回路の状態を正確に判定することができる、半導体装置を提供すること。

【解決手段】半導体装置1は、基板11上に複数の絶縁層121A〜121Jからなる絶縁層群12が積層されるとともに、回路形成領域Aが形成されている。この半導体装置1は、複数の絶縁層121A〜121H中に形成され、前記回路形成領域Aを囲むように設けられた第一のシールリング13と、この第一のシールリング13の外側に設けられたビアチェーン14と、ビアチェーン14の外側に設けられるとともに、前記複数の絶縁層121A〜121J中に形成され、前記回路形成領域Aを囲むように設けられた第二のシールリング15とを備える。

(もっと読む)

半導体装置

【課題】グラフェンのバリスティック(弾道)伝導性を利用し、パターン形状によらず電気抵抗の上昇を抑えることができ、さらにエレクトロマイグレーションやストレスマイグレーション等のマイグレーションに対する耐性に優れた低抵抗配線を備えた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、配線層絶縁膜5中に形成されたシングルダマシン構造を有する配線10と、コンタクト層絶縁膜2中に形成され、上層の配線10と下層の導電部材1を電気的に接続するコンタクト3と、コンタクト層絶縁膜2と配線層絶縁膜5との間に形成されたエッチングストッパ膜4と、配線層絶縁膜5上に形成された拡散防止膜6と、を有する。配線10は、芯材14と、芯材14の底面および両側面に接するグラフェン層13と、グラフェン層13の底面および両側面に接する触媒層12と、触媒層12の底面および両側面に接する下地層11とを含む。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法

【課題】

ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】

1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスの製造方法を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

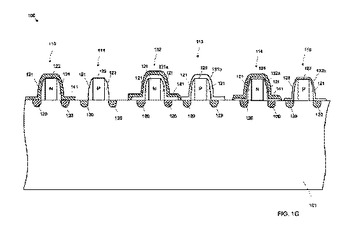

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置および記憶媒体

【課題】高速電子による有機膜の改質効果を十分に発揮することができるプラズマエッチング方法を提供すること。

【解決手段】プラズマエッチングによりエッチング対象膜にホールを形成するにあたり、プラズマ生成用高周波電力印加ユニットをオンにして処理容器内にプラズマを生成する第1条件と、プラズマ生成用高周波電力印加ユニットをオフにして処理容器内のプラズマを消滅させる第2条件とを交互に繰り返し、第1の直流電源から、第1条件の期間よりも第2条件の期間のほうが印加電圧の絶対値が大きくなるように負の直流電圧を印加する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110との間に、酸化しても導電性を有する導電材料(例えば金属)からなる導電層112を形成し、ここでは、導電プラグ110の下地膜を導電層112(Ag,Ni,Cu,Zn,In,Sn,Ir,Ru,Rh,Pd,Osから選ばれた少なくとも1種を材料として形成される。)とする。

(もっと読む)

半導体装置の製造方法

【目的】従来よりも比抵抗の低いW膜のプラグ或いは配線が得られる半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜に開口部を形成する工程(S106)と、前記開口部の少なくとも底面に、ルテニウム(Ru)膜を形成する工程(S112)と、前記Ru膜が形成された前記開口部内に、水素(H2)還元による化学気相成長(CVD)法によりタングステン(W)膜を埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において歩留まりを向上させること。

【解決手段】シリコン基板30の上方に金属からなる第1の配線66を形成する工程と、第1の配線66の上に層間絶縁膜69を形成する工程と、第1の配線66の表面が露出する開口69aを層間絶縁膜69に形成する工程と、開口69aの内面及び層間絶縁膜69の表面に、上記金属の拡散を抑制するバリアメタル膜72を形成する工程と、バリアメタル膜72上に第1の導電膜73を形成する工程と、第1の導電膜73の表面を化学機械研磨法により研磨し、バリアメタル膜72の表面を露出させる工程と、開口69aの内の第1の導電膜73上及びバリアメタル膜72上に、第2の導電膜80を形成する工程と、第2の導電膜80を、開口69aよりも拡大した領域に残して選択的に除去し、第2の配線80aを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線間の容量の増加が抑制された半導体装置およびその製造方法を実現する。

【解決手段】本実施形態における半導体装置10は、半導体基板100と、半導体基板100上に形成された層間絶縁膜110(第一の層間絶縁膜)と、層間絶縁膜110上に形成された、層間絶縁膜110よりも誘電率が低い層間絶縁膜120(第二の層間絶縁膜)と、層間絶縁膜120を貫通し、底部が層間絶縁膜110に入り込んでいるCu配線141と、を備えている。Cu配線141は、下方に向かって幅が狭くなる形状を有しており、層間絶縁膜120におけるCu配線141の側面の傾斜よりも、層間絶縁膜110におけるCu配線141の側面の傾斜が大きくなっている。

(もっと読む)

半導体装置の製造方法

【課題】シード膜の酸化を抑制して、電気的信頼性の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有する基板100の少なくとも凹部1aの内面1b上に、シード膜5を形成する工程と、シード膜5上に、シード膜5の構成材料より酸化されやすい材料からなる保護膜6を形成する工程と、保護膜6に熱処理を施す工程と、熱処理が施された保護膜6の少なくとも一部を除去し、シード膜5の少なくとも一部を露出させる工程と、少なくとも一部が露出したシード膜5に電流を供給して、シード膜5上に凹部1aに埋め込まれるように電解めっきによりめっき膜7を形成する工程と、凹部1aに埋め込まれた部分以外のめっき膜7を除去する工程とを具備することを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】比誘電率の低い層間絶縁膜を用いた半導体装置において、プラズマ処理時の層間絶縁膜へのダメージを軽減でき、ダメージ層を除去する際に形成されるアンダーカットを抑制する。

【解決手段】基板上に比誘電率の低い材料からなる絶縁膜4を形成する。次に、前記絶縁膜上にチャンバ内でSiOCH膜5を形成し、前記チャンバ内にプラズマを発生させた状態で徐々に膜中のカーボン濃度を減らし、前記SiOCH膜上に連続的にSiO2膜6を形成する。前記SiOCH膜と前記SiO2膜をハードマスクに用いて前記絶縁膜をプラズマ処理し、前記絶縁膜に溝7,8を形成する。その後、前記絶縁膜に形成した溝のエッチング表面をウェットエッチングし、プラズマ処理によるダメージ層と加工残渣物を除去する。

(もっと読む)

半導体装置の製造方法

【課題】例えばエアギャップ構造の形成に好適な、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に第1の絶縁膜を形成する工程と、第1の絶縁膜に溝を形成する工程と、第1の絶縁膜上面及び溝の内面を覆うように、Ruを含む第1の金属層を形成する工程と、第1の金属層上に、銅を含む第2の金属層を形成する工程と、第1の絶縁膜上の第2の金属層及び第1の金属層を研磨し除去して、第1の絶縁膜を露出させ、溝内に形成された第1の金属層及び第2の金属層を残す工程と、研磨によって露出した第1の絶縁膜を上面から少なくとも一部除去する工程と、第1の絶縁膜の上方に、第1及び第2の金属層の少なくとも上面を覆う第2の絶縁膜を形成する工程とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】、配線層とその下層のプラグ層との配線抵抗を抑えながら下層のプラグの埋め込み性を向上させることが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Cu配線10と、Cu配線10の下層側でCu配線10と接触して接続されるCuプラグ20と、Cuプラグ20の底面側及び側面側に配置された、Cuに対してバリア性を有するBM膜240と、Cu配線10とCuプラグ20との内Cuプラグ20側に選択的に、かつCuプラグ20とBM膜240との間に介在するように配置された、BM膜240よりも前記導電性材料に対して濡れ性が高いRu膜242と、Cu配線10とCuプラグ20とが接触する箇所を少なくとも除くCu配線10の底面側と、Cu配線10の側面側とに配置された、Cuに対してバリア性を有するBM膜244と、を備えたことを特徴とする。

(もっと読む)

21 - 40 / 103

[ Back to top ]