Fターム[5F033RR02]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040)

Fターム[5F033RR02]の下位に属するFターム

Fターム[5F033RR02]に分類される特許

81 - 100 / 103

成膜装置及び成膜方法

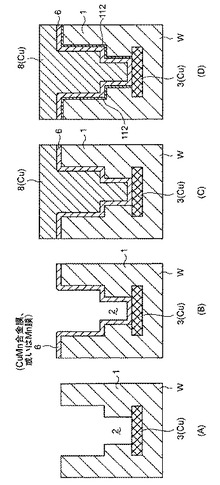

【課題】例えばCuMn合金膜やMn膜等を、CVD等の熱処理によって形成することにより、微細な凹部でも、高いステップカバレッジで埋め込むことができ、しかも、同一の処理装置で連続的な処理を行うようにして装置コストを大幅に低減化することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器14内で、銅を含む銅含有原料ガスと遷移金属を含む遷移金属含有原料ガスと還元ガスとにより被処理体の表面に、熱処理により薄膜を形成する。これにより、例えばCuMn合金膜やMn膜等を、CVD等の熱処理によって形成することにより、微細な凹部でも、高いステップカバレッジで埋め込むことができる。

(もっと読む)

処理方法および処理装置

【課題】水蒸気を含む処理ガスを用いて、下地の金属やその近傍の部位にダメージを与えない温度で金属の表面に形成された酸化物を除去することができる処理方法および処理装置を提供すること。

【解決手段】水蒸気と水蒸気よりも酸化膜に対する除去能の高い除去補助物質とを含む処理ガスを表面に酸化膜が形成された金属部分を有する被処理体に接触させ、酸化膜を除去する。

(もっと読む)

パッシベーション及びポリイミドにより包囲されたコンタクト及びその製造方法

半導体装置(10)は、ボンディングパッド(28)と最終相互接続層(16)との間にコンタクトを有し、そのコンタクトは、最終相互接続層(16)とボンディングパッドとの間にバリアメタル(26)を含む。パッシベーション層(18)及びポリイミド層(22)の両方により、最終相互接続層(16)とボンディングパッド(28)とが分離される。パッシベーション層(18)は、最終相互接続層(16)と接するように第一の開口(20)を形成すべくパターン化される。また、ポリイミド層(22)も、パッシベーション(18)を貫通する第一の開口(20)よりも内側にあって、それゆえにより小さな第二の開口(24)を残存させるようにパターン化される。次に、バリア層(22)が最終相互接続層(16)と接して堆積されて、ポリイミド層(22)により境界を形成する。次に、バリア(26)と接してボンディングパッド(28)が形成されると、その後、ボンディングパッド(28)に対してワイヤボンド(30)が形成される。  (もっと読む)

(もっと読む)

マルチプレート分離構造を有する半導体デバイス

マイクロエレクトロニクスアセンブリ及びマイクロエレクトロニクスアセンブリの製造方法が提供される。マイクロエレクトロニクスアセンブリは、分離トレンチ(62)が形成された半導体基板を含む。分離トレンチ(62)は、第1及び第2の対向内壁(74,76)及び底面(78)を有する。第1及び第2の導電プレート(106)は、第1及び第2の導電プレート(106)間に間隙(90)が存在するように、分離トレンチ(62)の第1及び第2の対向内壁(74,76)上にそれぞれ形成される。第1及び第2の半導体デバイス(114)は、半導体基板内の分離トレンチ(62)の対向する側に形成される。上記の方法は、半導体基板内にトレンチ(62)を形成する工程と、そのトレンチ内に第1及び第2の導電プレート(106)を形成する工程と、トレンチ(62)の対向する側において半導体基板内に第1及び第2の半導体デバイス(114)を形成する工程とを含む。  (もっと読む)

(もっと読む)

窒化膜サイドウォール付きゲートを有する半導体装置の製造方法

【課題】 ストッパー窒化膜肩部の形状が垂直化され、コンタクトホールエッチングでの窒化膜の後退を低減することができる窒化膜サイドウォール付きゲートを有する半導体装置の製造方法を提供する。

【解決手段】 自己整合プロセスによりコンタクトを形成する窒化膜サイドウォール付きゲートを有する半導体装置の製造方法において、オフセット窒化膜32付きゲート31を生成後、ストッパー窒化膜を堆積させ、サイドウォールエッチング後、絶縁膜34を生成しCMP処理を施し、更に平坦化された前記ゲート31上に層間絶縁膜36を生成し、この層間絶縁膜36生成後のCMP処理を省くようにしたものである。

(もっと読む)

半導体装置の製造方法

【課題】微細な配線構造を形成可能であると共に、製造コストの低い半導体装置の製造方法を提供する。

【解決手段】配線層11上の低誘電率材料からなる第1層間絶縁層13および第2層間絶縁層15のそれぞれを覆うSiO膜14,16を形成する。SiO膜14,16は、CVD法によりSiH4ガスとCO2ガスを用いて、ウェハを350℃〜500℃に加熱して形成する。このようにして形成されたSiO膜14,16は、実質的に窒素を含まないため、シリコン窒化膜等の反射防止膜18を形成する際にアンモニアガスや窒素ガス等の透過を抑制し、第1層間絶縁層13および第2層間絶縁層15に窒素に由来する塩基性物質の吸蔵を抑制する。その結果、レジストポイゾニングを抑制できる。さらに、SiO膜14,16は原料がガスのみであるので液体原料を使用するTEOS膜よりもCVD装置の汎用性が高まり、製造コストを低減できる。

(もっと読む)

バリア性向上のための酸素/窒素遷移領域を含むメッキシード層

【課題】 別個の拡散層及びシード層を利用する必要性を排除した、導電性材料、好ましくはCuの、向上した拡散特性を有するメッキシード層を含む相互接続構造体を提供すること。

【解決手段】 特に、本発明は、相互接続金属の拡散特性向上のためにメッキシード層内に酸素/窒素遷移領域を設ける。メッキシード層はRu、Ir又はそれらの合金を含むことができ、相互接続導電性材料は、Cu,Al、AlCu、W、Ag、Auなどを含むことができる。好ましくは、相互接続導電性材料はCu又はAlCuである。より詳細に言えば、本発明は、上部及び底部シード領域間に挟持された酸素/窒素遷移領域を含む単一のシード層を提供する。メッキシード層内に酸素/窒素遷移領域が存在することで、メッキシードの拡散バリア抵抗が顕著に向上する。

(もっと読む)

層間絶縁構造およびその形成方法

【課題】層間絶縁体、あるいは層内絶縁体および層間絶縁体としてエアギャップを統合する銅のインタコネクトを製造する方法を提供すること。

【解決手段】層間絶縁構造の形成方法であって、第1の金属層を提供する工程と、第1の犠牲層を堆積する工程と、エッチング停止層を堆積する工程と、第2の犠牲層を堆積する工程と、2層のハードマスクを形成する工程と、2層のハードマスクをパターニングしてビアマスクおよびトレンチマスクを生成する工程と、第2の犠牲層をエッチングしてビアを形成する工程と、エッチング停止層の剥き出し部分と第1の犠牲層とをエッチングして第1の金属層を剥き出しにする工程と、第2の犠牲層をエッチングしてトレンチを形成する工程と、バリア金属および銅を堆積し、平坦化して第2の金属層を形成する工程と、第1および第2の犠牲層を分解して上記犠牲層をエアギャップと交換する工程とを包含する。

(もっと読む)

半導体装置の製造方法

【課題】本発明の目的は、層間絶縁膜に密着用の膜を追加することなく、簡易に有機絶縁膜と無機絶縁膜との密着性を向上させることができる半導体装置の製造方法を提供することにある。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体基板1上に、有機絶縁膜12と無機絶縁膜11,13の積層膜を含む層間絶縁膜10を形成する工程と、層間絶縁膜10に対して電子線EBあるいは紫外線UVを照射して、有機絶縁膜12と無機絶縁膜11,13とを密着させる工程とを有する。

(もっと読む)

半導体装置

【課題】水分や酸化ガスの透過を防止して、耐水性および耐酸化性を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板11上の素子形成領域13を囲むように前記半導体基板上の層間絶縁膜14−1、12−2中に設けられ、Cuを主成分とするガードリングGR1、GR2と、前記層間絶縁膜とガードリングとの界面に設けられ、前記層間絶縁膜の構成元素と所定の金属元素との化合物を主成分とするバリア膜19とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】更なる配線層の微細化、層間絶縁膜の低誘電率化に対応することが出来る剥離防止のパターンを有する半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板1上に複数の絶縁膜2〜7を有し、複数の絶縁膜3〜7に埋設された配線32、42、52、62、72とを備え、複数の絶縁膜3、4が低誘電率材料を用いた絶縁膜である多層配線構造の半導体装置であって、半導体装置のコーナ部にすべての絶縁膜2〜7を貫通する貫通孔を形成し、貫通孔の全体に貫通ビア10を形成している。これにより、絶縁膜の剥離の発生を防止することができ、しかも貫通ビアは、ビアと配線をキャップ層で接続する部分が存在しないので、剥離防止の効果は大きい。

(もっと読む)

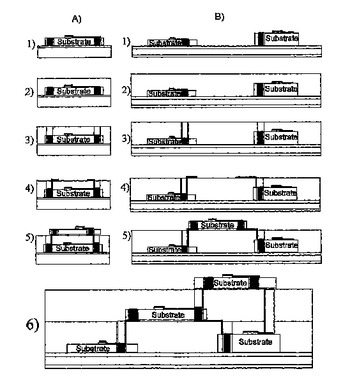

チップの架橋接続

システムは、第1半導体デバイスと第1電気接続とを有する第1チップ、第2半導体デバイスと第2電気接続とを有する第2チップ、および第3半導体デバイスと第3電気接続とを有する第3チップを有し、第3チップは、第1および第2チップの上面にスタックされ、第1および第2チップのそれぞれの少なくとも一部分を物理的に架橋し、前記第1および第2チップに接続される。  (もっと読む)

(もっと読む)

半導体デバイスおよびその構造体の製造方法

【課題】集積回路におけるRC遅延の容量成分Cを低くするための改良された方法の提供。

【解決手段】基板上に犠牲膜となる第1の絶縁材が堆積され、該第1の絶縁材上に、犠牲部分を有する第2の絶縁材が堆積される。上記第1および第2の絶縁層をパターニングして導電性材料を蒸着し余剰な導電材を除去して導電線が形成される。上記犠牲部分を除去するために上記第2の絶縁材の内部に気孔または開口部を形成して、透過性とする。この気孔または開口を通じて第1の絶縁材が除去され、上記導電線間に空隙が形成される。上記処理後に、第2の絶縁膜と導電膜の上にキャップ層を形成する。この結果、導電線間に空隙が形成される。

(もっと読む)

配線構造の形成方法,配線構造およびデュアルダマシン構造

【課題】応力が調整された配線構造とその製造方法を提供する。

【解決手段】 配線構造は、導電材料102を有する基板100から構成される。少なくとも1つの応力調整層106が内部に介在された複合誘電体層110が、基板100の上部に存在する。複合誘電体層110における導電機構Sが、少なくとも1つの応力調整層106を貫通し、導電部材102を電気的に接続する。

(もっと読む)

貫通ウェーハ相互接続

貫通ウェーハ相互接続および同相互接続を製造する方法が開示される。本方法は、導電ウェーハの材料を除去することによって、パターン形成したトレンチを形成するために導電ウェーハから出発する。パターン形成したトレンチは、深さがウェーハの前面から裏面に達し、全体的に導電ウェーハを内部分と外部分とに分割する環状開口部を有し、それによって導電ウェーハの内部分は、外部分から絶縁されて貫通ウェーハ導体としての役目をする。誘電材料が、パターン形成したトレンチの中へ形成または追加され、貫通ウェーハ導体を機械的に支持しおよび電気絶縁する。多導体を、アレイとして形成することもできる。  (もっと読む)

(もっと読む)

深トレンチのドープシリコン充填のプロセスシーケンス

膜堆積がトレンチの底部から上に向かって生じるようなシラン比に対する温度、圧力およびドーパントで第1の充填が実施される、深トレンチ構造のイン・シトゥー・ドープアモルファスシリコンによるボイドフリー充填方法が提供される。この第1の充填によって、100%を超えるステップカバレージウェルが達成される。第2の充填ステップにおいて、堆積レートに対するドーパントの影響を低減するために変更された条件で堆積が実施されることによって、トレンチ充填が、第1の充填の堆積レートを超える堆積レートで完了される。深トレンチキャパシタ構造を形成するためのこの方法の用途において、中間ステップはさらに、アモルファスシリコン層によるボイドフリー充填トレンチのキャッピング、その後のウェーハの平坦化、およびドーパントを再分布させるための熱アニーリングを含む。 (もっと読む)

半導体装置の製造方法

【課題】 所望の適正な加工状態を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11の主面上にゲート絶縁膜12を介してゲート構造13を形成する工程と、ゲート構造の上面、ゲート構造の側面及び半導体基板の主面を覆う第1の絶縁膜14を形成する工程と、フッ素を含まないガスを用いた異方性のプラズマ処理によりゲート構造の上面及び半導体基板の主面を覆う第1の絶縁膜を改質する工程と、改質された第1の絶縁膜15を除去する工程とを備える。

(もっと読む)

半導体装置

【課題】金属薄膜抵抗体を含む集積回路を備えた半導体装置において、レーザ照射による金属薄膜抵抗体の周辺領域へのダメージを低減する。

【解決手段】半導体基板1上に形成された下層側絶縁膜5と、下層側絶縁膜5上に形成された金属配線パターン11と、下層側絶縁膜5上及び金属配線パターン11上に形成された、少なくとも最上層にリン又はリン及びボロンが導入されたシリコン酸化膜15bをもつ下地絶縁膜15と、金属配線パターン11上の下地絶縁膜15に形成された接続孔17を備え、金属薄膜抵抗体21は下地絶縁膜15上から接続孔17内にわたって形成されて接続孔17内で金属配線パターン11と電気的に接続されている。

(もっと読む)

エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法

【課題】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法が開示される。

【解決手段】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法において、第1単結晶シリコン膜上に前記第1単結晶シリコン膜の表面を部分的に露出させる開口部を有する第1絶縁膜パターンを形成した後、前記開口部によって露出された第1単結晶シリコン膜上に単結晶シリコンで構成された第1シード膜を形成する。そして、前記第1シード膜が形成された結果物上部にシリコンソースガスを提供して、前記第1シード膜上にエピタキシャル膜を成長させながら、前記第1絶縁膜パターン上に非晶質シリコン膜を形成する。その後、前記非晶質シリコン膜の結晶構造を単結晶に転換させて前記エピタキシャル膜と非晶質シリコン膜から第2単結晶シリコン膜を獲得する。

(もっと読む)

多孔質膜の堆積方法

【課題】基板上に多孔質膜を堆積させる処理方法を提供する。

【解決手段】多孔質シリカ膜及びドープシリカ膜を堆積させる処理方法。本方法は、循環方式を用い、各サイクルは、最初にシリカをシリコンと共に共堆積させる段階と、次に選択的にシリコンを除去して多孔質構造体を形成する段階とを含む。好ましい実施形態では、共堆積は、プラズマ強化化学気相蒸着によって行われる。反応剤給送流れは、共堆積反応剤と選択的シリコン除去反応剤との混合物を含む。RF電力変調を使用して、共堆積段階及び選択的シリコン除去段階を制御し、後者は、RF電力が切られるか又は低レベルに低減される度に進行する。本発明を用いて、高度に均一な小さな孔隙及び望ましい空隙率プロフィールを有する多孔質膜を取得することができる。本方法は、半導体集積回路製造のための広範囲の低−k誘電体を形成するのに有利である。本方法はまた、他の用途のための他の多孔質膜を形成するのにも有利である。

(もっと読む)

81 - 100 / 103

[ Back to top ]