Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

301 - 320 / 5,243

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体装置

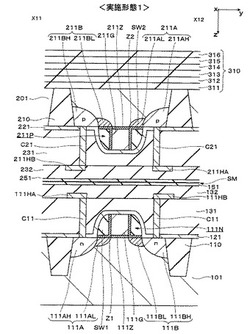

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理後も低い電気抵抗率を有する新規なCu合金膜を提供する。

【解決手段】基板上にて、基板及び/又は絶縁膜と直接接触するCu合金膜であって、前記Cu合金膜は基板側から順に、合金成分としてX(Xは、Ag、Au、C、W、Ca、Mg、Al、Sn、BおよびNiよりなる群から選択される少なくとも一種の元素)を含有するCu−Mn−X合金層(第一層)と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる層(第二層)で構成されたCu合金膜である。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

半導体素子

【課題】不良品の発生を容易に防止出来て歩留まりの向上と製造条件の確認の容易な半導体素子を実現する。

【解決手段】半導体素子本体の外表面を覆って設けられた絶縁膜と、この絶縁膜に設けられ前記半導体素子本体に一端側が接する外部接続用端子と、前記絶縁膜に穿設され一端側が前記外部接続用端子に接する配線取出し孔と、を具備する半導体素子において、前記外部接続用端子の前記配線取出し孔に接する面全体に一面が接し他面が前記絶縁膜に接して設けられ前記外部接続用端子の色と前記絶縁膜の色と異なる色を有し前記配線取出し孔の穿設時に除去されることにより前記配線取出し孔の穿設完了を識別する識別膜とを具備したことを特徴とする半導体素子である。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板に形成された開口部の側壁全体を均一に成膜することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一実施形態に係る半導体装置の製造方法は、底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

電気光学装置の製造方法

【課題】素子基板に絶縁膜を成膜した際にフッ素が混入しても、電界効果型トランジスターに特性異常が発生することを防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】素子基板10にシリコン酸化膜からなる絶縁膜12を成膜する第1絶縁膜成膜工程の後、画素トランジスター30(電界効果型トランジスター)の半導体層1aを形成する半導体層形成工程を行う前に、絶縁膜12に水素を導入する第1絶縁膜水素導入工程を行う。また、シリコン酸化膜からなる層間絶縁膜41を形成する第2絶縁膜成膜工程の後、層間絶縁膜41に対して水素の導入を行う第2絶縁膜水素導入工程を行う。このため、絶縁膜12や層間絶縁膜41にフッ素が混入していた場合でも、かかるフッ素は、水素と結合してフッ化水素として放出される。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

電極が埋設されたウエーハの加工方法

【課題】電極を被覆している二酸化珪素膜をエッチングすることなく、また電極をエッチングすることなくシリコン基板の裏面から電極を露出させることができる加工方法を提供する。

【解決手段】ウエーハの表面に保護部材を貼着する保護部材貼着工程と、シリコン基板21の裏面を電極214を露出させることなく研削する工程と、シリコン基板の裏面をエッチング液によってエッチングしシリコン基板の裏面に電極を露出させる工程とを含み、エッチング工程は、シリコンに対してエッチングレートが高いエッチング液を用いてシリコン基板をエッチングして二酸化珪素215膜が被覆された電極をシリコン基板の裏面に不完全に露出させる工程と、シリコンをエッチングするとともに二酸化珪素に対してエッチングレートが低いエッチング液を用いてシリコン基板をエッチングして二酸化珪素膜で被覆された電極をシリコン基板の裏面から突出させる工程とを含んでいる。

(もっと読む)

半導体装置、回路基板および電子機器

【課題】半導体基板と貫通電極との絶縁を確実とする半導体装置を提供する。

【解決手段】半導体装置10の一方の面14から他方の面16に形成された電極パッド24の裏面に到達する貫通電極13を形成した半導体装置10であって、他方の面16側には第1の絶縁膜20を介して電極パッド24が設けられ、貫通電極13を構成する貫通孔21と第1の絶縁膜20との境界面に、一方の面14側の開口よりも大きい開口を有し、貫通電極13を形成する際、他方の面16側の貫通孔21開口部内周に貫通電極13を構成する導電材料と電極パッド24との間に第2の絶縁膜23を備え、貫通孔21内壁面および第2の絶縁膜上に第3の絶縁膜22が設けられる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における配線形状を改善すること。

【解決手段】半導体装置の製造方法は、溝領域を規定する第1パターンを有する第1マスクを、サイドウォール形状の転写により、半導体装置の層間膜に設けられた金属膜上に形成する工程と、前記第1パターンに重なる少なくとも一つの開口を有する第2マスクを、平面図で見た場合に、前記2マスクが前記第1マスクに重なり、前記開口が前記溝領域に重なるように、形成し、第2パターンを形成する工程と、前記第1及び第2マスクを介して、前記層間膜をエッチングし、前記第1パターンを前記層間膜に転写させる工程と、前記第2マスクを介して前記層間膜をエッチングし、前記第2パターンを前記層間膜に転写させる工程とを具備する。前記第1パターンは、前記第2パターンとは異なる深さで前記層間膜に形成される。

(もっと読む)

高密度配線構造及びその製造方法

【課題】従来の製造方法と比べて、少ない工程数で形成可能であり、また、高精度の位置合わせ技術を必要としない、配線構造とその製造方法を提供する。

【解決手段】基板10の主表面10a上に、スペーサ絶縁膜20を形成する。次に、スペーサ絶縁膜をパターニングして、下部配線形成領域42の基板の主表面を露出させる。次に、露出した基板の主表面上、及び、スペーサ絶縁膜22の上側表面22a上に配線材料を堆積させて、基板の主表面上に下部配線52を形成するとともに、スペーサ絶縁膜の上側表面上に上部配線50を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ダイシング面からチップ領域への水分の浸入を抑制しつつ、スクライブ領域とチップ領域とを配線により接続する。

【解決手段】半導体装置は、チップ領域16と、スクライブ領域15と、2重に配置された第1シールリング18及び第2シールリング17と、チップ領域16からスクライブ領域15まで延伸する配線60と、を有する。半導体装置は、2重に配置された第1シールリング18及び第2シールリング17のうちの一方のシールリングが配線60を通すためにシールしていない層を、他方のシールリングでシールする構造となっている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、被加工材にパターンを形成するためのマスクの選択比を向上させ、プロセスコストの低減、歩留りの向上を可能とする。

【解決手段】被加工材上に所定パターンの有機膜を形成し、所定パターンの有機膜中に金属元素を導入し、金属元素が導入された所定パターンの有機膜を用いて、被加工材をエッチング処理する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】基板上に設けられた層間絶縁膜40に開口部48を形成する工程と、開口部48の側面上および底面上、ならびに層間絶縁膜40上に第1金属材料からなる第1膜10を形成する工程と、第1膜10上であって、開口部48内および層間絶縁膜40上に、第1金属材料よりも電気陰性度が小さい第2金属材料からなる第2膜20を形成する工程と、第2膜20上に、第2金属材料よりも電気陰性度が小さい第3金属材料からなる第3膜30を形成する工程と、熱処理する工程と、開口部48外に位置する第1膜10および第2膜20、ならびに第3膜30を研磨によって除去する工程と、を備える。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

301 - 320 / 5,243

[ Back to top ]