Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

281 - 300 / 5,243

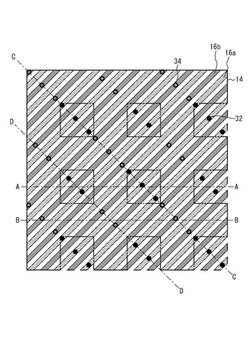

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】隣接するメモリセルゲート電極間に空隙を形成することで結合容量を抑制し、複数のコンタクト同士の短絡を防止しメモリの信頼性を向上する。

【解決手段】半導体記憶装置は、複数の選択ゲート電極間に形成され、選択ゲート電極に近接した側の側面と当該選択ゲート電極との第2間隔が第1間隔より広い層間絶縁膜11と、複数のメモリセルゲート電極間に空隙AGを備えるよう当該空隙AGの上部を被覆し、複数の選択ゲート電極間においては当該選択ゲート電極の側面および層間絶縁膜11の側面に沿って形成され、その上部に窪部Rを備えて形成されたエアギャップ形成膜12と、複数のメモリセルゲート電極上のエアギャップ形成膜12上に形成され、複数の選択ゲート電極間ではエアギャップ形成膜12の窪部Rの内側に埋込まれたリフィル膜13と、複数の素子領域に接触するように層間絶縁膜11に形成された複数のコンタクトCBa,CBbを備える。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】本発明は、絶縁膜を金属に密着させることができる半導体装置の製造方法と半導体装置を提供することを目的とする。

【解決手段】本願の発明に係る半導体装置の製造方法は、基板上に多結晶の金属を形成する工程と、該金属の表面粗さRaが0.051μmより大きくなり、かつ該金属の表面に1〜10μm径のランダムな方向に伸びる複数の穴が形成されるように、該金属の表面を1.0μm/min未満のエッチングレートでウェットエッチする工程と、該金属の表面に絶縁膜を形成する工程と、を備えたことを特徴とする。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

(もっと読む)

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、簡便に形成できて、チャージアップしにくいハードマスクを用いた半導体装置の製造方法を提供することを目的とする。

【解決手段】

半導体装置の製造方法であって、半導体基板上に形成された被加工膜上に、アミン化合物と水素化アルミニウムとの錯体を含有するアルミニウム膜形成用材料を塗布して、塗布膜を形成する工程と、前記塗布膜に対して、加熱処理および光照射処理から選ばれる少なくとも一種の処理を行いアルミニウム膜を形成する工程と、 該アルミニウム膜をエッチングしてハードマスクを形成する工程と、前記ハードマスクをマスクにして被加工膜をエッチングする工程を有することを特徴とする。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 2層構造のビットライン配線において、製造工程を減少することができる半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態に係る半導体記憶装置は、半導体基板を持つ。前記半導体基板上に第1及び第2のコンタクトプラグが設けられる。前記第1のコンタクトプラグに接する第1のビットラインが設けられ、前記第2のコンタクトプラグ上には第2のビットラインが設けられる。前記第1のコンタクトプラグは、前記第1のビットラインの上面と接し、かつ前記第2のビットラインと電気的に絶縁しており、前記第2のビットラインの底面の高さは、前記第1のビットラインの上面よりも高い。

(もっと読む)

半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体素子

【課題】熱(工程)に耐性のある配線構造を採用し、配線上の析出物の発生を抑制できる半導体素子を実現する。

【解決手段】半導体素子本体に接続する金材を含む配線パターンと、この配線パターンに一端側が接続され金材を含む接続端子と、前記半導体素子本体と前記配線パターンと前記接続端子とを覆う絶縁体と、を具備する半導体素子において、前記配線パターンあるいは接続端子の一方の面に一面が接し他面が前記絶縁体に接する面状のシリサイド体を具備したことを特徴とする半導体素子である。

(もっと読む)

281 - 300 / 5,243

[ Back to top ]