Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

5,161 - 5,180 / 5,243

配線構造及びその製造方法

【課題】 高温で保持されても動作不良を起こさない、信頼性の高い多層配線構造を実現する。

【解決手段】 第1配線102Aと第2配線111とは、層間絶縁膜(SiO2 膜104及びFSG膜105)中に形成されたビア110Aを介して接続されている。第2配線111におけるビア110Aの接続部分の近傍にダミービア110Bが接続されている。ダミービア110Bは、実使用時において閉回路の一部分とはならない。

(もっと読む)

プラズマ処理システムにおける選択性の制御方法

プラズマ処理システムにおける、半導体基板上の所定の層を介して機能をエッチングするための方法。本方法は、上記プラズマ処理システムのプラズマ処理室に基板を置くことを含む。また本方法は、上記プラズマ処理室内へエッチャント混合気を流し込むことも含み、上記エッチャント混合気は所定の層をエッチングするように構成されている。本方法はさらに、エッチャント・ソース・ガスからのプラズマを打撃することを含む。さらに本方法は、上記基板にバイアスRF信号を印加しながら、上記機能を少なくとも部分的に所定の層を介してエッチングすることを含む。上記バイアスRF信号は約27MHz乃至約75MHzの範囲のバイアスRF周波数と、バイアスRF電力成分とを有し、上記バイアスRF電力成分は、エッチ機能を、基板の第2の層への、予め決められた選択性しきい値より高いエッチング選択性でエッチングさせるように構成され、または上記機能を、バイアスRF周波数における予め決められたエッチ速度パラメータ及びエッチ・プロファイル・パラメータに従ってエッチングさせるように構成される。  (もっと読む)

(もっと読む)

減少されたコンタクト高さでのバイポーラ及びCMOSの集積回路構造体

【課題】 複数の高さのデバイスを含む集積回路構造体であって、このようなデバイスに形成されたコンタクトの高さを減少させるために保護層の高さを減少させた、改善された構造体を提供すること。

【解決手段】 単一の基板上に配置された複数の相補型金属酸化膜半導体(CMOS)トランジスタ及び複数の垂直バイポーラ・トランジスタを含む集積回路構造体のための方法及び構造体が開示される。垂直バイポーラ・トランジスタは、CMOSトランジスタより高さのあるデバイスである。この構造体においては、保護層が、基板の上に、及び、垂直バイポーラ・トランジスタとCMOSトランジスタとの間に配置される。配線層は保護層の上にある。垂直バイポーラ・トランジスタは、配線層と直接接触しており、CMOSトランジスタは保護層を通って延びるコンタクトによって配線層に接続されている。

(もっと読む)

半導体製品の製造方法

本発明は、半導体製品の製造方法に関するものである。この方法は、低k材料層を形成して、該低k材料層の中/上に導電性構造体を形成する工程と、該導電性構造体の少なくとも重複エリアにおいて、低k材料に対して範囲制限処理を施すことにより、交差領域における誘電率の値を上昇させる。これにより、高い誘電率値を有する交差領域および材料において上記導電性構造体から容量が形成される。  (もっと読む)

(もっと読む)

レジスト剥離中における多孔質低誘電率材料の損傷を阻止する方法

【課題】レジスト剥離中における多孔質低誘電率材料の損傷を阻止する。

【解決手段】多孔質低誘電率層内に形状を形成する方法が提供される。先ず、基板の上に、多孔質低誘電率層が配される。次いで、多孔質低誘電率層の上に、パターン形成されたフォトレジストマスクが配される。次いで、多孔質低誘電率層内に、形状がエッチングされる。形状のエッチング後は、形状の上に保護層が成長される。そして、保護層の一部が除去されるように、パターン形成されたフォトレジストマスクが剥離され、形状内に、保護層で形成された保護壁を残留させる。

(もっと読む)

補強された内部接続メタライゼーションを有するワイヤボンディングされた半導体部品

ドープされたシリコン基板製の半導体チップ2を含む半導体部品であって、前記チップは、半導体デバイスの中へドープされて構造化され、そして、コンタクトウインドウ中に内部接続メタライゼーション7を含み、前記半導体チップの前記内部接続メタライゼーションは、ワイヤボンド接続9によって、各外部接続メタライゼーションと接続され、前記内部接続メタライゼーションは、前記ドープされたシリコン基板上に開放格子構造体を有する補強システム8を含むことを特徴とする半導体部品。  (もっと読む)

(もっと読む)

調整可能な反射防止コーティングを含む構造およびその形成方法。

【課題】 調整可能な反射防止コーティングを含む構造およびその形成方法を提供することである。

【解決手段】 調整可能なエッチング耐性反射防止(TERA)コーティングを含む配線工程(BEOL)アプリケーションにおける配線構造が記載される。TERAコーティングは、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。TERAコーティングは、配線構造を形成するリソグラフィマスクの一部として役に立つことができ、または、それは、ハードマスクとして、ケミカルメカニカルポリシング(CMP)のストップ層として、またはCMP中の犠牲層として役立つことになる。

(もっと読む)

トレンチエッチングのためのラインエッジ粗さ低減

【課題】基板上の誘電体レイヤにおいてトレンチ深さまでトレンチをエッチングする方法を提供する。

【解決手段】ARCが前記誘電体レイヤ上に設けられる。厚さを有するフォトレジストマスクが前記ARC上に形成される。前記ARCがエッチングされる。1:1および2:1の間であるフォトレジストに対する誘電体のエッチング選択性で、トレンチが前記誘電体レイヤ中へエッチングされる。

(もっと読む)

強誘電体キャパシタデバイスおよびFeRAMデバイス

1つ以上のコンタクトプラグが通過して延びている基板と、上記基板上に形成された第1の層間絶縁膜とから、強誘電体キャパシタデバイス(例えばFeRAMデバイス)が形成されている。上記第1の層間絶縁膜上にはスペーサ層が形成されていて、このスペーサ層上には第1の酸素バリア層が形成されていて、この第1の酸素バリア層上にはバッファ層が形成されている。上記バッファ層上において、上記バッファ層と上記コンタクトプラグとの間に下地材料の層が形成されていて、第1の電極と第2の電極との間に誘電体層が挟まれている。上記デバイスに第2の酸素バリア層が塗布される。上記スペーサ層があれば、上記下地材料と上記コンタクトプラグとの界面まで酸化が及ぶことが抑制される。なぜなら、上記界面が、上記第1の酸素バリア層の下に位置しているからである。この結果、電気コンタクトが破損することはない。  (もっと読む)

(もっと読む)

フォトレジストストリッピングの間のバリヤー物質損失の最小化

銅インターコネクトを覆う暴露されたバリヤー層を含むエッチングされた誘電体物質を有する集積回路(IC)構造からフォトレジスト層を除去する方法。バリヤー層は、5窒化ケイ素または炭化ケイ素のような物質によって構成される。本方法は、一酸化炭素(CO)をさらすガス混合物を反応器に供給する工程を含む。ついで、反応器内で、プラズマを発生させる。フォトレジスト層は、ついで、暴露されたバリヤー層をほとんどまたは全くエッチングすることなく選択的に除去される。  (もっと読む)

(もっと読む)

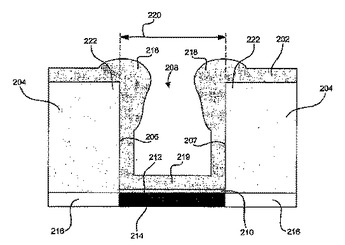

コンタクトの形成中、コンタクトホール幅の増大を防ぐ方法

一形態によれば、半導体ダイに位置するシリサイド層(214)上にコンタクトを形成する方法は、コンタクトホール(208)の各側壁(206、207)、及び、コンタクトホール(208)の底部に位置する自然酸化物層(210)に、バリア層(202)を堆積するステップを含み、各側壁(206、207)は、絶縁層(204)のコンタクトホールによって形成される。コンタクトホール(208)の各側壁(206、207)、及び、酸化物層(210)にバリア層(202)を堆積する(150)ステップにおいて、バリア層(202)の厚さを、コンタクトホール(208)の上部が、コンタクトホール(208)の底部よりも厚くなるよう最適化してもよい。この形態によれば、バリア層(202)の一部分(219)及びコンタクトホール(208)の底部に位置する酸化物層(210)を除去し、シリサイド層(214)を露出させるステップを含む方法も提供される。  (もっと読む)

(もっと読む)

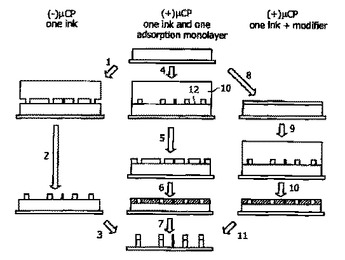

基板上にパターン化層を形成する方法

ソフト・リソグラフィのパターン化工程によって基板(24)上にパターン化された自己組織化単分子層(20)を形成する方法であって、その方法は、a)前記パターン化された自己組織化単分子層(20)の必要なパターンを画定するためのパターン化手段(10)を提供すること、b)前記基板(24)の表面(22)上に自己組織化単分子層(20)を形成すること、c)前記パターン化手段(10)を前記基板(24)の前記表面に適用することであって、前記パターン化手段(10)が前記基板表面の選択された領域に修飾剤を送達するように配置され、前記選択された領域が前記必要なパターン又はそのネガに対応し、前記修飾剤が化学物質を含み、且つ前記選択された領域で、前記自己組織化単分子層(10)の分子と前記基板(24)の前記表面との間の相互作用の強さを変えるように配置されること、並びにd)ステップc)の後、その分子と前記基板の前記表面との間でより低い相互作用の強さを示す前記自己組織化単分子層(20)の領域を選択的に除去又は置換し、それによって前記必要なパターンを有する自己組織化単分子層(20)を形成することを含む。修飾剤は、工程の要求に応じて、自己組織化単分子層の分子と基板の最上面との間の相互作用の強さを弱める又は高めるように選択されてもよい。  (もっと読む)

(もっと読む)

低K誘電体を半導体製造プロセスにおいて形成する方法

低K誘電体複合層(26,28)は、低kバリア層(26)及びバリア層(26)上の低K誘電体層(28)により形成される。結果的に疎水性の上部表面を有するように堆積するバリア層(26)を酸素プラズマで処理して表面を疎水性から親水性に改質する。後続の水を用いた洗浄は、バリア層(26)の表面の改質に起因して歩留まりを低下させるバリア層(26)上の欠陥を取り除くために非常に効果的である。水を用いた洗浄の後、低K誘電体層(28)をバリア層(26)の表面上に形成して低K誘電体である複合層(26,28)を完成させる。  (もっと読む)

(もっと読む)

一酸化二窒素を使用したエッチバック方法

ビアの中に有機プラグを形成する方法について記述する。ビアはシリコン含有誘電体を含む集積回路(IC)構造中に存在する。有機プラグを形成する方法は底部反射防止膜等の有機化合物を塗布することを含む。その有機化合物はビアを占める。そして、その方法は反応装置に一酸化二窒素(N2O)ガスを供給することに進み、そして反応装置中でプラズマを生成する。有機化合物の多くの部分が除去されて、ビアを占める有機プラグを残す。有機プラグは、典型的には、デュアルダマシンプロセスにおいて形成される。 (もっと読む)

レーザ除去タングステン・ヒューズ用配線保護要素(電気的構造体および形成方法)

【課題】集束放射線(52)によるヒューズ・リンク除去中に電気的構造体(25)を保護するための構造および対応する形成方法を提供すること。

【解決手段】構造体(1)は、ヒューズ要素(2)と、保護プレート(10)と、第1誘電体層(14)と、第2誘電体層(4)とを含む。構造体(1)は、半導体デバイス(5)内に形成される。保護プレート(10)は、ダマシン・プロセスを使用して第1誘電体層(14)内に形成される。第2誘電体層(4)は、保護プレート(10)および第1誘電体層(14)上に形成される。ヒューズ要素(2)は、第2誘電体層(4)上に形成される。ヒューズ要素(2)は、レーザビーム(52)で切断されるように構成される。第2誘電体層(4)の誘電率は、第1誘電体層(14)の誘電率より大きい。保護プレート(10)は、第1誘電体層(14)をレーザビーム(52)のエネルギーから遮蔽するように構成される。

(もっと読む)

半導体装置及びその製造方法

底部電極(11)及び又はキャパシタ誘電体上に導電性平滑化層(16、19)を形成することにより、幾何学的に高くされた電場を低下させると共に、電極を平滑化することで、形成されるMIMキャパシタの信頼性を向上させることができる。一実施形態において、難溶性窒化物で形成された第1のキャッピング層(14)上には、難溶性金属又は難溶性金属リッチ窒化物を含む第1の層(16)が形成される。更に、キャパシタ誘電体上には、難溶性金属(18)又は難溶性金属リッチ窒化物を含む第2の層(19)が形成される。導電性平滑化層(16、19)は、例えば、ゲート電極とゲート誘電体との間のトランジスタ等の他の半導体装置にも使用される。  (もっと読む)

(もっと読む)

低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体

【課題】 低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体を形成すること。

【解決手段】 調節可能で自己整合型の低静電容量集積回路のエアーギャップ構造は、相互接続層上で第二相互接続部に隣接する第一相互接続部と、該第一相互接続部及び該第二相互接続部の隣接する側部に沿って形成されたスペーサと、該第一相互接続部と該第二相互接続部との間に形成されたエアーギャップとを含む。エアーギャップは、第一相互接続部及び第二相互接続部の少なくとも一方の上面より上方で、かつ、該第一相互接続部及び該第二相互接続部の少なくとも一方の下面より下方に延び、スペーサ間の距離が該エアーギャップの幅を定める。エアーギャップは、第一相互接続部及び第二相互接続部の隣接する側部に自己整合する。

(もっと読む)

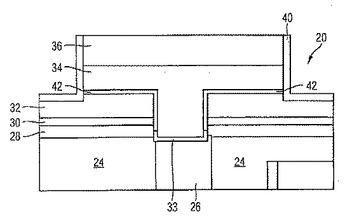

磁界を形成する導体

本発明は、電流が電気導体を流れるときに回路構成の少なくともさらにもう1つの部分に作用する磁界を生成する少なくとも1つの電気導体(40)を有する集積回路構成を提供している。電気導体(40)は、この回路構成のこの少なくともさらにもう1つの部分に向かって方向付けられた第1の側を有し、導電材料の主要線(41)と、その第1の側に接続され、磁性材料から成る少なくとも1つの磁界形成ストリップ(42)を備える。磁界形成ストリップ(42)により、電気導体(40)上の磁界プロファイルの不均一性が、低下される。  (もっと読む)

(もっと読む)

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

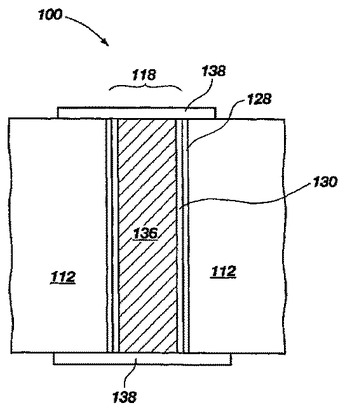

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

5,161 - 5,180 / 5,243

[ Back to top ]