Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

5,221 - 5,240 / 5,243

配線構造の形成方法

【課題】 絶縁膜に埋め込まれた配線同士の間における短絡を防止する。

【解決手段】 基板100上に形成されたFSG膜109に複数の配線用溝110を形成した後、各配線用溝110が完全に埋まるようにFSG膜109の上にバリアメタル膜(窒化タンタル膜111)及び配線用導電膜(銅膜112及び113)を順次堆積する。その後、各配線用溝110の外側の銅膜112及び113を研磨により除去した後、各配線用溝110の外側の窒化タンタル膜111を研磨により除去する。その後、研磨時に基板100に付着した異物を除去した後、FSG膜109の表面を研磨する。

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

配線構造及びその形成方法

【課題】 配線遅延を抑止し配線の微細化及び多層配線化を可能とする配線構造、及び当該配線構造の材料に固有の諸問題、例えば一方の材料の他方の材料への溶出等の不都合を解決して、信頼性の高い配線構造を実現する。

【解決手段】 Cu配線101と電気的に接続されるWプラグ102を形成するに際して、

三次元ソレノイドの製造方法および同方法によるデバイス

【課題】 CMOS製造技術を利用し、フォトマスキングを使用しないバック・エンド処理を利用する三次元ソレノイドの製造方法を開示する。

【解決手段】 この方法では、異なる残留応力ないし熱膨張係数を有する金属からなる二重層金属構造で各々形成された二つのサスペンド・アームが、二つのアームの中間にAlCuに形成された誘導コイルに結合されるように利用される。二酸化シリコンの絶縁層がサスペンド・アームから除去されると、アームの自由端が上方に湾曲し、誘導コイルが半導体基板の表面から三次元構造に立ち上がる。

(もっと読む)

多層配線構造を備えた半導体装置

【課題】本発明の課題は、多層構造の配線層に加わるパッケージの熱収縮による応力を効果的に緩和し、チップの保護膜であるパッシベーション膜のクラックの発生などを防止できる半導体装置を提供することである。

【解決手段】上記課題は、半導体基板11上に層間絶縁膜14を介して下層配線と13上層配線15とが形成される多層配線構造を備えた半導体装置において、層間絶縁膜14の面積が広くとれるように該層間絶縁膜14に開ける開口を小さくすることを特徴とする多層配線構造を備えた半導体装置にて解決される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 アルミニウムを主成分とする導体膜パターンを有する半導体集積回路装置の信頼性を向上させる。

【解決手段】 アルミニウムを主成分とする導体膜16dを有する第1層配線L1をドライエッチング法によってパターニングした後、その加工側壁の側壁保護膜18およびエッチングマスクとして使用したフォトレジストパターン17aをプラズマアッシング処理によって除去する。続いて、絶縁膜15bおよび第1層配線L1の表面に付着した塩素成分を、酸素ガスとメタノールガスとの混合ガスを用いたプラズマアッシング処理によって除去する。この際、フォトレジストパターン17a等のアッシング除去処理時は、ウエハの主面温度が相対的に低くなるようにし、塩素成分の除去処理時は、ウエハの主面温度が相対的に高くなるようにする。また、それらのプラズマアッシング処理を別々の処理室で行う。

(もっと読む)

配線構造およびその製造方法

【課題】感光性絶縁膜を用いたダマシン配線法により、微細で信頼性の高い多層配線構造を形成する。

【解決手段】感光性ポリシラザンを主成分とした感光性絶縁膜で第1ビアホール6を有するビアホール用絶縁膜7を形成し、全面にスピン塗布法で第2の感光性絶縁膜8を形成する。そして、フォトリソグラフィ法による露光/現像のみで上記第1ビアホール6の上部に配線溝9あるいは第2ビアホール10を形成する。そして、この配線溝9および第2ビアホール10に導電体材料を埋め込んでデュアルダマシン配線を形成する。ここで、感光性絶縁膜の下層に反射防止機能を有しそのまま層間絶縁膜として使用できる絶縁膜を形成する。

(もっと読む)

配線用シード膜および半導体装置の配線方法

【課題】 低コストにて歩留まり,信頼性,電気的特性の高い半導体装置を作製する。

【解決手段】 絶縁膜60上の下層絶縁膜61に銅の下層配線62を形成(S61)した後、プラズマCVD法により層間絶縁膜63,ストッパ膜64を順次形成し、ストッパ膜64における下層配線62上に孔64aを形成してから、ドライエッチングして層間絶縁膜63にコンタクトホール63aを形成する(S62)。その後、上層絶縁膜65を形成しマスク66を介してドライエッチングすることにより、上層絶縁膜65に溝部65aを形成すると共に、コンタクトホール63a中の上層絶縁膜65を除去する(S63)。そして、バリア膜67を形成(S64)した後、Cu−Ni膜,Cu−Zn膜,Cu−Zn−Ni膜のうち何れかを堆積してシード膜68を形成する(S65)。

(もっと読む)

配線基板の製造方法、半導体装置及びめっき装置

【課題】 導体層の研磨中に導体層の剥がれを防止できる配線基板の製造方法を提供することを目的とする。

【解決手段】 基板10の一方の面10aに少なくとも孔10bを形成する工程と、基板10の一方の面10a上、他方の面10e上及び側面10f上と、孔10bの内面上とに、めっき給電層14を形成する工程と、電解めっきにより、めっき給電層14を介して、基板10の一方の面10a上、他方の面10e上及び側面10f上に形成され、かつ孔10bを埋め込む金属層18を形成する工程と、金属層18を研磨することにより、孔10bに金属層18が埋め込まれた金属層のパターン17a,17bを形成する工程とを有する。

(もっと読む)

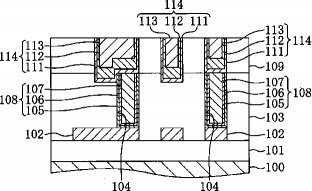

配線構造

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造を提供する。

【解決手段】 半導体素子が形成された基板上に絶縁膜103が多層形成され、絶縁膜103に形成された配線溝およびビアホールに金属配線剤が充填されて、配線および接続プラグが形成された配線構造において、絶縁膜103のうち少なくとも一層が対電子線感光性を有する材料から形成されており、絶縁膜103の層間にはバリア絶縁膜104を有し、前記金属配線剤は銅を含むものである。

(もっと読む)

低誘電率層間絶縁膜の形成方法

【課題】 半導体装置の層間絶縁膜などとして有用な低誘電率の膜を形成する方法と、この方法により形成される膜を提供すること。

【解決手段】 基材上に膜を成長させるのに十分な化学気相成長条件下で、シリルエーテル、シリルエーテルオリゴマー又は1以上の反応性基を有する有機ケイ素化合物を含む、有機ケイ素前駆物質を反応させて、約3.5以下の誘電率を有する層間絶縁膜を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

配線構造の製造方法

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造の製造方法を提供する。

【解決手段】 配線構造の製造方法が、半導体素子201の上にWプラグ203(下層配線)が形成された基板上に、対電子線感光性を有する材料を含む第二層間絶縁膜204(絶縁膜)を形成する工程と、第二層間絶縁膜204に電子線を照射して、第二層間絶縁膜204を露光する工程と、第二層間絶縁膜204を現像して未露光部を除去し、配線溝および/またはビアホールおよび/またはコンタクトホールを形成する工程とを有する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

多層配線構造の製造方法及びその構造

【課題】 上層配線層と下層配線層とを、アスペクト比の高いビアコンタクトで接続した多層配線構造を提供する。

【解決手段】 多層配線構造のビアコンタクト形成工程が、ビアホールの底面上に触媒層を設け、触媒層上にビアホールの上方に向ってめっき金属層を成長させ、めっき金属層でビアホールを充填する無電解めっき工程からなる。

(もっと読む)

多層配線構造

【課題】シールドによる配線容量の増加を抑え、シールド効果も補償できる多層配線構造を提供する。

【解決手段】半導体基板100上の酸化膜4上に所定の間隔で平行に配置された下層メタル配線3と、下層メタル配線3上の層間絶縁膜5上に下層メタル配線3と平行でかつ下層メタル配線3間に位置するように配置されたシールド用の配線メタル配線1と、メタル配線1上の層間絶縁膜6上に下層メタル配線3と重なるように配置された上層メタル配線2とから多層配線を構成し、シールド効果と同時に上層メタル配線2の全容量値の低減を図る。

(もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度が強く、かつ、放熱性に優れた半導体装置を提供する。

【解決手段】 シリコン基板10上に形成される配線層のうち、第1層から第3層を、コンタクト部11及びビア14a,14bにタングステン、配線13a〜13cに銅をそれぞれ用いてシングルダマシン工程によって形成し、第4層から第6層を、ビア15a〜15c及び配線13d〜13fに銅を用いてデュアルダマシン工程によって形成し、かつ、第4層から第6層におけるビア15a〜15cの径を第1層から第3層におけるコンタクト部11及びビア14a,14bの径の12.9倍以上とする。

(もっと読む)

多層配線構造及びその製造方法

【課題】 エレクトロマイグレーション耐性と、ストレスマイグレーション耐性を同時に向上させる多層配線構造及びその製造方法を提供する。

【解決手段】 AlCu膜103Cと、厚みが0〜15nmのTi膜との反応によりAl3 Ti層103DをAlCu膜とTiN膜の界面に形成することにより、界面拡散を抑制し、かつAl3 Ti層形成時に発生する引張り応力を低減し、EM耐性を向上させる。その後のFSG膜104AをHDP−CVD法で成膜する際に、ウェハ裏面に不活性ガスを流してウェハを冷却し、ウェハ温度を450℃以下にすることにより、FSGとAlCuの熱膨張率差に起因するAlCu膜の残留引張り応力の発生を低減し、SM耐性及びEM耐性を向上させる。さらに、FSG膜の上にSiON膜を設けることにより、FSG膜の遊離フッ素の上方への拡散を阻止して、上層配線の剥がれを防止する。

(もっと読む)

高周波用伝送線路およびその製造方法

【課題】 比抵抗の低い半導体基板の上であっても、その上に形成した高周波用伝送線路の伝送損失を抑制できるようにする。

【解決手段】 信号線103およびグランド線104と半導体基板101との間に介在する絶縁膜102と、信号線103の両側の半導体基板101に形成された溝105とを備え、信号線103およびグランド線105は、半導体基板101に接している辺より半導体基板101に垂直な隣辺の方が長い長方形状の断面を有する。

(もっと読む)

5,221 - 5,240 / 5,243

[ Back to top ]