Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

5,121 - 5,140 / 5,243

半導体装置及びその製造方法

【課題】 本発明の目的は、低抵抗であって且つ絶縁膜及び配線との間で高い密着性を有するバリアメタル膜を有する半導体装置を提供する。

【解決手段】 半導体装置は、基板(1)上に形成された絶縁膜(6,8)と、絶縁膜(6,8)中に形成された埋め込み配線(14)と、絶縁膜(6,8)と埋め込み配線(14)との間に形成されたバリアメタル膜(A1)とを有する。バリアメタル膜(A1)は、絶縁膜(6,8)が存在している側から埋め込み配線(14)が存在している側へ向かって順に積層されている金属酸化物膜(11)、遷移層(12a)及び金属膜(13)よりなり、遷移層(12a)は、金属酸化物膜(11)の組成と金属膜(13)の組成とのほぼ中間的な組成を有する単一の原子層よりなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 多孔質絶縁膜を含む層間絶縁膜の誘電率を実効的に低減させ、微細で高信頼性のダマシン配線を有する半導体装置の実用化を容易にする。

【解決手段】 下層配線1上に多孔質の第1低誘電率膜2bを含む第1層間絶縁膜2が形成され、第1層間絶縁膜2に設けられたビアホール3内にその側壁に設けられた第1側壁保護膜4を介して第1バリア層5およびビアプラグ6が形成される。同様に、多孔質の第2低誘電率膜7bを含む第2層間絶縁膜7のトレンチ8内にその側壁に設けられた第2側壁保護膜9を介して第2バリア層10および上層配線11が形成される。ここで、第1側壁保護膜4および第2側壁保護膜9は多孔質の低誘電率膜で成り、その空孔の含有率は30%以下であり、空孔の寸法は2nm以下である。

(もっと読む)

半導体装置の製造方法

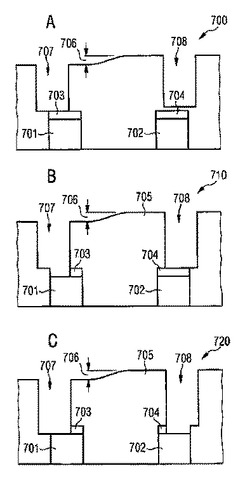

【課題】簡便な方法によりシリコン層のディッシングを抑制でき、安定した平坦性を得ることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、(1)凸部を有するシリコン層を覆う絶縁層のうちシリコン層の凸部の上方部分を除去することにより、シリコン層を露出させる工程と、

(2)前記絶縁層の残部でシリコン層を保護しながら、シリコン研磨用スラリーで露出したシリコン層を化学機械研磨する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置、例えばSRAMのメモリセルのα線によるソフトエラーを低減する。

【解決手段】基板1aをエッチングして第1配線溝HM1を形成し、第1配線溝HM1下の素子分離2(または素子分離溝2および絶縁層1c)をエッチングして第2配線溝HM2を形成し、第1配線溝HM1および第2配線溝HM2の内壁に沿って局所配線16a,16bを形成し、一方の局所配線16aを下部電極ELとして、その下部電極EL上に容量絶縁膜となる窒化シリコン膜17、さらに上部電極EUを形成することにより、容量CA1の面積を増加させて、メモリセルの記憶ノードに相対的に大きな静電容量を付加する。

(もっと読む)

半導体装置及びその製造方法

【課題】静電破壊耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極とドレイン領域とソース領域とを有する半導体装置であって、ドレイン領域は、ゲート電極の第1の側に形成された第1導電型の第1の不純物拡散領域18aと;第1の不純物拡散領域より深く形成された第1導電型の第2の不純物拡散領域20aと;第1の不純物拡散領域より浅く形成され、不純物拡散層より不純物濃度が高い第1導電型の第3の不純物拡散領域28a、28bと;第3の不純物拡散領域上に形成され、ドレインコンタクト部22Dに接続されるシリサイド膜32a、32bとを有し、ドレインコンタクト部とサイドウォール絶縁膜との間にシリサイド膜が形成されていない領域が存在しており、ドレインコンタクト部の下方の半導体基板内に第2の不純物拡散領域が形成されていない。

(もっと読む)

層構造の製造方法

本発明は、層構造の製造方法に関するものである。導電層および犠牲層をパターニングし、形成する。これらの層の上に、電気絶縁層を形成し、犠牲層の表面領域が露出するようにパターニングする。該露出した領域を除去し、そうすることによって露出したパターン形成された導電層の表面領域を、導電性材料からなる構造によって覆う。  (もっと読む)

(もっと読む)

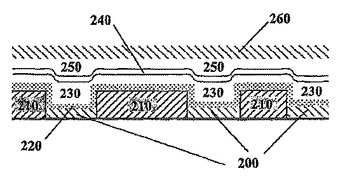

low−kスピンオン誘電体膜におけるクラッキングの減少

本発明は、low−k誘電体高分子のクラッキングを最小限に抑制するプロセスに関する。実施の一形態では、プラズマ蒸着された酸化シリコンSiOXで不動態化された金属層(220)上に配置される複合誘電体(230,240,250,260)を半導体基板(200)上に形成する方法がある。その方法は、プラズマ蒸着された酸化シリコンSiOX(220)で保護された金属層(210)上にスピンオン誘電体からなる第1の所定の厚さの第1の層を堆積させるステップ(310,320)を含む。次に、第2の所定の厚さの薄い応力緩和層(240)が、スピンオン誘電体からなる第1の層(230)上に堆積される(330)。薄い応力緩和層(230)上には、スピンオン誘電体からなる第3の所定の厚さの第2の層(250)が堆積される(340,350)。low−kスピンオン誘電体は、水素メチルシルセスキオキサン(HSQ)及びメチルシルセスキオキサン(MSQ)を含んでいてもよい。  (もっと読む)

(もっと読む)

低k材料上にTaN拡散バリア領域を堆積する方法(低k材料上のTaN拡散バリア領域のPE−ALD)

【課題】低k材料上にタンタル−窒化物(TaN)拡散バリア領域を堆積する方法を提供する。

【解決手段】この方法は、チャンバにおいてタンタル系前駆物質および窒素プラズマからプラズマ増強原子層堆積(PE−ALD)を実行することによって、低k材料基板(102)上に保護層(104)を形成することを含む。保護層(104)は、そのタンタル含有量よりも大きい窒素含有量を有する。次いで、タンタル系前駆物質ならびに水素および窒素を含むプラズマからPE−ALDを実行することによって、次の実質的化学量論的タンタル−窒化物層を形成する。また、本発明は、このように形成したタンタル−窒化物拡散バリア領域(108)も含む。一実施形態において、金属前駆物質は、五塩化タンタル(TaCl5)を含む。本発明は、低k材料とライナ材料との間に鮮鋭な界面を生成する。

(もっと読む)

改善された二重ダマシン集積構造およびその製造方法

ガスクラスターイオンビーム処理を用いた多孔質超低k値(ULK)絶縁体材料内に二重ダマシン構造を形成する方法に関して開示する。これらの方法においては二重ダマシンULK処理中におけるハードマスク層を最小にし、最終的なULK二重ダマシン構造内には、ハードマスク層が存在しない。ガスクラスターイオンビームのエッチング処理、緻密化処理、孔のシーリング処理、アッシング処理の各方法が記載されており、該方法は、材料の除去と同時にULKインターフェースの緻密化を進行させる。緻密なインターフェースとハードマスクがない新規なULK二重ダマシン構造が含まれている。 (もっと読む)

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

空隙を有する半導体デバイスの形成方法および該方法によって形成された構造

【課題】半導体デバイスの形成方法および該方法によって形成されたデバイスを提供すること。

【解決手段】第1の誘電材料(12a〜f)と第2の誘電材料(14a〜f)の互層を付着させる。ここで、第1の誘電材料と第2の誘電材料は異なる速度で選択的にエッチング可能である。誘電材料の互層内に第1のフィーチャ(22、24)を形成する。誘電材料の互層を選択的にエッチングして、第1の誘電材料を有するそれぞれの層内の第1の誘電材料の少なくとも一部分(26)を除去し、第2の誘電材料は本質的にエッチングされていないままにしておく。

(もっと読む)

付着材料を除去するための反応性流体システムおよびそれを使用するための方法

本発明は、一般に材料を処理するための方法に関する。より詳細には、本発明は反応性流体、および被覆材料、金属、非金属、層状材料、有機物、ポリマーおよび半導体材料を非限定的に含む付着材料を除去するための反応性流体の使用に関する。本発明は、半導体チップ生産のような商用プロセスに適用することが可能である。

(もっと読む)

(もっと読む)

半導体装置用のバックエンド工程伝送線路構造(バックエンド工程処理におけるサスペンデッド伝送線路構造の形成方法)

【課題】 半導体装置用のバックエンド工程伝送線路構造を提供する。

【解決手段】 半導体装置用の伝送線路構造(300)を形成する方法は、第1のメタライゼーション層上に層間絶縁膜を形成するステップと、前記層間絶縁膜の一部を除去するステップと、前記層間絶縁膜の一部の除去により生じた一つ以上のボイド(308)内に犠牲材を形成するステップとを含む。前記層間絶縁膜上に形成された第2のメタリゼーション層中に信号伝送線路(302)が形成され、該信号伝送線路(302)は前記犠牲材上に設けられている。前記第2のメタリゼーション層中に含まれる誘電体の一部が除去されて前記犠牲材が露出され、このとき該犠牲材の一部は前記信号伝送線路(302)を貫通して形成された複数のアクセスホール(310)を介して露出される。前記犠牲材は除去され、それにより前記信号伝送線路(302)の下部にエアギャップが形成される。

(もっと読む)

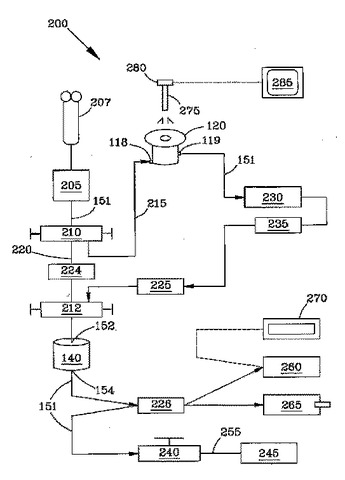

フルオロカーボン化学エッチングにおけるH2添加物を使用しての炭素ドープ酸化ケイ素エッチング

実施例はエッチング材料の供給(210)、水素を含む混合ガスの適用(230)、プラズマの発生(240)、エッチング材料のエッチング(250)を含むエッチング方法(200及び1600)を含む。エッチング材料は低k誘電性材料を含み得る。混合ガスは水素ガス、水素非含有フルオロカーボン、窒素ガスを含み得る。また、1つ以上のハイドロフルオロカーボンガス、不活性ガス、及び/又は一酸化炭素を含み得る。水素ガスとしては、H2、CH4、C2H4、NH3、及び/又はH2Oガスを含む、二原子水素、炭化水素、シラン、及び/又はフッ素非含有水素ガスであってもよい。水素非含有フルオロカーボンガスはCxFyガス(x≧1、y≧1)、ハイドロフルオロカーボンガスはCxHyFzガス(x≧1、y≧1、z≧1)であってもよい。混合ガスは酸素非含有であってもよい。実施例は減圧、低流量水素、1つ以上のプラズマ周波数を含み得る。

(もっと読む)

(もっと読む)

半導体デバイスにおけるレベル内またはレベル間誘電体としての超低誘電率材料を製造するための改良した方法およびこれによって作成される電子デバイス

【課題】 誘電率が低く、熱安定性を有する誘電材料を提供する。

【解決手段】 プラズマ化学気相成長(PECVD)プロセスを利用して、平行板化学気相成長プロセスにおいて、Si、C、O、およびH原子を含む熱的に安定した超低誘電率膜を製造するための方法を開示する。更に、この方法によって作成された熱的に安定した超低誘電率材料の絶縁層を含む電子デバイスを開示する。熱的に安定した超低誘電率膜の製造を可能とするため、例えばジエトキシメチルシラン(DEMS)のようなシラン誘導体、および、例えばビシクロヘプタジエンおよび酸化シクロペンテンのような有機分子等、特定の前駆物質材料を用いる。

(もっと読む)

感光性誘電体層を分解することによる相互接続構造の形成

本発明は、感光性材料の層が直接にパターン化される方法を提供する。その後、感光性材料は、少なくとも部分的に分解され、層内にボイドまたは空隙を残し、低減された抵抗キャパシタンス遅延特性を有する低誘電率の層を提供する。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

メモリセル形成のためのインサイチュ表面処理

有機メモリセルの製造中などに実施されうるものなど、導電層上にパッシブ層を形成するためのシステムおよび方法が開示され、これは、一般に、従来の無機メモリデバイスに固有の不具合を低減させる。パッシブ層は硫化銅(Cu2S)などの導電促進化合物を含み、これは、導電材料の上部から形成される。この導電材料はメモリセルにおいて下部電極として作用し、導電材料の上部が、フッ素(F)系ガスから生成されたプラズマによる処理によってパッシブ層に変換されうる。  (もっと読む)

(もっと読む)

低減された層内静電容量を有する集積回路の配線構造

【課題】

【解決手段】集積回路の配線構造を形成する方法が、誘電材料の層(13)内に複数のフィーチャ(16)を形成するステップと、フィーチャの側壁(16s)にスペーサ(20)を形成するステップとを含む。次に、スペーサによって側壁から分離された導体(25)をフィーチャ内に形成する。その後、スペーサを除去して側壁のところに空隙(40)を形成し、それによって導体が空隙によって側壁から分離されるようにする。導体の上下の誘電体層(42、12)は、導体間の誘電体の誘電率よりも低い誘電率を有する低k誘電体とすることができる。各導体(25)の断面は、低k誘電体層(12)と接触する底部と、他の低k誘電体(42)と接触する上部と、空隙(40)とのみ接触する側面とを有する。空隙は、層内静電容量を低減する機能を果たす。

(もっと読む)

エッチング残渣を除去するための水溶液

本発明は、エッチング残渣を除去するための改善された特性を有する新規溶液及び半導体製造におけるその使用に関する。本発明は、特に、半導体の製造プロセスの間にエッチング残渣及びパーティクルを除去しなければならないメタライジング部に対して及び表面に対して低いエッチング速度を有する水溶液に関する。 (もっと読む)

5,121 - 5,140 / 5,243

[ Back to top ]