Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

5,081 - 5,100 / 5,243

半導体装置の製造方法及び半導体装置

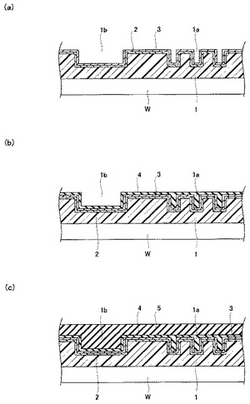

【課題】ダマシン配線に含まれる不純物の濃度を低下させて、配線中の欠陥を低減させる事が可能な半導体装置の製造方法を提供する。

【解決手段】ウェハW上の層間絶縁膜1に幅が0.3μm以下の細幅配線溝1a及び幅が0.3μmを超える太幅配線溝1bを形成する。層間絶縁膜1上にバリアメタル膜2及びシード膜3を形成する。その後、細幅配線溝1a全体に埋め込まれ、かつ太幅配線溝1bの一部に埋め込まれるように膜4を電解めっき法により形成する。太幅配線溝1bの他の部分に埋め込まれるように膜4よりも不純物濃度が低い膜5をスパッタ法により形成する。熱処理により膜4中の不純物を膜5中に拡散して、配線膜6を形成する。最後に層間絶縁膜1上の不要なバリアメタル膜2及び配線膜6を除去し、細幅配線と太幅配線を形成する。

(もっと読む)

半導体装置およびその製造方法

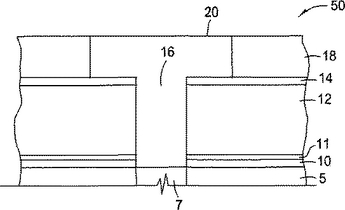

【課題】 セルフアライン形成技術によりセルフアライン形成領域の絶縁膜に形成されたコンタクトホールの径に比較してさらに開孔幅の大きな穴部を絶縁膜の上部に形成するためセルフアライン形成領域を再度エッチング処理する必要があったとしても、セルフアライン形成領域内のセルフアラインマスク膜に悪影響が及ぼされることなく、さらにセルフアライン形成領域に対して複数回に分けて接続配線を埋込み形成する必要をなくす。

【解決手段】 領域CB2に対して第1のコンタクトホール16を形成した後、フォトレジスト38、塗布型酸化膜39、フォトレジスト40の3層構造の多層レジスト構造41を形成し、第5のシリコン酸化膜23の上部に穴部24および25を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 多孔質絶縁膜を含む層間絶縁膜の誘電率を実効的に低減させ、微細で高信頼性のダマシン配線を有する半導体装置の実用化を容易にする。

【解決手段】 下層配線1上に多孔質の第1低誘電率膜2bを含む第1層間絶縁膜2が形成され、第1低誘電率膜2bに設けられたビアホール3の側壁に第1サイドウォールメタル4が形成され、その後に第1エッチングストッパー層2aがエッチングされて下層配線1が露出される。そして、ビアホール3内にビアプラグ5が埋め込まれる。同様に、多孔質の第2低誘電率膜6bを含む第2層間絶縁膜6のトレンチ7内の側壁に第2サイドウォールメタル8設けられた後に第2エッチングストッパー層6aがエッチングされ上記ビアプラグ5に接続する上層配線9が形成される。

(もっと読む)

配線形成方法及び配線形成装置

【課題】 基板表面に配線用の微細凹部を形成した後の一連の配線形成処理を、ドライ処理とウェット処理の混合した処理を経ることなく連続的に安定して行えるようにする。

【解決手段】 表面に堆積した絶縁膜62の内部に配線用の微細凹部64を形成した基板Wを用意し、この基板Wの表面にウェット処理によりバリア層68を形成し、このバリア層68の表面にウェット処理によりシード層70を形成し、このシード層形成後の基板の表面にウェット処理により配線層72を形成する。

(もっと読む)

耐酸化性が良好な次世代ダマシンバリヤ適用のための二層膜

基板を処理する方法であって、フェニル基を含む有機シリコン化合物を含む処理ガスを処理チャンバに供給するステップと、処理ガスを反応させて低k誘電物質によるダマシン又はデュアルダマシン適用においてバリヤ層として用いられる低kシリコンカーバイドバリヤ層を堆積させるステップとを含む、前記方法が提供される。低kシリコンカーバイドバリヤ層上に酸素を含まない有機シリコン化合物を含む処理ガスからのシリコン原子にフェニル基がほとんど結合されていないシリコンカーバイドキャップ層を堆積する方法が提供される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の更なる微細化に対応可能な、微細化されたコンタクトが確実に形成された素子特性に優れ、歩留まりの良い半導体装置、およびその製造方法を得る。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極を覆うエッチング保護膜を形成する工程と、前記エッチング保護膜を覆うように前記半導体基板上にバリアメタル層を形成する工程と、前記バリアメタル層上に導電性材料を堆積して導電性膜を形成する工程と、前記導電性膜上にレジストマスクを形成する工程と、前記レジストマスクをエッチングマスクとして前記導電性膜を選択的にエッチング除去してコンタクトを形成する工程と、前記レジストマスクを除去する工程と、前記半導体基板上における前記導電性膜がエッチング除去された領域に絶縁性材料を堆積して層間絶縁膜を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法,半導体装置、エッチング条件の設定方法、導電膜除去条件の設定方法、及びレチクル

【課題】 導電膜が正常にパターニングされて配線が形成されていることを、少ない労力で確認することができるようにする。

【解決手段】 層間絶縁膜8上に導電膜を形成する工程と、前記導電膜をパターニングすることにより、チップ領域1aに配線10a〜10cを形成すると共に、スクライブライン1b上に、複数のダミー配線31〜33を互いに平行に形成する工程と、複数のダミー配線31〜33相互間の抵抗値を測定する工程とを具備する。最外側に位置するダミー配線31,33それぞれに接続するパッド34,35を形成し、このパッド34,35に抵抗計の端子を接触させてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】 工程を複雑にすることなく実装の際の強度及び精度を向上させることが可能な半導体装置及びその製造方法を提供する。

【解決手段】 ダイシングラインDLに沿って半導体基板10の裏面に溝14を形成する。さらに半導体基板10の裏面からパッド電極11に到達するビアホール16を形成する。そして、ビアホール16内に埋め込み電極18を形成し、それと接続してダイシングラインDL近傍に延びる配線層19を形成する。配線層19の端部には導電端子21を形成する。そして、ダイシングラインDLに沿ったダイシングにより、裏面の端部に傾斜面1sを有した半導体装置1が完成する。半導体装置1がリフロー処理により回路基板30に接続される際、流動性の増した導電性ペーストが、導電端子21及び傾斜面1sを覆う。ここで、半導体装置1の外縁における回路基板30上には、サイドフィレットを含む導電性ペースト40a,40bが形成される。

(もっと読む)

半導体チップの製造方法および半導体装置の製造方法

【課題】 貫通電極用の貫通孔の形成時間を短縮化することで生産性を向上させた半導体チップの製造方法を提供する。

【解決手段】 まず、第1の絶縁膜3をマスク部材としてシリコン基板1の上面側に第1のトレンチ7aを例えばボッシュプロセスを用いて形成する。次に、第2の絶縁膜5をマスク部材としてシリコン基板1の裏面側に、第1のトレンチ7aに連通する第2のトレンチ7bを同じくボッシュプロセスを用いて形成する。そして、これにより形成された貫通孔8内に絶縁膜を形成した後、その貫通孔8内に導電性材料を充填して貫通電極2を形成する。

(もっと読む)

測定で求めた電気的特性に基づいて製造プロセスを制御するための方法および装置

本発明の方法は、動作レシピに従って半導体デバイスの構造を形成するプロセスを少なくとも1つ実行するステップを有する。この構造の電気的性能特性が測定される。測定で求めた電気的性能特性とその電気的性能特性の目標値とが比較される。この比較に基づいて、操作レシピの少なくとも1つのパラメータが決定される。システム(10,100)は、プロセス装置(30〜80,200,210,220,230)、計測装置(30〜80,250)およびコントローラ(140)を備える。プロセス装置(30〜80,200,210,220,230)は、操作レシピに従って半導体デバイスの構造を形成するプロセスを少なくとも1つ実行するように構成されている。計測装置(30〜80,250)は、構造の電気的性能特性を測定するように構成されている。コントローラ(140)は、測定で求めた電気的性能特性とその電気的性能特性の目標値とを比較して、この比較に基づいて操作レシピの少なくとも1つのパラメータを決定するように構成されている。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

半導体素子の製造方法

【課題】 シリコンを含むN型の導電領域と直接接続される導電パターンの形成時に、N型の導電領域と接続される部分のコンタクト抵抗の増大を防止し、バリア膜の厚さ増大に伴う導電パターンの寄生容量の増大を防止できる半導体素子の製造方法を提供すること。

【解決手段】 シリコンを含むN型の導電領域(207)にN型の不純物をドープして、N型の高濃度不純物拡散領域(212)を形成する工程と、CVD法を用いて高濃度不純物拡散領域(212)上にバリア用第1金属膜を蒸着し、高濃度不純物拡散領域(212)のシリコンと前記第1金属膜の金属とを反応させて、高濃度不純物拡散領域(212)と前記第1金属膜との間の界面に金属シリサイドを形成する工程、前記第1金属膜上に導電膜を形成する工程、及び、前記導電膜と前記第1金属膜とを選択的にエッチングして、導電パターンを形成する工程を含む。

(もっと読む)

金属薄膜および多層配線の形成方法ならびに薄膜基板

【課題】 集積度を維持しつつ、エレクトロマイグレーション耐性およびストレスマイグレーション耐性が優れ、高信頼性を有する金属薄膜および多層配線の形成方法ならびにそのような金属薄膜および多層配線を備えた薄膜基板を提供する。

【解決手段】 基板1上に金属薄膜3および熱エネルギーを吸収する熱吸収層4を形成し、熱吸収層4に対して第1のパルスレーザビームE1を照射することにより金属薄膜3に対して第1の加熱処理を施して再結晶化し、熱吸収層4を所定の形状にパターニングして基板全面に対してさらに第2のパルスレーザビームE2を照射することにより、金属薄膜3に対して高温領域および低温領域を有する選択的な温度分布で第2の加熱処理を施し、低温領域を核として、金属薄膜3を面内において熱吸収層4の形状に基づいた態様で再結晶化するようにしたので、粒界3重点が存在しにくい金属配線を形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】 工程を大幅に増加させずに導電層を形成しやすい形状のコンタクトホールの形成、特にウェットエッチング後にドライエッチングをより確実に行うことによってコンタクトホールの形状不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1上に形成されている層間絶縁膜2上に第1マスク3を形成する第1マスク形成工程と、層間絶縁膜2の途中までエッチングして第1凹部4aを形成する第1エッチング工程と、第1マスク3を除去する第1マスク除去工程と、第1エッチング工程により形成された第1凹部4a内に開口部を有するように第2マスク5を形成する第2マスク形成工程と、層間絶縁膜をシリコン基板1の表面に達するまでエッチングしてコンタクトホール4を形成する第2エッチング工程と、第2マスク5を除去する第2マスク除去工程とを有する。

(もっと読む)

シリコンゲルマニウム犠牲層を用いた半導体素子の微細パターンの形成方法及びそのパターンの形成方法を用いた自己整列コンタクトの形成方法

【課題】 シリコンゲルマニウム犠牲層を使用して半導体素子の微細パターンを形成する方法、及びそれを用いた自己整列コンタクトを形成する方法を提供する。

【解決手段】 基板上に導電性物質膜、ハードマスク膜及び側壁スペーサを含む導電ライン構造物を形成し、基板の全面に少なくとも導電ライン構造物の高さと同じであるか、またはそれ以上の高さにシリコンゲルマニウム(Si1−XGeX)犠牲層を形成し、犠牲層上にコンタクトホールを限定するフォトレジストパターンを形成した後、犠牲層を乾式エッチングすることで基板を露出させるコンタクトホールを形成し、ポリシリコンを使用してコンタクトホールを埋め込む複数のコンタクトを形成した後に残留する犠牲層を湿式エッチングした後、その領域にシリコン酸化物を満たして第1層間絶縁層を形成する半導体素子の自己整列コンタクトの形成方法。

(もっと読む)

貫通電極の形成方法、貫通電極および半導体装置

【課題】 工数や手間の増大を招くことなく、半導体基板の汚染を防止できる貫通電極の形成方法を提供すること。

【解決手段】 シリコン基板1に非貫通孔を形成し、この非貫通孔の底面からシリコン基板1に不純物を添加して、不純物添加部2を形成する。非貫通孔の側面および底面に表面側絶縁膜3を形成し、表面側絶縁膜3の内側に埋め込み電極4を形成する。シリコン基板1の裏面部分を除去して、不純物添加部2を裏面に露出させる。シリコンに対してエッチングレートが高いエッチングによって、不純物添加部2を、埋め込み電極4に対してセルフアライメントした状態で除去できる。

(もっと読む)

半導体装置の製造方法

【課題】 寄生容量の増加を抑制しつつ、所望のゲート耐圧を有するパワーMISFETを製造できる技術を提供する。

【解決手段】 基板上に多結晶シリコン膜を堆積し、その多結晶シリコン膜で溝部7、8を埋め込んだ後、その多結晶シリコン膜をパターニングすることにより、活性セル領域においては溝部7内にてゲート電極11を形成し、ゲート配線領域においては溝部8内を埋め込み、一部が溝部8内から連続して溝部8の外部に延在し、ゲート電極11と電気的に接続するゲート引き出し電極12を形成し、溝部8外のゲート引き出し電極12には、ゲート引き出し電極12の端部から延在するスリット14を形成する。その後、基板上に酸化シリコン膜19およびBPSG膜20を堆積する。

(もっと読む)

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 誘電体膜の段差被覆性がよく、かつ誘電体物質の廃棄量を少なくする。

【解決手段】 下地膜8上に、パターニングされた下部電極11を形成する工程と、インクジェット方式の塗布機構を用いて、下部電極11上に誘電体物質を塗布する工程と、塗布された誘電体物質を加熱することにより、下部電極11上に誘電体膜12を形成する工程と、誘電体膜12上に上部電極を形成する工程とを具備する。上部電極を形成する工程は、下地膜8上及び誘電体膜12上に層間絶縁膜を形成する工程と、層間絶縁膜に、誘電体膜上に位置する開口部を形成する工程と、開口部の中及び層間絶縁膜上に導電体を堆積する工程と、層間絶縁膜上から導電体を除去することにより上部電極を形成する工程とを具備する。

(もっと読む)

導電性電子部品およびその製造方法

導電構造(100)のある実施態様は、第1の導電層(110)および第2の導電層(120)を有する。第2の導電層は、第1の導電層のほぼ全長にわたり、第1の導電層に接触している。第2の導電層は第1の導電層の上方にある。非導電層(130)は、第1の導電層および第2の導電層に接触している。電流は第1の導電層および第2の導電層を通じて伝搬する。  (もっと読む)

(もっと読む)

5,081 - 5,100 / 5,243

[ Back to top ]