Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

5,141 - 5,160 / 5,243

低誘電率ナノ細孔性膜の多段階硬化

本発明に従った実施形態は、化学気相堆積された低誘電率材料の多段階硬化プロセスに関する。特定の実施形態では、電子ビーム放射および熱暴露ステップの組合せが、膜に組み込まれているポロゲンの選択的脱ガス化をコントロールするために採用されてもよく、ナノ細孔の形成をもたらす。一具体的な実施形態によると、シリコン含有成分と、不安定基を特徴付ける非シリコン含有成分との反応に起因する低誘電率層は、電子ビーム形態の放射印加が続く熱エネルギーの初期印加によって硬化されてもよい。 (もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

下にあるバリア層への多孔性低誘電率膜の接着を促進する手法

下にあるバリア層に対する多孔性低誘電率膜の接着は、その上にある多孔性低誘電率膜より炭素含量が低く、シリコン酸化物が豊富な中間層を形成することにより向上する。この接着層は、多数の手法のうち一つを単独で又は組み合わせて利用して形成されてもよい。一つのアプローチでは、接着層は、低誘電率材料の堆積直前にO2/CO2/などの濃酸化ガスを導入してSi前駆体を酸化することにより形成することができる。別のアプローチでは、α−テルピネン、シメン及びその他の酸素非含有有機物などの熱的に不安定な化学物質が、低誘電率膜の堆積前に除去される。また別のアプローチでは、ハードウェア又はシリコン非含有成分を導入する方式などの処理パラメータが変更されて、低誘電率膜の堆積の前に酸化物界面の形成を可能とすることもできる。さらに別のアプローチでは、吸収量、エネルギー又は熱アニール処理の使用などの電子ビーム処理のパラメータが制御され、バリアと低誘電率膜との間の界面で炭素種を除去することもできる。さらなるアプローチでは、低誘電率堆積の前に前処理プラズマが導入されバリア界面の加熱を増進することにより、低誘電率堆積ガスが導入され、低誘電率膜が堆積される時、薄い酸化物界面を形成することもできる。 (もっと読む)

高度に選択的な酸化ケイ素エッチング組成物

少なくとも一種のカルボン酸からなる溶媒中に溶解した少なくとも一種の酸性フッ化物供給源化合物の生成物を含有し、更に約(0.5)〜約(3)溶液重量%のフッ化水素酸と約(1)〜約(5)溶液重量%の水とを含む酸化ケイ素エッチング溶液であって、ここで酸性フッ化物供給源化合物の総濃度は、溶媒1キログラム当たり約(1.25)〜約(5.0)モルである、前記酸化ケイ素エッチング溶液。金属表面から酸化ケイ素と金属のケイ酸塩とを選択的に除去する方法も開示する。 (もっと読む)

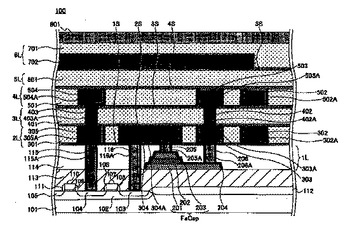

多層配線構造

【課題】 導電性のパターンを配置することができない領域があっても、CMP後の表面の平坦度を高めることが可能な多層配線構造を提供する。

【解決手段】 支持基板(20)の表面に、第1の領域(10)、該第1の領域を取り囲む環状の第2の領域(11)、及び該第2の領域を取り囲む第3の領域(12)が画定されている。支持基板の上に第1の配線層(M8L)が配置されている。第1の配線層の第3の領域内に配線が形成され、第2の領域内にダミーパターンが形成され、第1の領域内には導電パターンが形成されていない。第1の配線層の上であって、かつ第1の領域内に機能素子(1)が配置されている。

(もっと読む)

プラズマ加工システムによる基板エッチング法

プラズマ加工システムで基板をエッチングする方法を提供する。基板は、半導体層、その半導体層上方に提供された第1バリアー層、その第1バリアー層上方に提供された低k層、その低k層上方に提供された第3ハードマスク層、その第3ハードマスク層上方に提供された第2ハードマスク層、及びその第2ハードマスク層上方に提供された第1ハードマスク層を有する。方法には、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対して低選択度を有するが、第2ハードマスク層の第2ハードマスク材料に対しては高選択度を有する第1エチャントと、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対しては高選択度を有する第2エチャントとで基板を交互にエッチングするステップが含まれ、第1エチャントは第2ハードマスク層の第2ハードマスク材料に対して低選択度を有する。  (もっと読む)

(もっと読む)

応力緩和部を備えた電子装置

本発明は、基板と基板上に配される回路部を含む構成本体を有する電子装置に関する。一実施例は、少なくとも1つの応力緩和エレメント(4)と、上面及び側壁を有する基板(1)と、この基板(1)上に配される少なくとも1つの回路部(2)と、基板(1)上に配される少なくとも1つのパッシベーション層(3)とを含み、アイソレート層(3)は、少なくとも1つの回路部(2)及び/又は基板(1)を被覆し、頂面と基板の側壁に向けて配される少なくとも1つの外部側面とその頂面及び少なくとも1つの外部側面により形成される少なくとも1つの外部エッジとを含み、少なくとも1つの応力緩和エレメント(4)は、延性材料により形成され、パッシベーション層(3)上で、延性材料が基板(1)の上面と接触する。  (もっと読む)

(もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

炭素含有アンチヒューズ材料を使用した再プログラム可能な金属−金属間のアンチヒューズ

金属−金属間のアンチヒューズが集積回路内の2つの金属相互接続層の間に配置される。下側のバリア層はTiから形成される。下側の付着力促進層は下側のTiバリア層の上に配置される。アモルファス炭素、および、水素およびフッ素の少なくとも1つによりドープされたアモルファス炭素のうち少なくとも1つを有するグループから選択されたアンチヒューズ材料層が、下側の付着力促進層上に配置される。上側の付着力促進層がアンチヒューズ材料層の上に配置される。上側のTiバリア層が上側の付着力促進層の上に配置される。  (もっと読む)

(もっと読む)

半導体装置

本発明は、ボンディングパッドで発生する応力に対する強度を向上させることが可能な半導体装置を提供することを目的とする。本発明に係る半導体装置においては、半導体チップ上にボンディングパッド(1)が複数個設けられる。それぞれのボンディングパッド(1)においては、最上層の配線層を用いて形成された第1メタル(11)の下に、ライン状の第2メタル(12)が複数個設けられる。そして、上記目的を達成するために、ボンディングパッド(1)は、第2メタル(12)の長手方向に並べて配設される。つまり、第2メタル(12)の長手方向(L1)と、ボンディングパッド(1)の配列方向(L2)とが同じ方向になるように、ボンディングパッド(1)を並べて配設する。 (もっと読む)

半導体部品のための配線を組立てる方法

一面において、本発明は半導体部品のための配線を組立てる方法を含む。半導体基板が用意され、そして基板を貫通して全体に延びる開口(212)が形成される。約200℃以下の温度において開口の側壁(218)に沿って第一の材料(220)が堆積される。堆積は原子層堆積法と化学蒸着法のうちの一つまたは両方を含むことができ、そして第一の材料は金属窒化物を含むことができる。第一の材料の表面の上にソルダー湿潤材料(224)が形成される。ソルダー湿潤材料は、例えばニッケルを含むことができる。次いで、開口の中およびソルダー湿潤材料の上にソルダー(240)が設けられる。 (もっと読む)

成膜方法、SiO2膜、電子部品および電子機器

【課題】所定パターンのSiO2膜を容易かつ安価に形成し得る成膜方法、かかる成膜方法により形成されたSiO2膜、このSiO2膜を備える電子部品および電子機器を提供すること。

【解決手段】本発明の成膜方法は、所定パターンの第2の層間絶縁層(SiO2膜)5を形成する方法であり、主としてポリオルガノシロキサンで構成されるポリオルガノシロキサン膜を形成する第1の工程と、ポリオルガノシロキサン膜の前記所定パターンに対応する領域に、第1のSiO2化処理を施して、前記領域に存在するポリオルガノシロキサンをSiO2に変化させる第2の工程と、SiO2に変化した前記領域をアルカリ溶液により除去する第3の工程と、第3の工程において残存するポリオルガノシロキサン膜に、第2のSiO2化処理を施して、ポリオルガノシロキサンをSiO2に変化させることにより、第2の層間絶縁層5を得る第4の工程とを有する。

(もっと読む)

マイクロ波伝送線路

【課題】シリコン基板を信号伝播媒体とするマイクロ波伝送線路を長期安定性を維持しながら伝送損失の劣化を防止できるようにする。

【解決手段】高抵抗シリコンからなる基板1の主面上には、酸化シリコンからなる保護膜2、酸化アルミニウムからなる電位中和膜3及びストリップメタル4が順次形成されている。保護膜2は正の空間電荷を持ち、電位中和膜3は負の空間電荷を持ち、信号電界が基板1と保護膜2と電位中和とを伝播し、保護膜2及び電位中和膜3の各膜厚は、基板1の表面近傍における電位が中和されるように調整されている。

(もっと読む)

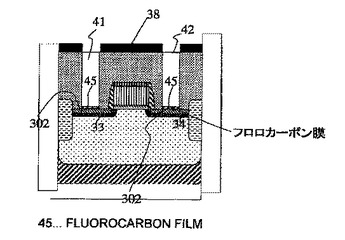

半導体装置の製造方法および絶縁膜のエッチング方法

コンタクトホールのエッチングにおいて、エッチングの途中においてイオン照射のエネルギーだけでなく、ガス組成を変化させ、高速エッチングから低速エッチングに切り替え、ダメージを低減させる。低速エッチングでは、ガス組成をも変化させることにより、コンタクトホール底部に、強固なフロロカーボン膜を形成し、シリコン表面を保護した状態でエッチングすることができる。このため、シリコンにドープされた不純物の不活性化を防止できる。  (もっと読む)

(もっと読む)

アモルファスカーボン膜を含む構造およびその形成方法。

【課題】 アモルファスカーボン膜を有する構造およびその形成方法を提供することである。

【解決手段】 半導体デバイスは、半導体基板と、半導体基板上に形成され、被処理膜を有する膜スタックとを含む。膜スタックに含まれるデュアルハードマスクは、アモルファスカーボン層、およびアモルファスカーボン層と被処理膜との間に配置される下層のハードマスク層を有し、ハードマスク層は、アモルファスカーボン層を含まない。金属配線のためのダマシン構造は、膜スタックに形成されている。アモルファスカーボン膜は、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。アモルファスカーボン膜は、配線構造を形成するためのリソグラフィマスクの一部として役に立つことができ、または、それは、CMPの間、デュアルハードマスク、ケミカルメカニカルポリシング(CMP)ストップ層または犠牲層の上部層として役立つことになる。

(もっと読む)

低KのCVD材料の勾配堆積

【課題】 全体として低いkをもつILDを提供し、ILDに内在する接着性の欠陥に対する抵抗性だけでなく、ILDと基板との間の良好な接着性を提供する構造体と方法を提供すること。

【解決手段】 全般的に低い誘電率、半導体基板への良好な接着、及び熱循環によるクラッキングへの良好な抵抗性を有する、半導体デバイスのための誘電体層(12)である。誘電体層(12)は、誘電率の勾配をもつ誘電体層を提供するために、誘電体材料の堆積条件の連続的変化を含むプロセスによって生成される。

(もっと読む)

PMD層の限定された熱履歴の形成

基板上に持ち上がった隣接特徴部により画成されたギャップを充填する方法は、基板を収容するチャンバにシリコン含有プロセスガス流を供給するステップと、上記チャンバに酸化プロセスガス流を供給するステップと、上記チャンバに燐含有プロセスガス流を供給するステップとを備えている。また、この方法は、シリコン含有プロセスガスと、燐含有プロセスガスと、酸化プロセスガスとの間に反応を生じさせることにより、Pドープの酸化シリコン膜の第1部分を実質的な適合層としてギャップに堆積するステップも備えている。適合層の堆積は、(シリコン含有プロセスガス+燐含有プロセスガス):(酸化プロセスガス)の比を時間と共に変化させる段階と、適合層の堆積全体にわたり基板の温度を約500℃未満に維持する段階とを含む。また、この方法は、Pドープの酸化シリコン膜の第2部分をバルク層として堆積するステップも備えている。上記膜の第2部分の堆積は、(シリコン含有プロセスガス+燐含有プロセスガス):(酸化プロセスガス)の比をバルク層の堆積全体にわたり実質的に一定に維持する段階と、バルク層の堆積全体にわたり基板の温度を約500℃未満に維持する段階とを含む。 (もっと読む)

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

配線構造の形成方法及び半導体装置

下層配線(101)と不図示の上層配線とを接続するためのビア孔(102)を絶縁膜(103)にエッチングストッパー膜(104)及びハードマスク(105)を用いて形成した後、本発明の1ステップの低パワー・バイアス・スパッタ法によりビア孔(102)の内壁を覆うように絶縁膜(103)上にTaからなる下地膜(106)を形成する。ここで、ビア孔(102)の内壁面から絶縁膜(103)上にわたって薄く均一な膜厚の下地膜(106)が得られる。このように、比較的簡素な工程により、配線形成上の不都合を生ぜしめることなく、開口の内壁面、即ち側壁面から底面にかけて薄く均一に下地膜を成膜することを可能とし、信頼性の高い極微細な配線構造を実現する。

(もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法

本発明では、水素またはH2Oの拡散を防止することで強誘電体キャパシタの劣化を防止し、高品質の強誘電体キャパシタを有する半導体装置を提供することを課題とする。そのため、本発明では、基板上に形成された強誘電体キャパシタと、前記強誘電体キャパシタ上に形成された配線構造とを有する半導体装置であって、前

記配線構造は、層間絶縁層と当該層間絶縁層中に形成されたCu配線部を含み、前記層間絶縁層に面するように、水素拡散防止層を含むエッチングストッパー層が形成されていることを特徴とする半導体装置を用いた。  (もっと読む)

(もっと読む)

5,141 - 5,160 / 5,243

[ Back to top ]