Fターム[5F033RR20]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 組成比 (158)

Fターム[5F033RR20]に分類される特許

141 - 158 / 158

配線構造およびその製造方法

半導体素子が形成された基板上に金属配線を積層し、半導体素子の接続を得る多層配線構造において、多孔質絶縁膜内に微細な金属配線を形成する場合に、リーク電流が発生し隣接する配線間の絶縁性が損なわれたり、隣接する配線間の絶縁耐性が劣化することのない配線構造およびその製造方法を提供する。半導体素子が形成された基板上の金属配線構造において、層間絶縁膜と金属配線との間に、有機物を含む絶縁性バリア層413を形成する。この絶縁性バリア層は隣接する配線間のリーク電流を低減し、絶縁信頼性を向上させることができる。  (もっと読む)

(もっと読む)

半導体デバイスのためのARC層

半導体デバイスの製造において使用される反射防止膜(ARC)の層(201)。ARC層は底部を有し、同底部は、底部上に配置されたARC層の部分と比較して低いケイ素含有率を有する。ARC層は金属層(107)上に形成される。ARC層の比較的低いケイ素含有率は、金属層/ARC層の界面における望ましくないシリサイドの形成を抑制する。ARC層の頂部は、ARC層の中間部と比較して低いケイ素含有率を有し、頂部の比較的低いケイ素含有率は、ARC層上のフォトレジスト層の汚染を抑制し得る。ケイ素含有率は、蒸着工程中、ケイ素含有ガスの流量に対して窒素含有ガスの流量を減少、又は増大させることによって増大または減少させ得る。  (もっと読む)

(もっと読む)

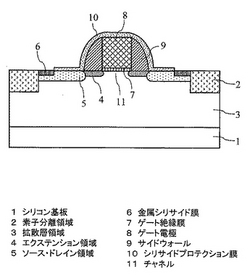

半導体装置およびその製造方法

【課題】 半導体措置で発生した熱を放熱しやすくすることによってESD耐圧に優れた半導体装置およびその製造方法を提供する。

【解決手段】 拡散層領域3に形成されたチャネル11の上には、ゲート絶縁膜7を介してゲート電極8が設けられている。また、ゲート電極8の側壁部には、サイドウォール9が形成されている。そして、ゲート電極8上とソース・ドレイン領域5上の一部とに、ゲート電極8およびサイドウォール9を被覆するようにしてシリサイドプロテクション膜10が形成されている。シリサイドプロテクション膜10が設けられていないソース・ドレイン領域の上には、シリサイドプロテクション膜10に隣接して金属シリサイド膜6が形成されている。ここで、シリサイドプロテクション膜10は、SiC膜およびSiOC膜の少なくとも一方からなるものとする。

(もっと読む)

半導体装置

【課題】 HDP−CVDなどにより層間絶縁膜を形成するに際に発生する水素イオンを除去し、デバイスへの水素イオンの影響を解消する。

【解決手段】 ゲート電極を形成した半導体基板上に、コンタクト層と、金属配線と、層間絶縁膜とを備える半導体装置であって、層間絶縁膜は、水素原子を含む原料ガスを用いて、バイアス印加したプラズマCVDにより金属配線上に形成し、金属配線および層間絶縁膜の下層にシリコン酸窒化膜を有することを特徴とする。

(もっと読む)

絶縁膜の加工方法

【課題】SiOCHの組成からなる材料で形成された層間絶縁膜に、アスペクト比の高い凹部を形成する際、凹部の加工初期から加工終期にかけてOラジカル量に対してCF系ラジカル量が過剰になることが防止された絶縁膜の加工方法を提供する。

【解決手段】CF系ラジカルをエッチング種として用いたドライエッチングにより、基板11上に設けられた層間絶縁膜16に、同一のエッチング条件下で接続孔18を形成する絶縁膜の加工方法において、層間絶縁膜16の表面側に向かってO含有率が高くなるように層間絶縁膜16の膜質を膜厚方向に変化させることで、ドライエッチングの進行により接続孔18のアスペクト比が高くなるのにともない、エッチング底面へのCF系ラジカルの入射量が減少するのに合わせて、層間絶縁膜16から放出されるOラジカル量を減少させることを特徴とする絶縁膜の加工方法である。

(もっと読む)

アルミノシリケート前駆体から形成された低いkの誘電体の層

アルミノシリケート前駆体で、高い機械的な強度の、低いkの、層間の誘電体の材料を、アルミニウムがその材料のケイ素の基材の中へ手軽に組み込まれるように、形成するための方法、及び、そのように形成された一つ又はより多くの高い強度、低いkの層間の誘電体の層を含む集積回路デバイス。

(もっと読む)

(もっと読む)

薄膜保護膜及びこれを有する表示基板

【課題】 安定的な垂直構造を有する保護膜を形成することでピクセルの作動不良を防止した薄膜保護膜の提供、及びこれを有する表示基板を提供する。

【解決手段】 基板に形成された薄膜の上面に形成され該薄膜を保護する保護膜において、前記保護膜は、前記薄膜と直接コンタクトされエッチングエージェント(etching agent)によって第1エッチング率を有する第1保護膜と、前記第1保護膜の上面に形成され前記エッチングエージェントに対して第1エッチング率より高いエッチング率である第2エッチング率を有する第2保護膜とを有する。

(もっと読む)

半導体装置

【課題】銅配線から絶縁膜へのCuイオンの電界拡散を抑制させること。

【解決手段】第1の銅導体33と、第1の銅導体より低い電位にある第2の導体30と、第1の銅導体33と第2の導体30との間に位置する第1の絶縁膜31と、第1の銅導体33と第1の絶縁膜31との間に、膜厚と抵抗率が第1の絶縁膜31よりも小さな第2の絶縁膜32を備えた半導体装置を提供する。第2の絶縁膜32の抵抗率は、第1の絶縁膜31の抵抗率の1/10以下であることが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、安定した処理が可能で、且つゲートショートしない、ダマシンゲート構造を有する半導体装置の製造方法を提供することを目的としている。

【解決手段】 本発明は、エッチングストッパー膜に用いたシリコン窒化膜を触媒CVD(Catalytic−CVD)法により、基板温度250〜400℃、触媒体温度1600〜2000℃で成膜する。これによって、シリコン窒化膜中の水素・塩素などの不純物を低減し、HF系のウェットエッチレートを熱酸化膜の1/4以下に抑えることにより、ゲート溝上部に露出したエッチングストッパー膜表面のエッチング量を抑えることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 導電層に至るホールが、アライメントのずれに起因して、下側の層間絶縁膜まで到達してしまうことが防止された半導体装置およびその製造方法を提供する。

【解決手段】 層間絶縁膜1の上にエッチングストッパ膜2が形成される。エッチングストッパ膜2の上に導電層3が形成される。導電層3を覆うようにエッチングストッパ膜4が形成される。エッチングストッパ膜4の上には層間絶縁膜5が形成される。前述の構造においては、まず、第1のエッチング条件で、層間絶縁膜5を上下に貫通し、エッチングストッパ膜4の表面を露出させるホールが形成される。その後、第2のエッチング条件で、そのホールの底面を構成するエッチングストッパ膜4が除去され、導電層3に至るホールが形成される。ホールに接続配線8が埋め込まれる。

(もっと読む)

半導体装置およびその作製方法

【課題】 本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大

させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極

等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】 本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミ

ニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3

層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域へ

の拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗

値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、そ

の第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、

配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

半導体装置、その製造方法、及び電子機器

【課題】製造工程を増加させることなく、エッチング工程においてコンタクトホールを形成するに際し、第1酸化膜と第2酸化膜との界面に切込み部が形成されず、コンタクトホールに形成される配線の断線を有効に回避することができるようにする。

【解決手段】第1酸化膜5と、この第1酸化膜5上に成膜された第2酸化膜8とを有する半導体装置において、第2酸化膜8が少なくともボロンを含む酸化シリコン膜であり、第2酸化膜8の第1酸化膜5との界面に形成される界面層8aのボロン濃度が高く設定されている。界面層8aのボロン濃度を高く設定することで、ウエットエッチングレートが遅くなり、両酸化膜5,8の界面に切込み部が形成されることが防止される。

(もっと読む)

粘性前駆物質を用いた化学気相堆積による機能的に段階的な誘電体層の堆積方法

下にある層上に段階的な誘電体層を形成する方法であって、シリコン-炭素含有ガスと酸素含有ガスとキャリヤガスの混合物を阻止板と面板を備えたシャワーヘッドに流して、段階的な誘電体層の酸化物を多く含む部分を形成するステップであって、シリコン-炭素含有ガスが初期流量を持つ前記ステップと、シリコン-炭素含有ガスを第1中間流量で約0.5秒以上流すステップであって、第1中間流量が初期流量より大きい前記ステップと、シリコン-炭素含有ガスを第1中間流量より大きい最大流量で流して、段階的な誘電体層の炭素を多く含む部分を形成するステップと、を含む前記方法。 (もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線の狭ピッチ化に対応可能な半導体装置およびその製造方法を得る。

【解決手段】半導体基板上に複数の第1配線層を形成する工程と、第1配線層を覆うように第1層間絶縁膜層9を形成する工程と、第1層間絶縁膜層に、表面からその厚み方向に貫いて第1配線層に接続する複数の第1プラグ14を形成する工程と、第1層間絶縁層上であって、第1プラグのうち一部の第1プラグの直上部に第2配線層40を形成する工程と、第1層間絶縁膜層上に第2配線層を覆うように第2層間絶縁膜層19を形成する工程と、第2層間絶縁膜層に、表面からその厚み方向に貫いて第2配線層に接続する第2プラグ24’と、表面からその厚み方向に貫いて第1プラグに直接接続する第3プラグ24と、を同時に形成する工程と、第2層間絶縁膜層上であって、第2プラグおよび第3プラグの直上部に第3配線層50を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

ドープ窒化膜、ドープ酸化膜、およびその他のドープ膜

【課題】一般に、半導体デバイスの製造に使用される被膜、特に窒化被膜および酸化被膜を提供すること。

【解決手段】窒化シリコン、酸化シリコン、酸窒化シリコン、または炭化シリコン被膜の形成中、少なくとも1つの非シリコン前駆体(ゲルマニウム前駆体や炭素前駆体など)を添加することによって、堆積速度が改善され、または被膜の応力を調整するなどこの被膜の特性を調整することが可能になり、あるいはその両方が可能になる。また、ドープ型酸化シリコンまたはドープ型窒化シリコンまたはその他のドープ型構造では、ドーパントが存在することを利用して、このドーパントに関連する信号(目印)をエッチング・ストップとして測定することができ、またはその他の場合にはエッチング中の制御を実現することができる。

(もっと読む)

炭素含有アンチヒューズ材料を使用した再プログラム可能な金属−金属間のアンチヒューズ

金属−金属間のアンチヒューズが集積回路内の2つの金属相互接続層の間に配置される。下側のバリア層はTiから形成される。下側の付着力促進層は下側のTiバリア層の上に配置される。アモルファス炭素、および、水素およびフッ素の少なくとも1つによりドープされたアモルファス炭素のうち少なくとも1つを有するグループから選択されたアンチヒューズ材料層が、下側の付着力促進層上に配置される。上側の付着力促進層がアンチヒューズ材料層の上に配置される。上側のTiバリア層が上側の付着力促進層の上に配置される。  (もっと読む)

(もっと読む)

低KのCVD材料の勾配堆積

【課題】 全体として低いkをもつILDを提供し、ILDに内在する接着性の欠陥に対する抵抗性だけでなく、ILDと基板との間の良好な接着性を提供する構造体と方法を提供すること。

【解決手段】 全般的に低い誘電率、半導体基板への良好な接着、及び熱循環によるクラッキングへの良好な抵抗性を有する、半導体デバイスのための誘電体層(12)である。誘電体層(12)は、誘電率の勾配をもつ誘電体層を提供するために、誘電体材料の堆積条件の連続的変化を含むプロセスによって生成される。

(もっと読む)

141 - 158 / 158

[ Back to top ]