Fターム[5F033RR20]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 組成比 (158)

Fターム[5F033RR20]に分類される特許

21 - 40 / 158

低誘電率誘電体を含む超小型電子構造およびその構造内の炭素分配を制御する方法

本発明の実施形態は、超小型電子構造の形成に関する。32nmの次のテクノロジーノード向けの低誘電率誘電体材料は、約2.6未満の誘電率を呈する必要がある。本発明により、全体として超小型電子構造の曲げおよび剪断強度の完全性を向上させながら、そのような低誘電率誘電体材料を使用する半導体デバイスを形成することが可能になる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線が形成される多孔質絶縁膜がプラズマダメージ等を受けるのを防ぐことにより、高歩留り且つ高信頼性な半導体装置を得られるようにする。

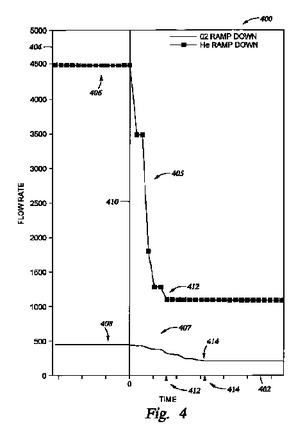

【解決手段】半導体基板の上に、化学気相成長法により、炭素濃度、空孔形成剤濃度及び酸素濃度がそれぞれ異なる複数の領域を有する空孔形成剤含有膜を形成する工程を備えている。この工程は、前駆体、空孔形成剤及び酸化剤を第1の流量で流す第1の期間と、第1の期間の後に、前駆体の流量に対する空孔形成剤の流量を減少させる第2の期間と、第2の期間の後に、前駆体の流量に対する空孔形成剤の流量の減少を停止し、前駆体、空孔形成剤及び酸化剤を第2の流量で流す第3の期間と、第3の期間の後に、前駆体の流量に対する酸化剤の流量を増大させる第4の期間と、第4の期間の後に、前駆体、空孔形成剤及び酸化剤を第3の流量で流す第5の期間とを含む。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

半導体装置の製造方法

【課題】配線構造を形成する際に、ウェハ面内の配線溝の深さのばらつきを抑え、均一加工を実現する。

【解決手段】高炭素濃度絶縁膜114と、炭素を含まないまたは炭素濃度が低い低炭素濃度絶縁膜116との積層構造にドライエッチングで配線溝を形成する際、CHF系ガスを添加した第1のエッチングガスを用いた第1のエッチング条件で低炭素濃度絶縁膜116に配線溝を形成し、当該配線溝底部に高炭素濃度絶縁膜114を露出させる。第1のエッチング条件の第1のエッチングガス中のCHF系ガスの分圧は、第1のエッチングガスに当該CHF系ガスを添加していない場合の各膜へのエッチングレートを基準として、当該CHF系ガスを添加することにより、高炭素濃度絶縁膜114に対するエッチングレートが低下するとともに、低炭素濃度絶縁膜116に対するエッチングレートを変化させない範囲に設定されている。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置の製造方法

【課題】配線からのCuの拡散を防止する。

【解決手段】例えば、UDC拡散バリア膜22、ポーラスシリカ膜23、UDCミドルストッパ膜24、ポーラスシリカ膜25およびUDC拡散バリア膜26の積層構造にビア溝27aと配線溝27bを形成したときに、内部に露出するUDC拡散バリア膜22、UDCミドルストッパ膜24、UDC拡散バリア膜26の表面に対し、水素プラズマを照射する。これにより、各SiC膜の露出表面をSiリッチにする。そして、プラズマ照射後のビア溝27aと配線溝27bにTa膜28を形成し、Cuで埋め込む。Ta膜28と接触することとなるSiC膜の表面をあらかじめSiリッチな状態にしておくことにより、Ta膜28をCuの突き抜けが抑えられるような結晶構造に制御することが可能になる。これにより、配線からのCuの拡散を防止することが可能になる。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

固体撮像装置およびその製造方法

【課題】本発明は、固体撮像装置に含まれる配線層間の絶縁膜の平坦性の向上に有利な技術を提供することを目的とする。

【解決手段】半導体基板上に、第1の配線層の導電パターンと、当該導電パターンの上部を覆う絶縁性を有する第1の研磨停止層とを形成する第1の形成工程と、第1の研磨停止層が形成された半導体基板上に層間絶縁層を形成する工程と、層間絶縁層の上に、半導体基板の少なくとも受光領域を覆うように絶縁性を有する第2の研磨停止層を形成する第2の形成工程と、導電パターンの上部を覆う第1の研磨停止層が少なくとも露出し、且つ受光領域を覆う第2の研磨停止層の少なくとも表面が研磨されるまで、第2の研磨停止層が形成された半導体基板の上側表面を平坦化するように研磨する研磨工程と、研磨された半導体基板に、第2の配線層の導電パターンを形成する工程とを含むことを特徴とする固体撮像装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線絶縁膜としてSiOCH膜を用いる場合に、ビアホールの開口径に依らず、その加工制御性を十分に得て、下層Cu配線の表面の組成のバラツキを十分に抑制する。

【解決手段】下層Cu配線3上に形成されている積層構造20は、シリコンと炭素を含有するキャップ絶縁膜4と、キャップ絶縁膜4上に形成されている配線絶縁膜5としてのSiOCH膜を有する。積層構造20にビアホール8、9を形成する工程は、第1及び第2ドライエッチングを組み合わせて行う。第1ドライエッチングでは開口径が小さいビアホール9のエッチングレートが、開口径が大きいビアホール8のエッチングレートよりも大きくなるようにO2濃度が設定された第1混合ガスを用いる。第2ドライエッチングではビアホール8のエッチングレートがビアホール9のエッチングレートよりも大きくなるようにO2濃度が設定された第2混合ガスを用いる。

(もっと読む)

多層配線の形成方法

【課題】 工程数の増加がなく、しかも銅を使用している配線にダメージが及ぶ可能性も少ない多層配線の形成方法を提供すること。

【解決手段】 銅を使用している下層配線3上にエッチングストップ層5を形成し、エッチングストップ層5上に層間絶縁膜6を形成し、層間絶縁膜6にエッチングストップ層5に達する開孔7を形成し。層間絶縁膜6上に酸化マンガン膜8を形成し、酸化マンガン膜8を開孔7から露呈した層間絶縁膜6の表面に残しながら、下層配線3上に形成されたエッチングストップ層5を除去し、開孔7の底に下層配線3を露呈させ、開孔7の底に露呈した下層配線3上に、上層配線を形成する。

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】自己整合的にバリア膜を形成する配線構造の信頼性を向上できるようにする。

【解決手段】半導体基板の上に酸素及び炭素を含む層間絶縁膜11を形成し、該層間絶縁膜11に溝部13を形成し、溝部13の底面上及び側壁上に所定の第1の金属元素及び第2の金属元素を含む補助膜14を形成し、熱処理を行い、銅を主成分とする配線本体層19を、溝部13の内部を埋め込むように形成する。熱処理を行うことにより、補助膜14中の第1の金属元素を補助膜14と対向する層間絶縁膜11に拡散させ、溝部13の底面及び側壁における層間絶縁膜11の上において、第1の金属元素と層間絶縁膜11の酸素元素との化合物を主成分とする第1のバリア膜15を形成させた後、補助膜14中の第2の金属元素が補助膜14と対向する層間絶縁膜11に拡散させ、第2の金属元素と層間絶縁膜11の炭素元素との化合物を主成分とする第2のバリア膜17を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

MOS型半導体装置

【目的】耐放射線特性の改善と高耐圧化が図れるMOS型半導体装置を提供する。

【解決手段】LOCOS膜18上に窒化膜18を形成し、窒化膜14上にPBSG膜10を形成する。窒化膜14の屈折率を2.0〜2.1とし、膜厚を0.1μm〜0.5μmとすることで半絶縁性薄膜にする。γ線でLOCOS膜18内に発生した電子―正孔対のうち移動度が小さい正孔31を窒化膜14を通してソース電極12に逃がし、LOCOS膜18にできる正の固定電荷33の蓄積量を抑制する。このように3層構造とすることで耐放射線特性の改善と高耐圧化が図れる。

(もっと読む)

21 - 40 / 158

[ Back to top ]