Fターム[5F033RR20]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 組成比 (158)

Fターム[5F033RR20]に分類される特許

41 - 60 / 158

半導体装置及びその製造方法

【課題】配線遅延の増大を防止すると共に、配線信頼性の低下を抑制する。

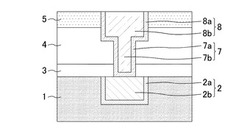

【解決手段】半導体装置は、基板の上に形成され、第1の配線2を有する第1の絶縁膜1と、第1の絶縁膜1及び第1の配線2の上に形成された第2の絶縁膜3と、第2の絶縁膜3の上に形成された第3の絶縁膜4とを有している。第2の絶縁膜3は、空孔を含んでいる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながら、高いドレイン電流を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたソース電極5s、ドレイン電極5d及びゲート電極5gと、が設けられている。更に、ソース電極5sとゲート電極5gとの間の化合物半導体積層構造2上に形成され、シリコンを含む第1の保護膜6と、ドレイン電極5dとゲート電極5gと間の化合物半導体積層構造2上に形成され、第1の保護膜6より多くシリコンを含む第2の保護膜7と、が設けられている。

(もっと読む)

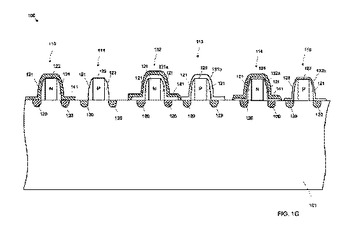

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

固体撮像装置およびその製造方法、および撮像装置

【課題】本発明は、オフセットスペーサを形成するときのシリコン基板へのエッチングダメージを防止して、画素トランジスタのノイズ発生、光電変換部の白点の発生を抑制することを可能にする。

【解決手段】半導体基板11に、光電変換部21と画素トランジスタを有する画素部12と、周辺回路部と、ロジック回路部14を有する固体撮像装置の製造方法は、半導体基板11上に、第1ゲート絶縁膜31N,31Pを介して形成したロジック回路部14のトランジスタの第1ゲート電極32N,32Pと、第2ゲート絶縁膜51を介して形成した画素部12および周辺回路部のトランジスタの第2ゲート電極52を被覆し、さらに光電変換部21を被覆する第1絶縁膜71を形成した後、光電変換部21、画素部12および周辺回路部をマスク83で被覆した状態で第1絶縁膜71をエッチバックして第1ゲート電極32N,32Pの側壁にオフセットスペーサ33を形成する。

(もっと読む)

多層膜の形成方法及び表示パネルの製造方法

【課題】予め定めた形状にパターニングされた導電層の上下に配置されている絶縁層のそれぞれにコンタクトホールを形成し、これらコンタクトホールを介して互いに異なる層として形成された2つの導電層を互いに電気的に接続する場合であっても、導電不良が生じ難い多層膜の形成方法及び表示パネルの製造方法を提供する。

【解決手段】基板2上に成膜された第1導電層40上に第1絶縁層20を成膜し、前記第1絶縁層20上に第2導電層41を成膜し、前記成膜した第2導電層41をパターニングし、パターニングされた前記第2導電層41を覆うように前記基板2上に第2絶縁層25を成膜し、前記第2絶縁層25上に該第2絶縁層25よりもエッチング速度が速い第3絶縁層26を成膜し、前記第1絶縁層20、前記第2絶縁層25及び前記第3絶縁層26に対して前記第1導電層40の少なくとも一部を露出させるコンタクトホールを一括形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】チャネル形成領域にSiOxを含む酸化物半導体層を用い、電気抵抗値の低い金属材料からなるソース電極層及びドレイン電極層とのコンタクト抵抗を低減するため、ソース電極層及びドレイン電極層と上記SiOxを含む酸化物半導体層との間にソース領域またはドレイン領域を設ける。ソース領域またはドレイン領域は、SiOxを含まない酸化物半導体層または酸窒化物膜を用いる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線間の容量の増加が抑制された半導体装置およびその製造方法を実現する。

【解決手段】本実施形態における半導体装置10は、半導体基板100と、半導体基板100上に形成された層間絶縁膜110(第一の層間絶縁膜)と、層間絶縁膜110上に形成された、層間絶縁膜110よりも誘電率が低い層間絶縁膜120(第二の層間絶縁膜)と、層間絶縁膜120を貫通し、底部が層間絶縁膜110に入り込んでいるCu配線141と、を備えている。Cu配線141は、下方に向かって幅が狭くなる形状を有しており、層間絶縁膜120におけるCu配線141の側面の傾斜よりも、層間絶縁膜110におけるCu配線141の側面の傾斜が大きくなっている。

(もっと読む)

半導体装置、その半導体装置の作製方法及びその半導体装置を有する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタにおいて、電界効果移動度を向上させることを課題の一とする。また、薄膜トランジスタの電界効果移動度を向上させても、オフ電流の増大を抑制することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とゲート絶縁層の間に、該酸化物半導体層より導電率が高い酸化物クラスターを形成することによって、該薄膜トランジスタの電界効果移動度を向上させ、且つオフ電流の増大を抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】比誘電率の低い層間絶縁膜を用いた半導体装置において、プラズマ処理時の層間絶縁膜へのダメージを軽減でき、ダメージ層を除去する際に形成されるアンダーカットを抑制する。

【解決手段】基板上に比誘電率の低い材料からなる絶縁膜4を形成する。次に、前記絶縁膜上にチャンバ内でSiOCH膜5を形成し、前記チャンバ内にプラズマを発生させた状態で徐々に膜中のカーボン濃度を減らし、前記SiOCH膜上に連続的にSiO2膜6を形成する。前記SiOCH膜と前記SiO2膜をハードマスクに用いて前記絶縁膜をプラズマ処理し、前記絶縁膜に溝7,8を形成する。その後、前記絶縁膜に形成した溝のエッチング表面をウェットエッチングし、プラズマ処理によるダメージ層と加工残渣物を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

半導体装置の製造方法

【課題】パターンの高さおよび間隔に応じた最適な膜厚で層間絶縁膜を形成することにより、製造工程数を増加させることなく層間絶縁膜の平坦度を向上させることができる半導体装置の製造方法を提供すること。

【解決手段】基板1上に形成された所定形状のパターン2におけるパターン間隔Sとパターン高さhの縦横比K=S/hに応じて、基板1上に形成すべき層間絶縁膜3の最適膜厚Tを算出し、パターン2を覆うように最適膜厚Tで層間絶縁膜3を基板1上に形成する層間絶縁膜形成工程と、基板1上の層間絶縁膜3を熱処理してリフロー平坦化する平坦化工程とを含むことを特徴とする半導体装置の製造方法。

(もっと読む)

金属層間誘電体による拡散防止バリヤ層を有する集積回路およびその製造方法。

【課題】ライン間キャパシタンスを減少できる構造を有する集積回路および不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止できる集積回路の製造方法を提供する。

【解決手段】低誘電率材料中での不純物の移動を防止できるキャップ層あるいはバリヤ層により、不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止する。集積回路は第一の誘電体層と集積回路のより上層の導電層間に拡散防止バリヤ層を堆積して製造される。拡散防止バリヤ層はその次の金属層で不純物を含む誘電体層へその場で形成され、さらに、研磨を含む処理が多層誘電体構造に対してなされる。キャップ層あるいはバリヤ層にその場堆積は不純物を含む層を雰囲気にさらすのを防止し、そしてキャップ層あるいはバリヤ層により、水分、水素あるいはそのたのものにより、層が汚染されるのを防止することができる。

(もっと読む)

フォトセンサ及び表示装置

【課題】マトリクス状に配置した光電変換素子が捉える光の強度分布を、再現よく電気信号に変換して取り出せる大型のエリアセンサおよび、エリアセンサを搭載した書き込み速度が速く、表示ムラが少ない表示装置を提供する。

【解決手段】インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタは、大面積基板にマトリクス状に配置することが容易であり、また特性にバラツキが少ない。インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタで構成した特性にバラツキが少ない増幅回路と表示素子の駆動回路を用いて、マトリクス状に配置したフォトダイオードが捉える光の強度分布を再現よく電気信号に変換して取り出し、マトリクス状に配置した表示素子をムラなく駆動する。

(もっと読む)

銅配線、半導体装置および銅配線形成方法

【課題】拡散バリア層と銅配線本体との密着性を大幅に改善することができるようにする。

【解決手段】この発明は、絶縁層に銅からなる配線本体を備えてなる銅配線において、上記絶縁層と、上記絶縁層に対向して設けられた拡散バリア層と、上記拡散バリア層上に形成された、銅(Cu)からなる配線本体と、を備え、上記拡散バリア層は、マンガン(Mn)に対する酸素(O)の組成比率(比率y/x)を2未満とするマンガン酸化物(組成式:MnxOy(比率y/x<2))を含むマンガン酸化物層を有する、ことを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】ボラジン系化合物の絶縁膜を用いて、絶縁材料と配線材料との間の密着性や、機械強度等の特性が向上された半導体装置およびその製造方法を提供する。

【解決手段】凹部に第1の導体層が埋め込まれた第1の絶縁層と、第1の絶縁層上に形成されたエッチングストッパー層と、エッチングストッパー層上に形成された第2の絶縁層と、第2の絶縁層上に形成された第3の絶縁層と、第2の絶縁層と第3の絶縁層との凹部に埋め込まれた第2の導体層と、を含む半導体装置であって、第2の絶縁層および第3の絶縁層は、炭素含有ボラジン化合物を原料として化学的気相反応成長法によって形成され、第3の絶縁層の炭素含有率が、第2の絶縁層の炭素含有率よりも小さく、第2の導体層の外周に、金属材料で構成された導体拡散防止層が形成されている半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁信頼性の劣化を低減し、銅配線の信頼性を改善する。

【解決手段】本発明の半導体装置は、半導体基板10と、シリコン(Si)と炭素(C)と酸素(O)とを含み、半導体基板10に形成された第一の多孔質絶縁膜11a及び第二の多孔質絶縁膜11bと、第一の多孔質絶縁膜11a中に埋め込まれた第一の銅配線12aと、第二の多孔質絶縁膜11b中に、それぞれ、埋め込まれた第二の銅配線12b及び銅ビア22と、第二の銅配線12a上に形成された第一のメタルキャップ膜13aと、第二の銅配線12b上に形成された第二のメタルキャップ膜13bと、を有する。第一、第二の多孔質絶縁膜11a、11bは、少なくとも上層のC/Si比が1.5以上であり、かつ、第一、第二の多孔質絶縁膜11a、11bの少なくとも上層に含有される空孔の最大径が1.3nm以下である。

(もっと読む)

低誘電率膜の堆積処理方法、基板処理システム、デュアルダマシン構造の形成方法、およびデュアルダマシン構造

【課題】集積回路製造工程において、ガスを化学的に反応させて化学気相成長又はCVDにより、低誘電率膜の堆積処理方法を提供する。

【解決手段】約10Wから約200Wの一定RFパワーレベルか、または約20Wから約500WのパルスRFパワーレベルで、1以上のシリコン化合物と酸化ガスからなるプロセスガスから、パターン化された金属層上にコンフォーマルライニング層を堆積する工程と、前記ライニング層上にギャップ充填層を堆積させる工程とを含む低誘電率膜の堆積処理方法。

【効果】シリコン酸化物は、配線間の静電結合を弱めて、1つの堆積チャンバで高信頼性のデュアルダマシン構造を製造する集積プロセスにおいてさらに有効である。

(もっと読む)

銅配線、銅配線の形成方法および半導体装置

【課題】銅配線本体の開放表面に形成されるマンガンを含むバリア層に最適な内部構成を持たせて、そのバリア機能を充分に発揮させることができる半導体素子の製造方法を提供する。

【解決手段】銅配線1は、電気絶縁層3に銅からなる配線本体8を備える。配線本体の外周81は、電気絶縁層に対向している第1の外周8aと電気絶縁層との間に形成された第1のバリア層7aと、配線本体の外周のうち電気絶縁層に対向していない第2の外周8bに接して形成された第2のバリア層7bとを備える。第1および第2のバリア層はそれぞれマンガンを含む酸化物層からなるとともに、各バリア層内の厚さ方向でマンガンの原子濃度が極大となる位置を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造に使用されるシリコン酸化膜の下地依存性を改善することによって、シリコン酸化膜の狭スペースへの埋め込み性やモフォロジーを向上させる。

【解決手段】半導体素子部を有するSi基板1の表面に有機基を含まないSi含有分子を吸着させ、Si含有分子による吸着層12を形成する。あるいは、Si基板1上にSiリッチなSiN系保護膜を形成する。吸着層12またはSiリッチなSiN系保護膜上から有機シリコン材料ガスとオゾン等の活性化された酸素を含むガスとを供給し、Si基板1上にシリコン酸化物からなる絶縁膜13を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低誘電率膜を用いた層間絶縁膜SiOCH膜をCMPプロセスにおけるダメージから保護しつつ、配線間層間絶縁膜SiOCH膜の実効誘電率を低減する。

【解決手段】半導体装置100は、SiOCH膜10の表層が改質されることにより形成された、SiOCH膜10よりも炭素濃度が低くかつSiOCH膜10よりも酸素濃度が高い表面改質層20が設けられるとともに、Cu配線50の表面及び表面改質層20の表面に接するキャップ絶縁膜60を有している。このため、SiOCH膜10全体の誘電率の上昇を低減しつつ、CMPプロセスにおいて親水性の表面改質層20が露出することによって水滴が残りにくくなり、CMPプロセス後のパーティクルの残留やウォーターマークの発生を低減できる。

(もっと読む)

41 - 60 / 158

[ Back to top ]