Fターム[5F033RR20]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 組成比 (158)

Fターム[5F033RR20]に分類される特許

101 - 120 / 158

半導体装置の多層金属配線の形成方法

【課題】金属スペーサを用いて金属配線の特性向上及びオーバラップマージンを改善できる多層金属配線の形成方法を提供する。

【解決手段】下層上に第1金属配線を形成する段階、前記第1金属配線を含む下層上に第1絶縁膜を形成する段階、前記第1絶縁膜をエッチングして前記第1金属配線の高さより低いように段差を形成する段階、前記第1絶縁膜上の第1金属配線の側壁に金属スペーサを形成する段階、前記金属スペーサを含む下層上に平坦化膜を形成する段階、前記平坦化膜をエッチングして前記第1金属配線が露出するようにコンタクト孔を形成する段階、及び、前記コンタクト孔を介して第1金属配線とコンタクトする第2金属配線を形成する段階を備えることを特徴とする。

(もっと読む)

アレイ基板、これを有する表示装置及びその製造方法

【課題】配線抵抗及び不良が減少したアレイ基板を提供する。

【解決手段】絶縁基板120上にバリア層を形成する。その後、バリア層上に銅または銅合金を含むゲートライン131及びゲートラインに電気的に接続されるゲート電極118を形成する。その後、ゲートライン131及びゲート電極118の表面を窒化プラズマ処理する。続いて、絶縁基板120上にゲートライン131及びゲート電極118をカバーするゲート絶縁膜126を蒸着する。続いて、ゲート絶縁膜126上にデータライン133、データライン133に電気的に接続されるソース電極117、ソース電極117と離隔されて配置されるドレイン電極119、及びゲート電極118上でソース電極117とドレイン電極119との間に配置される半導体パターンを形成する。

(もっと読む)

液晶表示装置、液晶表示装置を具備した電子機器

【課題】入力信号のHレベルとLレベルとを同時にレベルシフトすることができ、且つ低コストで製造できるレベルシフタ、及びレベルシフタを具備する表示装置を提供することを目的とする。

【解決手段】単一の導電型のトランジスタで構成されたオフセット回路を用いて、入力信号をオフセットする。そして、オフセットされた入力信号をオフセット回路と同じ導電型のトランジスタで構成された論理回路に供給することによって、入力信号のHレベルとLレベルとを同時にレベルシフトすることができる。また、オフセット回路と論理回路は単一の導電型のトランジスタで構成されているため、表示装置を低コストで製造することができる。

(もっと読む)

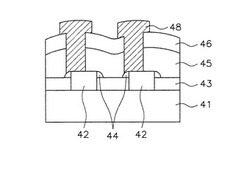

コンタクトスペーサを有するコンタクト構造を具備した半導体素子及びその製造方法

【課題】上部金属配線層と下部コンタクトパッドとの接続においてコンタクトパッドをエッチング工程から保護する半導体素子の製造方法を提供する。

【解決手段】半導体基板の上に絶縁層65を形成し、前記絶縁層はその内部に導電性パッド67を具備する段階と、前記絶縁層と導電性パッド上に誘電層72を形成する段階と、前記誘電層の一領域をエッチングして前記導電性パッドと重畳するコンタクトホール72aを形成し、前記コンタクトホールは前記導電性パッドの上部コーナーを露出させる段階と、前記コンタクトホール内に前記導電性パッドの上部コーナーを覆うエッチング防止層75を形成する段階により製造する。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、半導体基板の主表面側の下地領域 350に形成された凹部351内全体にシリコン窒化膜352を形成する工程と、前記シリコン窒化膜352を酸化して該シリコン窒化膜352をシリコン酸化膜353に変換することにより、前記凹部内全体に絶縁領域を形成する工程とを有することを特徴とする。

(もっと読む)

半導体装置及び当該半導体装置を具備するIDラベル、IDタグ、IDカード

【課題】RFIDを有する半導体装置において、駆動電源のための電池の経時的劣化に伴う電池の残存容量の確認や電池の交換作業をすることなく、個体情報を送受信することができ、且つ駆動するための電源を外部からの電磁波の電力が十分でない場合であっても良好な個体情報の送受信状態を維持するRFIDを有する半導体装置を提供することを課題とする。

【解決手段】信号処理回路と、信号処理回路に接続された第1のアンテナ回路及び第2のアンテナ回路と、信号処理回路に接続されたバッテリーとを設け、第1のアンテナ回路は、信号処理回路に記憶されたデータを送信するための信号を送受信するものであり、第2のアンテナ回路は、バッテリーに充電するための信号を受信するものであり、第1のアンテナ回路が受信する信号と第2のアンテナ回路が受信する信号の波長が異なる構成とする。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板の主表面側に形成された凹部を有する下地領域と、前記下地領域の凹部内全体に埋め込まれた塩素を含有するシリコン酸化膜とを有することを特徴とする。

(もっと読む)

ストレッサを有する半導体デバイスおよびその製造方法

Nチャネル(113、115)およびPチャネル(111)トランジスタが、引張ストレッサ層(128)および圧縮ストレッサ層(126)をそれぞれ付加することによって、拡張される。2つのストレッサ層について、これまで知られていなかった問題が見つかった。ストレッサ層は、両方とも好都合なことに窒化物であっても良いが、ある程度別の仕方で作製される。2つのストレッサはエッチ・レートが異なる。そのため、2つのストレッサ間の界面においてコンタクト・ホールをエッチングするときに有害な影響が出る。ゲートに対するコンタクトは、Nチャネル・トランジスタとPチャネル・トランジスタとの間の中間であることが好ましい場合が多い。これは一見したところ、2つのストレッサ層間の境界に対して最良の箇所でもある。境界においてコンタクト・エッチングを行なう結果、その下にあるゲート構造またはコンタクト・ホール内の残留窒化物に穴を開ける可能性がある。したがって各コンタクト(154)が確実に、コンタクトが通っているストレッサと反対のタイプのストレッサから少なくとも何らかの所定の距離に位置することが有用であることが分かっている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 多孔質有機シロキサン膜を層間絶縁膜として用いた半導体装置の製造方法において、フォトレジスト膜をマスクにして多孔質有機シロキサン膜をパタン加工した後、多孔質有機シロキサン膜を劣化させずに、かつ簡便にフォトレジスト膜を除去する。

【解決手段】 炭素量/シリコン量が0.3以上0.7以下で比誘電率が2.4以上2.6以下或いは炭素量/シリコン量が0.4以上0.6以下で比誘電率が2.2以上2.6以下の多孔質有機シロキサン膜を製膜し、その上方にパタンを有するフォトレジスト膜を成膜し、これをマスクとして多孔質有機シロキサン膜をドライエッチング加工し、しかる後にアミン系剥離液でフォトレジスト膜を除去する。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、n型領域を有するシリコン基板の上に、窒素を含む酸化シリコンを用いたゲート絶縁膜と、ホウ素を含むシリコンを用いたゲート電極とを形成する工程と、ゲート電極両側の前記シリコン基板内にp型ソース/ドレイン領域を形成する工程と、ゲート電極の側壁上に酸化シリコンを用いてサイドウォールスペーサを形成する工程と、ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜を形成する工程と、層間絶縁膜の平坦化された表面から内部に向って凹部を形成し,該凹部内に下地のバリア層とその上の銅領域を含む銅配線とを埋め込む工程と、銅配線の上に炭化シリコン層を形成する工程と、 前記炭化シリコン層の上方に絶縁層をCVDで形成する工程と、を含むことを特徴とする。

(もっと読む)

イメージセンサの金属配線形成方法

【課題】金属配線の熱安定性を確保し、イメージセンサの暗電流特性を改善させるためのイメージセンサの金属配線形成方法を提供すること。

【解決手段】半導体基板上にコンタクトプラグを備える第1の層間絶縁膜を形成するステップと、該第1の層間絶縁膜上に拡散防止膜を形成するステップと、フォーミングガスアニールを行うステップと、前記拡散防止膜上に第2の層間絶縁膜を形成するステップと、該第2の層間絶縁膜及び拡散防止膜を選択的にエッチングしてトレンチを形成するステップと、該トレンチを埋め込むまで導電物質層を形成するステップと、該導電物質層を平坦化してコンタクトプラグと電気的に接続する金属配線を形成するステップとを含み、上記した本発明は、 金属配線を形成する工程の前に拡散防止膜を形成した後、アニール処理を行って金属配線の熱安定性を確保し、イメージセンサの暗電流特性を改善させて金属配線の信頼性及び素子の信頼性を向上させるという効果がある。

(もっと読む)

LowK誘電絶縁体及び半導体回路構造の形成方法

【課題】半導体製造用に改善された誘電体及び機械的特性を有する絶縁体材料を供する。

【解決手段】材料は酸素、シリコン及び水素を含み、2g/ccより小さい密度を特徴とする。あるいは多孔質絶縁体材料は633nmないし673nmの波長の光に対する1.45より小さい屈折率又は45GPaより小さいヤングモジュラスを特徴とする。半導体デバイスの作製方法は、デバイス形成のための上部表面を有する半導体層を供すること及び半導体層上に複数のレベルの相互接続を形成し、各レベルは複数の部分を含むことを含む。部分は少なくともいくつかの部分間に多孔質層を形成するため、TEOSを分解することにより、他の部分から電気的に分離される。

(もっと読む)

表示装置及びその作製方法

【課題】表示装置において、低抵抗材料を配線に用いることが望まれてきたが、これまでは、有効な配線形成の手段が存在しなかった。

【解決手段】第1の導電膜を形成し、第1の導電膜上に選択的にレジストを形成し、第1の導電膜及びレジスト上に第2の導電膜を形成し、レジストを除去すると共にレジスト上に形成された第2の導電膜を除去し、第1の導電膜上に形成された第2の導電膜を覆うように第3の導電膜を形成し、第1の導電膜及び第3の導電膜を選択的にエッチングし、複数の配線及び電極を形成する。これにより、大型パネルに低抵抗材料を用いた配線を形成することができるため、信号遅延等の問題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】比誘電率の低い層と銅拡散を防止する比誘電率が高い層を有しつつも、層間に十分な密着強度を持つ半導体装置をおよびその製造方法を提供する。

【解決手段】多層構造を有する半導体装置において、第1の絶縁層13と、第1の絶縁層に接する第2の絶縁層12と、第1の絶縁層とは反対側で第2の絶縁層に接する第3の絶縁層11とを含み、第2の絶縁層は、第1の絶縁層と接する第1の界面では第1の絶縁層と同じ組成をし、第3の絶縁層と接する第2の界面では第3の絶縁層と同じ組成をし、第2の絶縁層は第1の界面から第2の界面までの間で組成が連続的に変化している。

(もっと読む)

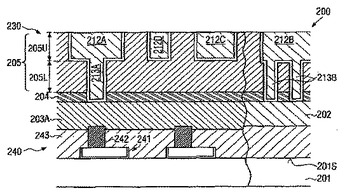

ダミービアの供給によりメタライゼーション層の密着性を向上させる技術

電気的に機能しない金属領域(212B、312B)の下方にダミービア(213B、313B)を供給することにより、後続のプロセスにおいて、金属が層間剥離する危険性が著しく低下する。更に、一実施形態では、形成されるメタライゼーション層(330)の機械的強度は、機能しないオーバーレイ金属領域(312B)のアンカーとしての役割を果たすダミー金属領域(303B)を供給することでさらに一層強化される。加えて、ダミービア(213B、313B)はさらに、電気的に機能する金属領域(212A、212C、212D、312A)と、領域(220A、320A)とともに供給され、これにより、機械的安定性とその電気的パフォーマンスも強化される。  (もっと読む)

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、液晶表示装置およびそれらの製造方法

【課題】パッシベーションおよびゲート絶縁膜のエッチング時の形状制御を可能とし、導電層の段切れを防止可能とし、品質を向上させた薄膜トランジスタ、これを用いた液晶表示装置およびその製造方法を提供する。

【解決手段】 絶縁基板1上にゲート層2、ゲート絶縁膜3、半導体層4、ドレイン層5、パッシベーション層60を設け、かつ前記パッシベーション層60上に配置された導電層7がコンタクトホールを介して前記ゲート層2若しくは前記ドレイン層5と接続される薄膜トランジスタにおいて、前記パッシベーション層60が、表面側を高速エッチングレート層62、基板側を低速エッチングレート層61の2層以上で形成され、かつ前記高速エッチングレート層62の膜厚を前記導電層7の膜厚以下とする。

(もっと読む)

引張応力を有するシリコン酸窒化膜を形成する方法

引張応力を有する緻密化されたシリコン酸窒化膜を形成する方法、及び緻密化されたシリコン酸窒化膜を含む半導体デバイスが開示される。緻密化されたシリコン酸窒化膜は、LPCVDプロセスにて基板上に多孔質SiNC:H膜を堆積すること、及びSiNC:H膜に酸素を混入し、それにより、多孔質SiNC:H膜より高い密度を有する緻密化されたSiONC:H膜を形成するために、多孔質SiNC:H膜を酸素含有ガスに曝すことによって形成されることができる。緻密化されたシリコン酸窒化膜は、半導体デバイスを含んだ基板上に含められ得る。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 不揮発性メモリ素子のデトラップ・リテンション特性の劣化を防止することができる技術を提供する。

【解決手段】 プラグ16を形成した絶縁膜14上にシリコンリッチな酸化膜よりなる層間絶縁膜17およびTEOS膜よりなる層間絶縁膜18を形成する。そして、層間絶縁膜17および層間絶縁膜18を貫通する溝19を設け、この溝19内へ埋め込むように配線20aを形成する。すなわち、第1配線層を層間絶縁膜17および層間絶縁膜18に埋め込んだ埋め込み配線とする。さらに、第1配線層を構成する配線20a〜20cと同層の層間絶縁膜17として水や水素などの不純物を捕獲する性質を有するシリコンリッチな酸化膜とする。

(もっと読む)

積層体およびその形成方法、絶縁膜、ならびに半導体装置

【課題】 低い比誘電率を有し、かつ、有機系膜と無機系膜との密着性に優れた積層体およびその形成方法、絶縁膜、ならびに半導体装置を提供する。

【解決手段】 積層体の形成方法は、基材の上に、無機系膜のための第1の塗膜を形成し、前記第1の塗膜の表面に対して、紫外線照射処理、電子線照射処理、およびプラズマ処理から選ばれる少なくとも1種の処理を行ない、前記処理後の前記第1の塗膜の上に、反応性シラン化合物および有機溶媒を含む密着促進用組成物を塗布した後、有機系膜のための第2の塗膜を連続的に形成することにより、積層膜を形成し、前記積層膜を硬化すること、を含む。前記反応性シラン化合物は、(Ri)nSi(Xj)4−n,i=1〜n,n=1〜3,j=1〜4−n,で表される化合物の群から選ばれた少なくとも1種のシラン化合物。

(もっと読む)

酸化膜埋め込み構造、酸化膜埋め込み方法、半導体装置および半導体装置の製造方法

【課題】本発明は、RFバイアスを増大させること無く、かつ経済的・実用的な方法により、ボイドの無い絶縁膜(酸化膜)を所定の凹部に形成することができる酸化膜の埋め込み構造等を提供することを目的とする。

【解決手段】第一の発明によると、酸化膜埋め込み構造は、凹部(溝4)を有する下地(シリコン基板1)と、当該凹部に形成される酸化膜(シリコン酸化膜6)とを、備えている。ここで、当該酸化膜は、少なくとも一部にシリコンリッチのシリコン酸化膜領域を含んでいる。

(もっと読む)

101 - 120 / 158

[ Back to top ]