Fターム[5F033TT00]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088)

Fターム[5F033TT00]の下位に属するFターム

Fターム[5F033TT00]に分類される特許

21 - 40 / 66

半導体装置の製造方法

【課題】半導体装置の製造過程において生じるウエハ外周部分からのパーティクルの発生を防止し、十分な歩留りを実現する。

【解決手段】ウエハにゲート電極となる導電膜4、5を形成する第一工程と、導電膜4、5の中の、ウエハの外周部分に形成された導電膜4、5の上に選択的に保護膜7を形成する第二工程と、導電膜4、5の上に第一レジストパターンを形成し、前記第一レジストパターンをマスクとして導電膜4、5をエッチングすることにより、ゲート電極を形成する第三工程と、前記ゲート電極を覆う層間絶縁膜を形成する第四工程と、前記層間絶縁膜の上に第二レジストパターンを形成し、前記第二レジストパターンをマスクとして前記層間絶縁膜をエッチングすることにより、コンタクトホールを形成する第五工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体ウエハ上に形成された第1の保護膜上にポリイミド系樹脂等からなる第2の保護膜を形成するとき、半導体ウエハが反りにくいようにする。

【解決手段】 所定の相隣接する2本の配線7の接続パッド部7b間に形成された5本の引き回し線部7cおよびその両側における相隣接する2つの接続パッド部7bの周辺部を含む第1の保護膜5の上面に、スクリーン印刷法やインクジェット法等により、ポリイミド系樹脂等からなる第2の保護膜10を形成する。この場合、当該5本の引き回し線部7cの互いに平行とされた部分がエレクトロマイグレーションに起因するショートが発生しやすい領域であるので、この領域のみを第2の保護膜10で覆えば、当該領域でエレクトロマイグレーションに起因するショートが発生しにくいようにすることができる。この結果、第2の保護膜10の形成領域を可及的に小さくすることができ、これにより半導体ウエハ21が反りにくいようにすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、半導体基板が樹脂層により被覆されない構造のため、半導体基板端部が欠け易い問題があった。

【解決手段】本発明の半導体装置1では、シリコン基板2上面に配線層13が形成され、配線層13を被覆するように樹脂層14が形成される。配線層13上には樹脂層14の開口領域15を介してバンプ電極18が形成される。また、保護シート19は、シリコン基板2の裏面及びシリコン基板2の側面20の一部を被覆する。この構造により、シリコン基板2の裏面側では、保護シート19が緩衝材として機能し、シリコン基板2のチッピングが防止される。

(もっと読む)

半導体素子及びその製造方法

【課題】回路基板に確実に実装可能で、且つ、加熱に起因して発生する応力が抑制可能な半導体素子を提供する。

【解決手段】半導体素子10において、複数の電極パッド13の上方に、中央部Aより中間部Bで、更に中間部Bより端部Cで膜厚が厚くなるように形成した絶縁部材15を設ける。各電極パッド13に接続するアンダーバンプメタル17は、それぞれ絶縁部材15から突出させ、その先端にそれぞれバンプ18を形成する。

(もっと読む)

半導体装置

【課題】応力集中に対して内部電極が断線、剥離しにくい半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11を厚み方向に貫通して設けられた貫通電極17と、半導体基板11の表面の貫通電極17が到達する部分に設けられ、貫通電極17と電気的に接続された内部電極12と、内部電極12の一部を除外して半導体基板11の表面を覆う第一の保護膜13Aと、内部電極12の第一の保護膜13Aで覆われない部分に、第一の保護膜13Aと離間して設けられた第二の保護膜13Bと、半導体基板11の裏面に設けられ、貫通電極17と電気的に接続された金属配線18とを備える。

(もっと読む)

チップ・パッケージ相互作用安定性を高めるための応力緩和ギャップを含む半導体デバイス。

【解決手段】

単一チップ区域を個々のサブ区域(1つ以上の応力緩和領域280a、280bに基く200a、200b、200c)に分割することによって、サブ区域の各々内に熱的に誘起される応力は、複雑な集積回路の動作の間に低減することができ、それにより低k誘電体材質又はULK材質を備えた複雑なメタライゼーションシステムの全体的な信頼性を高めることができる。その結果、従来の戦略と比較して、多数の積層メタライゼーション層を半導体チップ(200)の大きな横方向寸法との組み合わせにおいて用いることができる。

(もっと読む)

ウェハ貫通ビアおよびこれを作成する方法

【課題】 ウェハ貫通ビアおよびこれを作成する方法を提供する。

【解決手段】 ウェハ貫通ビア構造である。この構造は、上面(105)および反対側の底面(320)を有する半導体基板(100)と、少なくとも1つの導電性ウェハ貫通ビア(130)および少なくとも1つの非導電性ウェハ貫通ビア(125)を含むウェハ貫通ビアのアレイであって、ウェハ貫通ビアのアレイの各ウェハ貫通ビアが基板(100)の上面(105)から基板(100)の底面(320)への中間点を越えたところと全域との間まで延びている、ウェハ貫通ビアのアレイとを含む。また、このウェハ貫通ビア構造を製作するための方法である。

(もっと読む)

半導体装置及びその製造方法

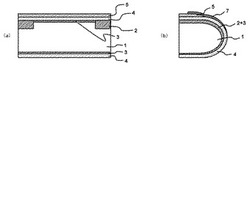

【課題】レーザ照射により切断されるヒューズを備えた半導体装置において、レーザの反射率の増加を抑えてヒューズへ加わるエネルギーの低下を抑制することにより、ヒューズの飛散を防止できるようにする。

【解決手段】絶縁膜1上に、密着層2a、メタル層3a及びTiN反射防止膜4aから構成されるヒューズ11が形成されている。ヒューズ11を覆うように絶縁膜1上にシリコン酸化膜5が形成されている。シリコン酸化膜5上にシリコン窒化膜8が形成されている。ヒューズ11上に位置するシリコン酸化膜5aにおけるヒューズ11の短辺方向の断面は三角形状を有している。

(もっと読む)

半導体装置の製造方法

【課題】導電性プラグの上に低誘電率絶縁膜を堆積させる場合、低誘電率絶縁膜の膜厚均一性の悪化による配線のオープン不良もしくはショート不良の発生を抑え、また低誘電率絶縁膜の機械強度や密着性の低下による信頼性の低下を抑えることを目的とする。

【解決手段】半導体装置の製造方法は、半導体基板の上に、第1の絶縁膜を形成する工程(a)と、工程(a)の後に、第1の絶縁膜を貫通する導電性プラグを形成する工程(b)と、工程(b)の後に、導電性プラグの上面に保護膜を形成する工程(c)と、工程(c)の後に、第1の絶縁膜の上および保護膜の上に第2の絶縁膜を形成する工程(d)と、工程(d)の後に、保護膜の上面に達するように第2の絶縁膜を貫通する配線溝を形成する工程(e)と、工程(e)の後に、保護膜を除去する工程(f)と、工程(f)の後に、配線溝内に配線を形成する工程(g)とを備えている。

(もっと読む)

半導体装置の製造方法

【目的】膜切れの無い均一なシード膜を形成する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S102)と、絶縁膜に開口部を形成する工程(S104)と、開口部内に光触媒膜を形成する工程(S110)と、Cuを含有する溶液に光触媒膜を浸漬させた状態で光触媒膜に紫外線を照射する工程(S112)と、開口部内に電解めっき法によりCuを埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間に設けられた絶縁膜への電界集中が抑制され、微細化されても、絶縁破壊が抑制され、十分な信頼性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に形成され、ビアホール506cと、ビアホール506cの上部に連結された配線溝(上層配線溝)505cとを有する第1の絶縁膜(第2の層間絶縁膜)504と、ビアホール506cに埋め込まれたビア506と、ビア506に電気的に接続され、配線溝(上層配線溝)505cに埋め込まれた金属配線(上層配線)505と、ビアホール506cの側面に設けられ、金属配線(上層配線)505の側面と第1の絶縁膜(第2の層間絶縁膜)504との間に挟まれて形成された第2の絶縁膜(絶縁膜)508とを備えている。平面的に見て、ビア506は、隣接する金属配線(上層配線)505間の領域に、はみ出す事無く形成されている。

(もっと読む)

多層相互接続のための波形界面を有するデバイス(多層相互接続のための波形界面)

【課題】 相互接続積層物内の誘電層間にナノスケール波形界面を有するデバイス構造を提供する。

【解決手段】 相互接続積層物においてナノメートル・スケール波形界面を有する界面を含む誘電複合構造は、接着強度および界面破壊靭性の向上をもたらす。また、波形接着促進物層(114)を更に含んで固有の界面接着を更に向上させる複合構造も記載する。また、自己アセンブリング・ポリマー系およびパターン転送プロセスを用いてこれらの構造を可能とするための、ナノメートル・スケール波形界面を形成するための方法も記載する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

配線構造及び半導体装置、並びにそれらの製造方法

【課題】配線間隔の狭い回路において配線容量を低減させた配線構造及び半導体装置、並びにそれらの製造方法を提供することを目的とする。

【解決手段】導電性の配線層8を形成する工程と、配線層8に配線パターンを形成する工程と、前記配線パターンの配線10A,10B,10C,10D間に絶縁性の配線層間膜11を形成する工程と、配線層間膜11の厚さ方向に、縦穴状の微細孔14を複数形成する工程を有することを特徴とする。また、微細孔14は、ナノ粒子12またはナノ粒子12を含有する材料からなるマスクを用いて、エッチングすることにより形成することができる。

(もっと読む)

半導体装置

【課題】シリコン基板を備え、高周波信号を導通させたときに発生する高調波が小さい半導体装置を提供する。

【解決手段】半導体装置1において、シリコン基板2上にシリコン酸化膜3を形成し、その上に配線6及び配線8を設ける。配線6は、周波数が500MHz以上であり、電力が20dBm以上である高周波信号が流れる高周波配線とし、配線8は一定電位が印加される定電位配線とする。そして、シリコン基板2におけるシリコン酸化膜3に接する領域に、アクセプタとしてのホウ素を導入し、ホウ素ドーピング層9を形成する。ホウ素ドーピング層9の厚さは1μm以下とし、ホウ素の面濃度は4.0×1010乃至3.5×1011cm−2とする。

(もっと読む)

半導体装置

【課題】表面保護膜や層間膜などの配線被覆膜の剥がれやひび割れの進行を防止することができる半導体装置を提供すること。

【解決手段】この半導体装置は、半導体チップ1と、半導体チップ1上に積層された保護膜2と、保護膜2上に突出する凸型端子3と、凸型端子3に接着される半田ボール4とを備えている。半導体チップ1の基体をなす半導体基板7上には、第1配線層8、第1層間膜9、第2配線層10、第2層間膜11、第3配線層12および最上層配線被覆膜15が半導体基板7側からこの順に積層されている。そして、半導体基板7の周縁から所定幅だけ内側の位置においては、最上層配線被覆膜15の表面から第2層間膜11および第1層間膜9を貫通して半導体基板7の表層部に達する溝18が半導体基板7の素子形成領域Bを取り囲んで形成されている。そして、この溝18には、保護膜2が入り込んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】 良好な動作特性を維持しつつ、隣接するゲート電極間、或いはゲート電極とコンタクトプラグとの間の離間距離を拡大することなくこれらの間における短絡の発生を防止することを可能にする半導体装置並びにその製造方法を提供する。

【解決手段】 半導体基板10上の所定の領域に不純物拡散領域6が離隔形成されており、2つの不純物拡散領域に挟まれる領域上にゲート電極(3、5)が形成される。又、不純物拡散領域6と配線12との電気的接続を形成するために層間絶縁膜9を貫通してコンタクトプラグ11が形成されており、このコンタクトプラグ11の外周部の内、少なくともコントロールゲート電極5と対向する領域の一部の領域には層間絶縁膜9と別工程で形成される埋め戻し絶縁膜15が形成される。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板および該シリコン基板上に設けられた低誘電率膜と配線との積層構造からなる低誘電率膜配線積層構造部を備えた半導体装置において、低誘電率膜を剥離しにくいようにする。

【解決手段】 低誘電率膜配線積層構造部3のうち配線5が配置された部分は平面方形枠状の溝6内に設けられ、その上には酸化シリコン等からなるパッシベーション膜8が設けられている。そして、溝6の内側における低誘電率膜配線積層構造部3およびパッシベーション膜8の側面は、溝6内およびその上方に設けられたポリイミド系樹脂等からなる保護膜10によって覆われている。これにより、溝6の内側における低誘電率膜4を剥離しにくいようにすることができる。この場合、溝6の外側における低誘電率膜4の側面が露出されているが、この露出された低誘電率膜4が剥離しても、保護膜10の側面が露出されるだけであり、溝6の内側における低誘電率膜4がそれに続いて剥離することはない。

(もっと読む)

21 - 40 / 66

[ Back to top ]