Fターム[5F033TT07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | コンタクトホールの側壁 (799)

Fターム[5F033TT07]に分類される特許

201 - 220 / 799

半導体装置とその製造方法、及び電子機器

【課題】寄生容量を低減し、高性能化を図った固体撮像装置等の半導体装置とその製造方法、前記固体撮像装置を備えたカメラ等の電子機器を提供するものである。

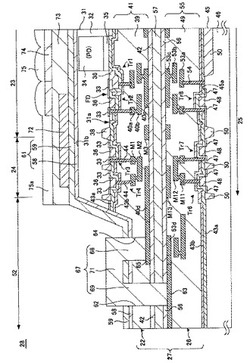

【解決手段】本発明の半導体装置は、2つ以上の半導体チプ部22,26が貼り合わされた積層半導体チップ27を有する。積層半導体チップ27では、少なくとも第1の半導体チップ部22に画素アレイ23と多層配線層41が形成され、第2の半導体チップ部26にロジック回路25と多層配線層55が形成される。第1の半導体チップ部22には、一部の半導体部分が全て除去された半導体除去領域52が形成され、半導体除去領域52内に第1の半導体チップ部22と第2の半導体チップ部26との間を接続する複数の接続配線67が形成される。この半導体装置は、裏面照射型の固体撮像装置として構成される。

(もっと読む)

半導体装置製造方法及び積層半導体装置

【課題】複数の基板を貼り合わせる積層半導体装置を効率よく製造できる方法を提供する。

【解決手段】複数の基板を貼り合わせて積層半導体装置を製造する半導体装置製造方法であって、回路が形成された複数の基板のうちの一の基板に凹部を形成する凹部形成ステップと、一の基板を複数の基板のうちの他の基板に重ね合わせる重ね合わせステップと、重ね合わせステップの後に、一の基板の凹部に導電性材料を導入することにより、一の基板の回路と他の基板の回路との間の電気的な導通路を形成する導通形成ステップとを備える半導体装置製造方法が提供される。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備し半導体装置において、半導体ウエハからダイを低コストで形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように輸送テープあるいはキャリヤ・テープ38上に形成される。この傾斜サイドウォール上、および、底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIからの保護を提供する。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備した半導体装置において、低コストで、半導体ウエハからEM保護の施されたダイを形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように形成される。この傾斜サイドウォール上、および、半導体ダイの底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIから保護する。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

ウエハレベルCSPの製造方法

【課題】 ウエハレベルで組立て可能な薄型CSPを提供する。

【解決手段】 ウエハ裏面側に、スクライブライン上の特定箇所に形成したスルーホールの側面を利用して,ウエハ表裏間の電気接合を取り、基板実装用の電極を配置する。そしてスルーホールは半導体基板のスクライブライン上をハーフエッチングした凹部を、バックグラインドを用いて裏面研磨することで形成する。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数の絶縁膜及び電極膜が交互に積層された信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、メモリアレイ領域にメモリ積層体を設け、周辺回路領域にダミー積層体を設け、ダミー積層体にダミーホール31a,31bを形成し、その内部に絶縁部材を埋め込む。そして、絶縁部材内に複数本のコンタクト35a,35b,35c,35d,35eを形成する。コンタクト35a,35bはMOSFET40のソース層36に、コンタクト35c,35dはドレイン層37に、コンタクト35eはゲート電極38に接続される。そして、1つのダミーホール内に配置された複数本のコンタクトは、同じ電位が印加されるコンタクトとするか、ダミーホールの長手方向に延びる中心線41a,41c、41d、41f、41h、41j、41k、41lから外れた位置に配置する。

(もっと読む)

半導体素子の製造方法

【課題】簡単な工程設備を用いて短い工程時間内に半導体素子のビアを形成できる半導体素子の製造方法を提供すること。

【解決手段】基板101に絶縁膜107と拡散防止膜109で内壁を被覆したビアホール105を形成する。荷電された金属粒子113を、電気力又は磁気力を利用して移動させて、このホールを金属粒子で充填する。ビアホールの下部から上方へ充填されるので、内部に空隙が発生することを抑制できる。従来技術による銅電気メッキ方式と比較すると、非常に短時間内に大きくて深いビアホールを金属粒子で充填できるため、シリコン貫通ビア(TSV)の工程コスト、及び工程時間を短縮することが出来る。また、従来技術の樹脂成分が多く含まれているメタルペーストを用いる乾式充填方式と比較すると、荷電された金属粒子を用いることで、より密なTSV金属配線を形成できる。

(もっと読む)

電子基板に組み込まれたビア構造

基板に配置されたビア構造のシステム。当該システムは、基板に配置された外側導電層と、内側絶縁層と、内側導電層とを備える第1ビア構造を有する。外側導電層は内側絶縁層と基板とを分離し、内側絶縁層は内側導電層と外側導電層とを分離する。第1相補的対の第1信号が内側導電層を通過し、第1相補的対の第2信号が外側導電層を通過する。別の実施形態では、電子基板にビア構造を形成する方法が提供される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面とを有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記貫通孔の内壁に設けられ、平面視において前記貫通孔と重なる位置に接続孔を有する樹脂膜と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に第1凹部を有する配線層と、前記配線層に接続され、前記第1凹部内と前記樹脂膜を介して前記貫通孔内とに設けられた貫通電極とを含む半導体装置。

(もっと読む)

半導体装置

【課題】 貫通穴の開口寸法が小さく小型化や微細化を容易にでき、貫通穴全体の金属層形成速度を向上する事が容易で、金属層形成工程に要する時間を短縮する事が容易な貫通穴形状を構成した半導体装置を提供することを目的とする。

【解決手段】 基板の表面と裏面とを接続する貫通穴内に金属層を設けた半導体装置において、貫通穴側壁に表面と裏面とを結ぶ向きに複数の突起を設けた事を特徴とする。

(もっと読む)

貫通電極基板及び貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板は、表裏を貫通する貫通孔を有する基板と、前記貫通孔内に充填され、金属材料を含む導通部と、を備え、前記導通部は、結晶粒径が29μm以上の金属材料を少なくとも含み、前記導通部の一端は、前記導通部の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部は、面積重み付けした平均結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

配線基板及び配線基板の製造方法

【課題】 貫通電極と配線層との間における電気抵抗の増加を抑制できる配線基板及び半導体装置を提供する。

【解決手段】 半導体基板と、半導体基板の少なくとも上面に形成され、導体層及び第1絶縁層を有する配線層と、半導体基板及び配線層の第1絶縁層を貫通する貫通電極と、半導体基板と貫通電極との間に形成された第2絶縁層と、を備える配線基板であって、貫通電極は、配線層の第1絶縁層を貫通する第1導電部と、半導体基板を貫通し、第1導電部と電気的に接続し、第1導電部の断面積よりも大きい断面積を有し、且つ導体層と電気的に接続する段差面を含む第2導電部と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面を有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に凹部を有する配線層と、前記貫通孔と前記凹部とで構成される溝の内壁および前記溝の底面に設けられ、且つ、平面視において前記配線層の前記凹部と重なる接続孔を有する樹脂膜と、前記配線層に接続され、前記樹脂膜を介して前記溝内に設けられた貫通電極とを含むことを特徴とする。

(もっと読む)

回路基板及び電子デバイス

【課題】導体の亀裂、基板のクラック、絶縁膜の破壊等を生じ難い高信頼度・高品質の回路基板及び電子デバイスを提供する。

【解決手段】基板1と、導体3とを含んでおり、導体3は、金属または合金でなり、基板1に設けられ、少なくとも基板1と対面する領域に、等軸晶31の領域を有する。この構造によれば、基板1と対面する領域で、導体3の等軸晶組織による等方性が得られるため、導体3の亀裂、絶縁膜の破壊及び基板1のクラックなどの発生が抑制される。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極およびこれと一体的に形成された裏面電極を有する半導体装置において、貫通電極の膜厚と裏面電極の膜厚とを独立に制御することにより、貫通電極の剥離の問題と裏面配線の剥離の問題を同時に解消することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10と、半導体基板の上方に形成された少なくとも1層からなる配線層13と、半導体基板の裏面から配線に達する貫通電極30と、半導体基板の裏面に設けられて貫通電極に接続された裏面配線40と、裏面配線に接続された外部端子50と、を含む半導体装置であり、裏面配線は、少なくとも外部端子との接続部を含む部分の膜厚が、貫通電極の膜厚よりも厚く形成されている。

(もっと読む)

半導体装置とその製造方法、及び電子機器

【課題】積層される半導体ウェハにより、量産性向上、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。

【解決手段】半製品状態の回路を備えた半導体ウェハ31,45を複数積層して貼り合わせ、複数の半導体ウェハ31,45からなる積層体を形成し、積層体のうち、上層の半導体ウェハ31の半導体層を薄肉化する。また、上層の半導体ウェハ31側から最下層の半導体ウェハ45に形成された配線に達する貫通開口部77を形成し、最下層の半導体ウェハ45に形成された配線を露出させることにより電極パッド部78を形成する。これにより、貫通開口部77は、半導体ウェハ31,45の脆弱な接合面を貫通して形成され、電極パッド部78は、脆弱な接合面よりも下層の半導体ウェハ45の配線において形成される。これにより、電極パッド部78における外部配線との配線時に、脆弱な接合面に係る応力を低減することができる。

(もっと読む)

201 - 220 / 799

[ Back to top ]