Fターム[5F033VV07]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ボンディングパッド、バンプ電極 (1,972)

Fターム[5F033VV07]に分類される特許

161 - 180 / 1,972

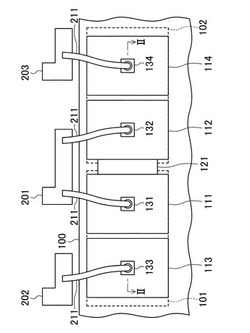

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程の効率化とパッシベーション膜の剥離の抑制とが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、金を含む配線30a及び配線30bを形成する工程と、配線30a及び配線30bに接して、窒化シリコン膜32をプラズマ気相成長する工程と、窒化シリコン膜32の製膜レートよりも大きな製膜レートのもと、窒化シリコン膜32に接し、窒化シリコン膜32よりもシリコン組成比が小さい窒化シリコン膜22をプラズマ気相成長する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】凹形状を有するホールの内壁側面上に側壁保護膜の一部を残留させることにより、ホールの内壁側面を平滑化する。後の工程でホール内に材料を埋設する際にも、ボイドを発生させることなく優れた埋設性でホール内を材料で埋設させる。

【解決手段】半導体基板の裏面上にマスクを設ける工程と、マスクを用いて半導体基板を貫通すると共に凹形状の内壁側面を有するホールであって内壁側面が側壁保護膜で覆われたホールを形成する工程と、側壁保護膜の一部を残留させるようにマスクを除去する工程と、を有する半導体装置の製造方法。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETのゲート電極を基板の周囲において引き出すゲート引き出し配線の引き出し部は、素子領域内と同等の効率で機能するMOSFETのトランジスタセルCを配置することができない非動作領域となる。つまり、ゲート引き出し配線を、例えばチップの4辺に沿って配置すると、非動作領域が増加し、素子領域の面積拡大や、チップ面積の縮小に限界があった。

【解決手段】 ゲート引き出し配線と、ゲート引き出し配線と保護ダイオードとを接続する導電体とを、チップの同一辺に沿って曲折しない一直線状に配置する。又これらの上に重畳して延在し、これらと保護ダイオードを接続する第1ゲート電極層の曲折部を1以下とする。更に保護ダイオードを導電体またはゲート引き出し配線と隣接して配置し、保護ダイオードの一部をゲートパッド部に近接して配置する。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】電位ドロップに起因するセルの動作不良を防止すること。

【解決手段】本発明に係る半導体集積回路は、チップ1上に配置された電源パッド2aと、電源配線構造10を介して電源パッド2aに接続された回路群21,22とを備える。その電源配線構造10は、異なる配線層に形成され複数の交差点IS1,IS2においてオーバーラップする複数の第1電源配線11及び複数の第2電源配線12と、それら複数の第1電源配線11と複数の第2電源配線12を接続するビア13とを有する。上記回路群は、第1領域R1に配置された機能ブロック21を含む。ビア13は、第1領域R1と電源パッド2aの間の第2領域R2における複数の交差点IS2の一部に配置されていない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

半導体装置

【課題】プロセス数を増大させることなく、応力を緩和できる構造を有する半導体装置を提供する。

【解決手段】一方の面に埋め込み酸化層と半導体層がこの順で積層される半導体基板10を加工して作製され、前記一方の面側で他の基板に接合される半導体装置であって、前記埋め込み酸化層及び前記半導体層を加工して形成される半導体素子20と、前記埋め込み酸化層及び前記半導体層を加工して形成され、前記半導体素子に接続される配線部と、前記配線部の端部に連続する前記半導体層によって構成され、当該半導体層の下側の埋め込み酸化層が除去されて前記半導体基板との間に空隙が形成されるパッド部40と、前記パッド部と前記他の基板を接合する接合部とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

半導体装置

【課題】ボンディングパッドの下の絶縁膜にクラックが入ることをより防止する。

【解決手段】三層構造のボンディングパッドを有する半導体装置とし、この三層構造のボンディングパッドは、第一金属膜と、第二金属膜と、第三金属膜とからなり、第二金属膜は、第一金属膜及び第三金属膜のヤング率よりも高いヤング率を有するようにした。

(もっと読む)

半導体装置

【課題】規格により規定された速度による信号の転送を実現し、半導体装置やそれを内蔵した電子機器の誤動作を防止する。

【解決手段】第1の半導体素子101の導体配線層106に、パッケージ基板100の信号端子103と第2の半導体素子102の信号端子117とを接続する信号線導体113aと、パッケージ基板100の電源端子104と第2の半導体素子102の電源端子118とを接続する電源導体114とを、信号線導体113aが導体配線層106において、信号線導体113aとの間に水平方向に一定の間隔をあけて隣接する電源導体114に挟まれるように形成する。

(もっと読む)

配線パターン及びその製造方法並びに半導体装置

【課題】配線パターンを覆う絶縁層をできる限り薄くする。

【解決手段】配線パターン1は、第一の一対の端子3,4及び該第一の一対の端子3,4間を接続する複数の第一の引き回し部5を有する第一の配線2と、第二の一対の端子7,8及び該第二の一対の端子7,8間を接続する少なくとも一つの第二の引き回し部9を有する第二の配線6とを含む。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置の配線構造及びその製造方法

【課題】第2メタル層が密着する絶縁層にクラックを生じさせ難い半導体装置の配線構造及びその製造方法を提供する。

【解決手段】半導体装置の配線構造は、絶縁層12と、絶縁層12によって覆われた第1メタル層13と、互いに間隔をあけて絶縁層12上に配列され且つ第1メタル層13より厚く形成された複数の電極部分101,102,…を有する第2メタル層14とを備え、絶縁層12の複数のビアホール内に配置された第1メタル層13と複数の電極部分101,102,…との間を繋ぐ複数の電極部分によって、複数の電極部分を第1メタル層13に電気的に接続する複数の貫通配線15を備えている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

161 - 180 / 1,972

[ Back to top ]