Fターム[5F033VV07]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ボンディングパッド、バンプ電極 (1,972)

Fターム[5F033VV07]に分類される特許

201 - 220 / 1,972

半導体装置およびその製造方法

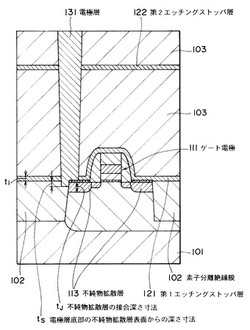

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

集積回路装置およびその調製方法

【課題】 非常に複雑で費用がかかるバンプ・パッドを形成せずに、集積回路装置を製造する。

【解決手段】 集積回路装置100は、第1の環状誘電体ブロック21Aを有する底部ウェハー10Aと、底部ウェハー10A上に配置される、第2の環状誘電体21Bを有する少なくとも1つの積層ウェハー10Bと、実質的に直線状に底部ウェハー10A中へと積層ウェハー10Bを貫通する導電性ビア49とを備える。底部ウェハー10Aと積層ウェハー10Bはその間の接着層41により接合されている。底部ウェハー10Aと積層ウェハー10Bとの間にはバンプ・パッドは配置されない。導電性ビア49は、第1の環状誘電体ブロック21Aおよび第2の環状誘電体ブロック21Bの内部に位置している。

(もっと読む)

半導体装置の製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】半導体素子の第1領域と接続される表面電極17、および通路12の少なくとも一部に、半導体素子の第2領域と接続される第1金属配線18を形成する。その後、はんだ29が実装されない通路12bに形成する第1保護膜25の高さが、はんだ29が実装される通路12aに形成する第1保護膜25の高さよりも高くなるように、注入器32を用いて第1保護膜25を通路12に塗布する。続いて、表面電極17および第1保護膜25の上に金属層27、28を形成してはんだ29が実装されない通路12bに形成した第1保護膜25が金属層27、28から露出するように、はんだ29が実装されない通路12bに形成した第1保護膜25の一部および金属層27、28を切削する。

(もっと読む)

半導体装置の製造方法

【課題】レーザー光の照射による滓の発生を抑えるようにするとともに、分断後の低誘電率膜にダメージを与えないようにする。

【解決手段】半導体ウエハ61の一方の面61aの上に形成された低誘電率膜21をドライエッチングすることにより低誘電率膜21に溝21aを形成し、低誘電率膜21の上に封止層41を形成するとともに、低誘電率膜21の溝21a内に封止層41の一部を埋め込み、半導体ウエハ61及び封止層41を低誘電率膜21の溝21aに沿って分割する。

(もっと読む)

半導体装置、半導体装置の検査方法、及び、半導体装置の製造方法

【課題】半導体装置の製造工程の増大を抑制しつつ、パッドの針跡を容易に確認できるようにする。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に形成された回路素子と、半導体基板1上に形成され、回路素子と電気的に接続されたパッド(接続パッド4)と、を有している。パッドは、平面視において、導体が存在する実体パターン41と、前記導体が存在しない開口パターン42と、を含む所定のパターン形状に形成されている。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

半導体装置

【課題】3次元的に積層された複数の半導体チップを有する半導体装置の製造歩留まりを向上できる技術を提供する。

【解決手段】半導体基板1の第2面1bからパッド3に達する貫通電極17が形成されている。貫通電極17の内部にある貫通空間は、第1孔7および第1孔7よりも孔径の小さい第2孔11によって構成されている。半導体基板1の第2面1bから半導体基板1を貫通して層間絶縁膜2の途中まで第1孔7が形成されている。そして、第1孔7の底部から層間絶縁膜2を貫通してパッド3に達する第2孔11が形成されている。このとき、半導体基板1の第1面1aに形成されている層間絶縁膜2は、第1孔7の底面と半導体基板1の第1面1aとの段差を反映して段差形状になっている。すなわち、第1孔7の底面とパッド3間に存在する層間絶縁膜2の膜厚がその他の場所の層間絶縁膜2の膜厚よりも薄くなっている。

(もっと読む)

半導体装置

【課題】機械的強度が比較的弱い材料を層間絶縁膜の材料として用いる場合であっても、集積度が高く、信頼性の高い半導体装置を提供する。

【解決手段】支持基板10と、支持基板上に形成され、絶縁層26,28,38,44,50,56,62,68を介して複数の配線36,42,48,54,60,66を積層して成る多層配線構造と、多層配線構造上に形成された電極パッド78と、多層配線構造を貫いて支持基板に達し、電極パッドを支持する構造物76であって、断面が十字形又はY字形である構造物とを有している。この構造物により電極パッドが支持されているため、ボンディングを行った際に電極パッドの下方に存在する構成要素に大きなストレスが加わるのを防止することができ、多層配線構造の一部に、機械的強度が比較的弱い層間絶縁膜を用いた場合であっても、微細な配線パターンの変形や断線等、トランジスタの破壊等を防止することができる。

(もっと読む)

半導体装置及び固体撮像装置

【課題】 チップ面積を縮小可能な半導体装置を提供する。

【解決手段】 電源配線105とパッド103とは第1の配線層に配される。そして、電源配線105とパッド103とは互いに重ならないように配される。信号配線106a、106bは第2の配線層に配される。信号配線107は第2の配線層とは異なる層に配される。信号配線107は、パッド103と重なるように、パッド103の下部に配される。信号配線106と信号配線107とは、プラグ108によって互いに接続される。パッド103と信号配線107との間に緩衝部109が配される。

(もっと読む)

光電変換装置およびその製造方法

【課題】 配線材料の層間絶縁膜への拡散を抑制する拡散抑制膜による多層配線構造を設けた光電変換装置において、工程を増加させることなく、受光効率を高める。

【解決手段】 本発明は、半導体基板に配された光電変換素子と、前記半導体基板上に層間絶縁膜を介して複数の配線層が配された多層配線構造を有する光電変換装置であって、最上配線層の上部に、前記最上配線層を構成する材料の拡散を抑制する拡散抑制膜が配され、前記拡散抑制膜は、前記最上配線層及び前記層間絶縁膜の前記光電変換素子に対応する領域を覆って配されており、前記拡散抑制膜の前記光電変換素子に対応する領域にレンズが配されていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を削減し、電気抵抗値のバラツキを低減して歩留まりを向上させる。

【解決手段】まず、半導体基板1の平面1aに、開口部を有するマスク層を形成し、次いで、半導体基板1に、マスク層の開口部から電極パッド層4に達するビアホール6を形成した後、マスク層を除去する。次に、金属層形成工程において、半導体基板1に形成したビアホール6の底部6aとなる電極パッド層4上に、電極パッド層4よりも絶縁材料の密着性が低い金属層8を形成する。次に、絶縁層形成工程において、化学気相成長法にて金属層8を除く部分、即ちビアホール6の側壁部6bに絶縁材料からなる絶縁層9を形成する。そして、導電膜形成工程において、半導体基板1の平面1a及びビアホール6の内部に導電層12を形成する。

(もっと読む)

三次元積層構造を持つ半導体装置の製造方法

【課題】 三次元積層構造を持つ半導体装置において、積層された半導体回路層間の積層方向の電気的接続を、埋込配線を使用して容易に実現する半導体装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの半導体基板11の表面に、絶縁膜14で内壁面が覆われたトレンチ13を形成し、トレンチ13の内部に導電性材料を充填して導電性プラグ15を形成する。次に、トレンチ13とは重ならないように所望の半導体素子を基板11の表面または内部に形成し、その上に層間絶縁膜19を介して多層配線構造30を形成してから、多層配線構造30の表面にプラグ15に電気的に接続されたバンプ電極37を形成する。そして、電極37を用いて基板11を支持基板40に固定してから基板11をその裏面側から選択的に除去し、絶縁膜14を基板11の裏面側に露出させる。基板11の裏面側に露出せしめられた絶縁膜14を選択的に除去してプラグ15を露出させ、その端に電極42を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、アルミ配線パターンに含まれるアルミニウムと銅配線に含まれる銅とが反応して高抵抗の合金が生成されることを防止した上で、導電膜である窒化チタン膜に起因する半導体基板の反りを低減することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】第2の層間絶縁膜18に形成されたコンタクト孔27により露出された銅配線16の上面16aを覆うように、窒化チタン膜を含む第1の導電膜21を設けると共に、アルミ配線パターン23と第1の導電膜21及び第2の層間絶縁膜18との間に、窒化チタン膜を含まない第2の導電膜22を設ける。

(もっと読む)

チップの製造方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体層の表面から貫通孔絶縁層が後退した場合においても、半導体層と貫通電極との絶縁性を確保する。

【解決手段】貫通孔6には、貫通孔絶縁層7、8を介して貫通電極9が埋め込まれ、貫通孔絶縁層7、8は、半導体層3の表面から後退するようにして形成され、半導体層3と貫通電極9との間には、貫通孔絶縁層7、8の後退部分の対応した凹部10が形成され、貫通電極9の側壁には、凹部10に埋め込まれたサイドウォール絶縁膜12が形成される。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極のための開口部を形成する時に、上部配線層の配線とのミスアラインメント問題が発生しない半導体装置を製造する方法の提供。

【解決手段】第1面及び第1面の反対側に第2面を有する基板を準備する段階と、基板の第1面から基板の厚さ方向に延長して貫通電極が形成される領域に犠牲膜パターンを形成する段階と、基板の第1面上に形成され、犠牲膜パターン上に位置する配線を有する上部配線層を形成する段階と、基板の第2面を部分的に除去して犠牲膜パターンを露出させる段階と、犠牲膜パターンを基板の第2面から除去して配線を露出させる開口部を形成する段階と、開口部内に配線と電気的に接続される貫通電極を形成する段階と、を有する。

(もっと読む)

201 - 220 / 1,972

[ Back to top ]