Fターム[5F033VV07]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ボンディングパッド、バンプ電極 (1,972)

Fターム[5F033VV07]に分類される特許

101 - 120 / 1,972

半導体装置の製造方法

【課題】LTHC膜に由来する基板の汚染を低減する。

【解決手段】基板の第1の主面を光熱変換膜を介して支持基板に張付ける工程と、支持基板上に露出した光熱変換膜を除去する工程と、を有することを特徴とする半導体装置の製造方法。支持基板上に光熱変換膜を形成する工程と、半導体基板より外側に光熱変換膜が延在するように半導体基板を前記支持基板に張付ける工程と、光熱変換膜に汚染防止処理を行う工程と、支持基板と半導体基板とを分離させる工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 厚い絶縁樹脂層のウェハレベルCSPで、第1電極(チップパッド)と外部電極(バンプ)との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】 次の各工程を含む半導体装置の製造方法、(1)絶縁樹脂層を半導体ウェハの上に形成し、(2)開口径が(D1)となるよう絶縁樹脂層の一部を除去し半導体ウェハ上の第1電極を露出し、(3)フィルム状レジストを半導体ウェハの全面に、第1電極とレジストとの間が中空構造となるよう貼付け、(4)レジストをパターニングし、再配線層を絶縁樹脂層の上に形成し、レジストパターンを除去し、めっきした部分以外のシード層を除去し、(5)再配線層の上に再配線保護層を形成し、(6)再配線保護層の開口径(D2)が、D2>D1となるように再配線保護層の一部を除去して第1電極と、第2電極を露出し、(7)第1電極及び第2電極の上にめっき層を形成し、(8)めっき層を溶融して外部電極を形成する。

(もっと読む)

超音波スキャンに基づくシリコン貫通配線(TSV)におけるボイドの存在の推定

【課題】 3次元集積化構造中の不良を超音波スキャンによって検出することであって、シリコンウエハなどのボードに配列されているシリコン貫通配線(TSV)においてプロセス中に発生してしまう可能性のあるボイドの存在を非破壊的に検出すること。

【解決手段】 ボード面にわたって超音波スキャンをすると、(はんだ)バンプ等が物理的な遮蔽物として超音波を散乱させてしまい、超音波スキャンによる測定を妨げてしまう。そこで、これら複数のTSVの中から、テスト要素グループ(TEG)に属する単数または複数のTSVを選び出すにあたって、物理的な遮蔽物を少なく存在するように選び出す。

(もっと読む)

半導体装置

【課題】本発明は、金属膜の端部の応力により金属膜の端部直下の表面電極がダメージを受けることを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、基板24と、該基板24の上に、アルミを含む材料で形成された表面電極26と、該表面電極26の上に、はんだ付け可能な材料で形成された金属膜28と、該表面電極26の上の部分と、該金属膜28の端部に重なる重畳部分30aとが一体的に形成されて該金属膜28の端部を固定する端部固定膜30と、を備えたことを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置及びその製造方法

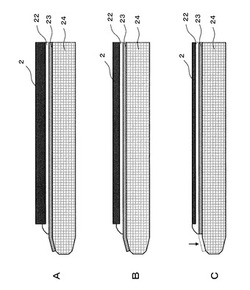

【課題】 半導体装置全体の応力緩和を実現すると共に、応力制御するための特別な構造が不要となり、装置の設計自由度も確保することができる半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1において、シリコン基板2とその上部に形成される金属配線層との絶縁を確保するために形成される絶縁部5を二層(第一絶縁部5a、第二絶縁部5b)に分離し、その一部に他の成膜工程で発生する残留応力と逆方向の残留応力を持たせることにより、半導体装置全体に作用する残留応力を低減する。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

電力用半導体装置及びその製造方法

【課題】本発明は、信頼性の高い外部電極との接続構造を有する電力用半導体装置及びその製造方法の提供を目的とする。

【解決手段】本発明の電力用半導体装置は、段差を有する絶縁膜9と、絶縁膜9の前記段差を覆って形成された上部配線10と、上部配線10上の少なくとも前記段差の側壁に対応する部分を含む所定箇所に、部分的に形成された酸化膜16と、上部配線10及び酸化膜16上に形成され、半田21により外部導体22と接合するバリア層20とを備える。

(もっと読む)

半導体チップ、半導体装置および半導体装置の製造方法

【課題】バンプ電極同士の横滑りを防止し、バンプ電極同士を接合する接合材料のはみ出しを抑制する。

【解決手段】

半導体チップ10は、基板17と、基板17の一方の面に設けられた第1のバンプ電極50と、基板17の他方の面に設けられた第2のバンプ電極60と、第1のバンプ電極50と第2のバンプ電極60のうちの少なくとも一方の頂面に形成された導電性の接合材料層61と、を有している。第1のバンプ電極50の頂面は凸面54であり、第2のバンプ電極60の頂面は凹面63である。

(もっと読む)

半導体装置

【課題】信頼性を向上させた半導体装置の作製方法の提供を課題とする。

【解決手段】基板上に第1の導電層を形成する工程と、第1の導電層上に、金、銀または

銅の導電性粒子(導電性微粒子ともよぶ)と樹脂を含む第2の導電層を形成する工程と、

第2の導電層にレーザービームを照射して、前記第1の導電層と前記第2の導電層が接す

る面積(部分)を増加させる工程とを含む半導体装置の作製方法を提供する。レーザービ

ームを照射する工程を含むことにより、第1の導電層上に、導電性粒子と樹脂からなる第

2の導電層を形成した場合でも、第1の導電層と第2の導電層が接する部分を増加させ、

第1の導電層と第2の導電層の間の電気的な接続不良を改善することができる。

(もっと読む)

半導体チップのクラックのチェックテスト構造を有する半導体装置

【課題】半導体チップ積層後に、チップごとにクラックの有無検出可能な半導体装置の提供。

【解決手段】積層半導体装置において、半導体チップ21〜24は、基板10とこの表裏面の対向する位置に形成した対のテスト端子と配線61を備える。これらは、一対の(表側)第1のテスト端子621h、(裏側)第1のテスト端子621t及び複数対の(表側)第2のテスト端子622〜625h、(裏側)第2のテスト端子622〜625tで、貫通電極TSVT1が(表側)第1のテスト端子と(裏側)第1のテスト端子を接続し、貫通電極TSVT2〜5が対の(表側)第2のテスト端子と(裏側)第2のテスト端子同士を接続し、配線は、一端が第1のテスト端子と、他端が第2のテスト端子の一つに接続され、基板の外周に沿って延びる。また異なる半導体チップの上下に隣接する第2のテスト端子同士も接続する。

(もっと読む)

ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法

【課題】ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体装置の正面と背面に対応する正面と背面を有する装置基板と、装置基板の正面上に形成される金属層部と、半導体装置の背面に設置され、金属層部と電気的に接続するボンディングパッドと、装置基板の背面上に設置されるシールド構造と、を含み、シールド構造とボンディングパッドは異なる厚さを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

半導体装置の製造方法

【課題】感光性樹脂膜を塗布した後のパターン形成不良を抑制する。

【解決手段】まず、基板上に、配線を形成する(S110)。次いで、配線上にパッシベーション膜を形成する(S120)。次いで、基板をアニールする(S130)。次いで、基板をアニールする工程(S130)の後、パッシベーション膜上に、感光性樹脂膜として、フォトレジスト膜を塗布する(S140)。次いで、フォトレジスト膜が塗布された基板を少なくとも一回以上ベークする(S150)。次いで、フォトレジスト膜を、露光および現像によりパターニングする(S160)。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

半導体装置及びその製造方法並びに積層型半導体装置

【課題】貫通電極と直接に接続される配線の信頼性を向上できるようにする。

【解決手段】半導体装置100は、貫通孔1Aを有する半導体基板1と、半導体基板1の上に形成された第2層間絶縁膜7bと、第2層間絶縁膜7bに貫通孔1Aを覆うように形成された第1の外部接続用配線8a1と、第2層間絶縁膜7bの上に、第1の外部接続用配線8a1を覆うように形成された第3層間絶縁膜7cと、第3層間絶縁膜7cにおける第1の外部接続用配線8a1の上側部分に形成された第2の外部接続用配線8b1と、貫通孔1Aにおける少なくとも内壁面に形成されると共に、各外部接続用配線8a1、8b1とそれぞれ電気的に接続される貫通電極15Aとを備えている。第1の外部接続用配線8a1は、複数の孔部19aを有し、第2の外部接続用配線8b1は、第1の外部接続用配線8a1の孔部19aを覆うように形成されている。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

101 - 120 / 1,972

[ Back to top ]