Fターム[5F033VV07]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ボンディングパッド、バンプ電極 (1,972)

Fターム[5F033VV07]に分類される特許

41 - 60 / 1,972

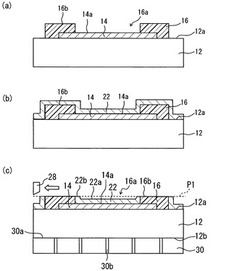

半導体装置の製造方法

【課題】切削又は研削加工を用いつつ、低コストで金属電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板12の主面12aに下地電極14を形成する工程と、下地電極を覆う保護膜16を形成するとともに、該保護膜に下地電極を露出させる開口部16aを形成する工程と、保護膜及び開口部から臨む下地電極の表面を覆うように第1金属膜22を形成する工程と、第1金属膜が形成された半導体基板を、裏面12bを搭載面として吸着ステージ30に吸着固定した状態で、吸着ステージと平行に設定された基準面上P1に位置する保護膜の部分及び第1金属膜の部分を、切削により除去して、第1金属膜をパターニングする工程と、パターニング工程後、裏面から半導体基板を研削し、半導体基板の厚さを所定厚さまで薄くする工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

(もっと読む)

半導体装置

【課題】半導体装置の最上層の保護膜のクラックを防いで、半導体装置の信頼性の向上を図ることのできる技術を提供する。

【解決手段】ボンディングパッドBP1を長方形状とし、ボンディングパッドBP1のワイヤボンディング領域BP1wでの保護膜5の重なり幅を、ボンディングパッドBP1のプローブ領域BP1pでの保護膜5の重なり幅よりも広くなるように、ボンディングパッドBP1上の保護膜5に開口部6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】基板を貫通する電極の形成に適用できる新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に半導体素子を形成する工程と、半導体基板に孔を形成する工程と、半導体素子の上方と孔の内壁および底を覆うように絶縁膜を形成する工程と、異方性エッチングにより、半導体素子の上方と孔の底の絶縁膜を除去する工程と、孔の底に金属拡散防止膜を形成する工程と、孔に導電膜を埋める工程とを有する。

(もっと読む)

半導体装置、及びその製造方法

【課題】絶縁破壊が発生しにくい半導体装置及びその製造方法を提供する。

【解決手段】集積回路13と電気的に接続する電極14が位置する半導体基板10を用意する。半導体基板の前記第1の面11とは反対側の第2の面12において等方性エッチングを行い、第1内壁面を有する第1凹部を形成する。第1凹部内から前記半導体基板を貫通して電極に至り、第2内壁面22aを有する第2凹部を形成する。第2の面と第1内壁面によって形成された第1の角部、及び第1内壁面と第2内壁面によって形成された第2の角部を除去するエッチバック処理を行い、第2の面と第2内壁面とを連続する第1内壁面を形成する。角部を除去した後、少なくとも第1内壁面、及び第2内壁面を覆うように、電極とオーバーラップする位置に開口部65を有する絶縁層30を形成する。絶縁層を介して第2凹部内に充填され、電極と接続し、かつ第2の面から突出する導電部40を形成する。

(もっと読む)

3DIC方法および装置

【解決手段】 切り分けられたダイまたはウェハのような素子を3次元的に集積する方法および切り分けられたダイまたはウェハのような素子が接続された集積構造。ダイまたはウェハの一方または両方は、その中に形成された半導体デバイスを有する。第1コンタクト構造を有する第1素子は、第2コンタクト構造を有する第2素子に接着される。第1、第2コンタクト構造は、接着の際に露出されることが可能で、また接着の結果、電気的に接続される。接着後にビアがエッチングされるとともに埋め込まれて電気的配線を露出および形成して第1、第2コンタクト構造を接続するとともに、この電気的配線への表面からの電気的なアクセスが可能になる。または、第1、第2コンタクト構造は接着の際に露出されず、接着後にビアがエッチングおよび埋め込みされて第1、第2コンタクト構造が電気的に接続されるとともに接続された第1、第2コンタクト構造への電気的なアクセスが得られる。 (もっと読む)

半導体集積回路装置

【課題】銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

(もっと読む)

半導体装置、半導体パッケージ、半導体装置の製造方法及び半導体パッケージの製造方法

【課題】電気的接続信頼性を向上させることができる半導体装置を提供する。

【解決手段】半導体チップ3は、第1主面30Aと第2主面30Bとの間を貫通する貫通孔30Xを有する半導体基板30と、半導体基板30の第2主面30Bを覆うように形成され、貫通孔30Xと対向する位置に開口部31Xが形成された絶縁層31と、絶縁膜33によって覆われた貫通孔30X及び開口部31Xに形成された貫通電極32とを有する。絶縁層31から露出される貫通電極32の上端面は、当該半導体チップ3に他の半導体チップ4が積層される際のパッドになる。また、貫通電極32の上端面は、絶縁層31の半導体基板30と接する面と反対側の面と面一になるように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】所定値以上の厚みを有するパッドを少ない工程数で形成することができる半導体装置の製造方法を提供すること。

【解決手段】本発明は、アルミ層22を、半導体基板上に形成された層間絶縁膜1の上方に堆積させる。アルミ層22上には、アルミ層24を堆積させる。パッド領域102のアルミ層24の上方に、フォトレジスト7を形成する。フォトレジスト7を用いてエッチングを行うことにより、パッド領域102にパッド上層52を形成するとともに、配線領域101のアルミ層24を除去する。そして、フォトレジスト8を、パッド領域102のパッド上層52を覆い、かつ、配線領域101で配線パターンを構成するように形成する。フォトレジスト8を用いてエッチングを行うことにより、パッド領域102にパッド下層51を形成するとともに、配線領域101に配線2を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

厚膜レジストの現像方法、及び半導体デバイスの製造方法

【課題】生産性を低下させることなく、基板の外周部にレジスト残渣が発生することを抑制可能な厚膜レジストの現像方法、及び半導体デバイスの製造方法を提供する。

【解決手段】回路素子層の上面に、厚膜レジストを形成する工程と、厚膜レジストを露光する工程と、露光後に、30〜50rpmの範囲内の一定の回転速度で炭化珪素基板を回転させながら、厚膜レジストの上方から現像液を供給することで、厚膜レジストの上面に現像液よりなるパドルを形成し、該パドルにより厚膜レジストを現像して、厚膜レジストに回路素子層の上面を露出する開口部を形成する工程と、を有する。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

貫通配線の検査方法、貫通配線基板の製造方法

【課題】1つの貫通配線のみの抵抗を測定できる貫通配線の検査方法、及び該貫通配線の検査方法を行う工程を含む貫通配線基板の製造方法の提供。

【解決手段】基板1の一方の面1aに配された導電部2と、基板1を貫通し、導電部2と接続される第一貫通配線3、第二貫通配線4および第三貫通配線5とを少なくとも備えた貫通配線基板10を用い、基板1の他方の面1b側から第一貫通配線3及び第二貫通配線4に、定電流源6の一組の端子6a,6bを電気的に接続して、第一貫通配線3、導電部2、第二貫通配線4の経路に電流を流すと同時に、基板1の他方の面1b側から第一貫通配線3及び第三貫通配線5に、電圧計7の一組の端子7a,7bを電気的に接続して、第一貫通配線3における電圧降下を測定することを特徴とする貫通配線の検査方法。

(もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

穿孔方法およびレーザー加工装置

【課題】第1の材料と第2の材料とが接続された被加工物に加工孔を効率よく形成することができる穿孔方法およびレーザー加工装置を提供する。

【解決手段】レーザー光線の照射によって発するプラズマのスペクトルが第1の材料から第2の材料に変化するまでのショット数を最小値として設定する最小ショット数設定工程、および第1の材料から完全に第2の材料に変化した時までのショット数を最大値として設定する最大ショット数設定工程とし、レーザー加工孔を形成する際に、ショット数が最小値に達しプラズマのスペクトルが第1の材料から第2の材料に変化した場合にはパルスレーザー光線の照射を停止し、ショット数が最小値に達してもプラズマのスペクトルが第1の材料から第2の材料に変化しない場合にはショット数が最大値に達するまでパルスレーザー光線の照射を継続した後に停止する。

(もっと読む)

電極構造、半導体素子、半導体装置、サーマルヘッドおよびサーマルプリンタ

【課題】シェア強度の向上した電極構造を提供する。

【解決手段】電極構造C1は、基体2と、基体2上に設けられた電極4と、電極4上に設けられためっき層14とを備え、めっき層14は、第1部位14aと、第1部位14a上に位置する第2部位14bとを有しており、平面視して、第1部位14aの面積が第2部位14bの面積よりも大きいことから、電極構造C1のシェア強度を向上させることができ、シェア強度の向上した電極構造を提供することができる。

(もっと読む)

半導体装置

【課題】パッド下のクラックによるショート不良が抑制された半導体装置を提供する。

【解決手段】パッド開口部18aの下の層間絶縁膜16はコンタクト17で囲われているので、ワイヤボンディング時に生じたパッド開口部18aの下の層間絶縁膜16のクラックはコンタクト17の外周縁17aよりも外側に入らない。よって、クラックを通し、パッド開口部18aは、外周縁17aよりも外側のアルミやポリシリコンなどの金属膜や拡散層とショートしない。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

半導体ウェハ及び半導体装置の製造方法

【課題】第1の溝への絶縁膜の埋設性が向上させて、埋設不良を軽減する。アライメントマークにおける埋設不良個所での応力集中がもたらす基板へのクラックを軽減する。

【解決手段】基板の第1の主面に、第1の溝、および前記第1の主面に対向して見た形状が環状となりかつ前記第1の溝よりも深い第2の溝を形成する工程と、第1の溝と第2の溝とを埋め込むように絶縁膜を形成する工程と、絶縁膜を形成する工程の後、基板の第1の主面にフォトレジスト膜を形成する工程と、絶縁膜で埋め込まれた第1の溝の基板上での位置を基準として位置合わせした第1のパターンをフォトレジスト膜に転写する工程と、絶縁膜で埋め込まれた環状の第2の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

41 - 60 / 1,972

[ Back to top ]