Fターム[5F033VV07]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ボンディングパッド、バンプ電極 (1,972)

Fターム[5F033VV07]に分類される特許

21 - 40 / 1,972

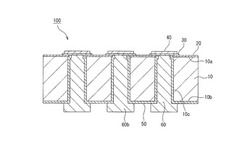

半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク不良の発生を抑制でき、かつ薄型基板を用いることができる半導体装置およびその製造方法を提供する。

【解決手段】半導体チップ30を、半導体基板35の表層部に形成された第1導電型層34と、第1導電型層34の表面に形成されたゲート絶縁膜37と、ゲート絶縁膜37上に形成されたゲート電極38と、半導体基板35の主表面35a上に配置され、主表面35aの一部を露出させるコンタクトホール42が形成された層間絶縁膜41と、層間絶縁膜41上に配置され、コンタクトホール42を介して半導体基板35と接続されるアルミニウムを有する材料で構成される上部電極43と、上部電極43上に形成されたニッケルを有する材料で構成されるメッキ膜44と、半導体基板35の裏面35bに形成された下部電極46とを有する構成とする。そして、上部電極43のうちコンタクトホール42に形成されている部分の膜厚tを2μm以上にする。

(もっと読む)

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを用いた実装における端子間のショートや実装精度の低下を防止する。

【解決手段】半導体チップ88の貫通ビア86の上に、他の半導体チップ101を実装する。半導体チップ101のバンプ103は、4つの貫通ビア86で囲まれた領域に導かれて接合される。各貫通ビア86は、バンプ103に面する側面及び上面の保護膜31がエッチングによって除去されており、バンプ103のハンダ材料への濡れ性が保護膜31で覆われた領域よりも良好になっている。このために、ハンダ材料のはみ出しによる他の電極との間のショートが防止される。さらに、1つのバンプ103に複数の貫通ビア86からなる接続端子を配置するので、バンプ103に確実に接合できる。

(もっと読む)

積層半導体基板、半導体基板および積層チップパッケージ並びにこれらの製造方法

【課題】単位時間あたりに製造できる積層チップパッケージの個数を増やして積層チップパッケージの製造コストを低減する。

【解決手段】積層半導体基板100は、複数の半導体基板1が積層されている。各半導体基板1はスクライブラインに沿った複数のスクライブ溝部20,21が形成されている。また、各半導体基板1は半導体装置が形成され、それぞれ絶縁されている複数のデバイス領域10と、複数のデバイス領域10のそれぞれに形成されている半導体装置に接続され、かつデバイス領域10からスクライブ溝部20,21の内側に延出している複数の配線電極15とを有している。複数の配線電極15は部分配置パターンで配置され、スクライブ溝部20,21を挟んで隣り合う2つのデバイス領域10のうちのいずれか一方だけから延出している。

(もっと読む)

半導体装置およびその試験方法

【課題】ワイヤボンディング時のストレスでボンディングパッド下の絶縁層のダメージを電気的に検出できる半導体装置および導入されたダメージを検出して良品、不良品を判定できる半導体装置の試験方法を提供すること。

【解決手段】酸化膜4上にポリシリコン5を配置し、このポリシリコン5にpnダイオード9を形成し、nカソード層6上に層間絶縁膜10を挟んで第1ボンディングパッド11を配置する。また、pアノード層7上に第2ボンディングパッド12を配設することで、層間絶縁膜10に導入されるダメージが層間絶縁膜10を貫通するか否かを電気的に検出できる半導体装置(パワーICなど)とすることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】クラックの発生を抑制できるとともに、SOG膜の剥離を抑えることが可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された半導体基板3上に、SOG膜を含む層間絶縁膜10が形成されており、この層間絶縁膜10を介して、配線層12a〜12dが半導体素子と電気的に接続されている。さらに、一方面側がボンディング接続されるパッド部12d(第4配線層12d)と、層間絶縁膜10に配置されると共に配線層12a〜12cを接続するビアホール15a〜15cと、ビアホール15a〜15c内に埋め込まれる導電層16a、16bとを有している。そして、ビアホール15a〜15cは、パッド部12dよりも下方に設けられており、導電層16a、16bの少なくとも一部は、内部に空洞部17を有している。

(もっと読む)

配線構造およびその製造方法

【課題】複雑な配線構造であっても、電極パターン同士を簡単な構造で接続できると共に、配線パターンの強度をも確保できるような配線構造、およびこうした配線構造を製造するための有用な方法を提供する。

【解決手段】本発明の配線構造は、基板上に形成された少なくとも第1の配線パターンと第2の配線パターンを有する配線構造であって、前記第1の配線パターンと第2の配線パターンとの間は、金属ワイヤーによる空中配線部によって接続されると共に、少なくとも金属ワイヤー表面には、金属ワイヤーと同じ若しくは異なる素材からなる金属めっきが施されたものである。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】外部からの不純物等に対する耐性を向上することができる半導体装置及びその製造方法を得る。

【解決手段】GaAs基板1上に下層配線2が設けられている。GaAs基板1及び下層配線2上に樹脂膜4が設けられている。樹脂膜4は、下層配線2上に開口5を有する。下層配線2及び樹脂膜4上にSiN膜6が設けられている。SiN膜6は、開口5内に開口7を有する。下層配線2及び樹脂膜4の一部上に上層配線8が設けられている。上層配線8は、開口5,7を介して下層配線2に接続されたTi膜8aと、Ti膜8a上に設けられたAu膜8bとを有する。上層配線8及び樹脂膜4上にSiN膜9が設けられている。SiN膜9は、樹脂膜4上においてSiN膜6に付着している。SiN膜6,9はTi膜8aの周囲を保護する。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置

【課題】高温環境下で使用することができる半導体装置を提供する。

【解決手段】第1インナー電極と第2インナー電極との積層からなるワイヤー接続領域を合金化防止溝によって第1アウター電極および第2アウター電極と分離することでワイヤーボンディング界面から成長したAu−Al合金層の進行を抑制し、半導体装置表面のパッシベーション膜のクラックを防止する。

(もっと読む)

半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法

【課題】本発明は、半導体ウエハの検査において、半導体ウエハの裏面電極の端子としての機能を維持しつつ、半導体ウエハに過度の力がかかることを防止できる半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法を提供することを目的とする。

【解決手段】本発明に係る半導体ウエハは、ダイシングラインを隔てて複数のチップが並ぶ半導体ウエハの表面側に形成された表面電極と、該半導体ウエハの裏面側に、該ダイシングラインを隔てて形成された複数の裏面電極と、該半導体ウエハの裏面側に、該ダイシングラインを跨いで該複数の裏面電極を電気的に接続する接続パターンと、を備える。該複数の裏面電極のうちの少なくともひとつは、該半導体ウエハのバイアホールを介して該表面電極と電気的に接続される。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

(もっと読む)

半導体装置の製造方法

【課題】切削又は研削加工を用いつつ、低コストで金属電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板12の主面12aに下地電極14を形成する工程と、下地電極を覆う保護膜16を形成するとともに、該保護膜に下地電極を露出させる開口部16aを形成する工程と、保護膜及び開口部から臨む下地電極の表面を覆うように第1金属膜22を形成する工程と、第1金属膜が形成された半導体基板を、裏面12bを搭載面として吸着ステージ30に吸着固定した状態で、吸着ステージと平行に設定された基準面上P1に位置する保護膜の部分及び第1金属膜の部分を、切削により除去して、第1金属膜をパターニングする工程と、パターニング工程後、裏面から半導体基板を研削し、半導体基板の厚さを所定厚さまで薄くする工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

(もっと読む)

21 - 40 / 1,972

[ Back to top ]