Fターム[5F033VV07]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ボンディングパッド、バンプ電極 (1,972)

Fターム[5F033VV07]に分類される特許

61 - 80 / 1,972

半導体ウェハ及び半導体装置の製造方法

【課題】第1の溝への絶縁膜の埋設性が向上させて、埋設不良を軽減する。アライメントマークにおける埋設不良個所での応力集中がもたらす基板へのクラックを軽減する。

【解決手段】基板の第1の主面に、第1の溝、および前記第1の主面に対向して見た形状が環状となりかつ前記第1の溝よりも深い第2の溝を形成する工程と、第1の溝と第2の溝とを埋め込むように絶縁膜を形成する工程と、絶縁膜を形成する工程の後、基板の第1の主面にフォトレジスト膜を形成する工程と、絶縁膜で埋め込まれた第1の溝の基板上での位置を基準として位置合わせした第1のパターンをフォトレジスト膜に転写する工程と、絶縁膜で埋め込まれた環状の第2の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】フリップチップ実装に用いられる半導体チップと実装基板との電気的な接続信頼性を向上させた半導体装置を提供する。

【解決手段】半導体チップ2と、半導体チップ2の主面に配置された複数の電極パッドと、複数の電極パッドの上に配置された複数のバンプ5とを有し、半導体チップ2のコーナー部において、第1のバンプと第2のバンプとが、第1のピッチで、隣接して配置され、半導体チップの中心部において、第3のバンプと第4のバンプとが、第2のピッチで、隣接して配置され、第1のピッチは、第2のピッチよりも狭い。

(もっと読む)

相互接続構造体及びその形成方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置および基板

【課題】アライメントマークを用いて形成される半導体装置であり、ダイシングおよびクラックに起因する半導体チップの品質低下を抑制し、半導体チップの微細化を容易にすることが可能な構成を有する半導体装置および基板を提供する。

【解決手段】主表面を有する半導体基板と、半導体基板の一方の主表面上に形成された多層構造回路ICと、多層構造回路ICのうち最上層と同一の層に形成される、平面視において多層構造回路を取り囲むように配置される保護壁GRと、最上層と同一の層に形成される位置合わせマークM2Bとを備える。上記位置合わせマークM2Bは少なくとも一部において保護壁GRと接するように形成される。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

集積回路構造及び裏面照射型イメージセンサデバイス

【課題】裏面照射(BSI)型イメージセンサチップのパッド構造を提供する。

【解決手段】前面及び背面を含む半導体基板、前記半導体基板の前記前面に配置される低k誘電体層、前記低k誘電体層に配置される非低k誘電体層、前記非低k誘電体層に配置される金属パッド、前記半導体基板の背面から延伸し、前記半導体基板、前記低k誘電体層、及び低k誘電体層を貫通し、前記金属パッドの表面を露出する開口、及び前記開口の側壁及び底部上に形成され、前記開口の底部は、前記金属パッドの前記露出された表面を部分的に覆う保護層を含む集積回路構造。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

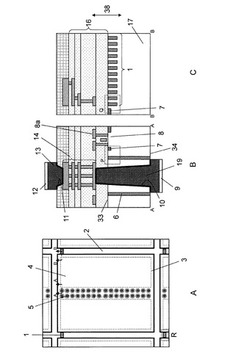

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

基板導通を利用した積重ねダイ式の構成をもつ集積回路

【課題】積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供すること。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

(もっと読む)

半導体発光素子

【課題】メタル電極に設けられた延伸部の表面を覆う絶縁膜の剥離が抑制された半導体素子を提供する。

【解決手段】半導体からなる活性層に積層されたn型またはp型の半導体層と、該半導体層の上に配置され接続部および延伸部を有するメタル電極と、該メタル電極の該延伸部の上面および側面を少なくとも覆う絶縁膜と、を備え、該延伸部はメタル多層膜で形成され、該メタル多層膜は少なくとも2層の第1メタル層と、該第1メタル層と交互に積層された第2メタル層とを含み、かつ、その最上層は該第2メタル層のひとつであり、該メタル多層膜に含まれる該最上層の第2メタル層以外の第2メタル層の各々の端面が該延伸部の側面に露出して該絶縁膜と接しており、該第2メタル層を構成する第2メタル材料は該第1メタル層を構成する第1メタル材料よりも導電率は低いが該第1メタル材料よりも該絶縁膜との密着強度に優れている。

(もっと読む)

半導体集積回路及びそれを備えた半導体装置、並びに電子機器

【課題】半導体集積回路において、ダイシング時の保護膜の剥離を抑制しつつ保護膜の密着性を確保し、チップサイズの小型化を実現する。

【解決手段】半導体集積回路は、スクライブ領域2近傍に形成されたシールリング3と、パッド4と、シールリング3とパッド4との間に形成された配線5と、シールリング3と、ダミーパターン8と、保護膜6と、保護膜7とを備えている。保護膜7の終端縁9は、シールリング3とパッド4との間に位置しており、ダミーパターン8における配線5を挟んで互いに向かい合う部分の端部が、保護膜7の終端縁9を中心に半導体チップ1の周縁部側及び中央部側方向に5μmの間隔以内に位置している。

(もっと読む)

半導体装置

【課題】半導体チップのバンプ電極と実装基板の配線との接続信頼性を向上できる技術を提供する。特に、バンプ電極下の最上層配線層に配線を配置しても、バンプ電極の平坦性を確保してバンプ電極とガラス基板に形成されている配線との接続信頼性を向上できる技術を提供する。

【解決手段】バンプ電極BP1の非重複領域Y直下にある最上層配線層に電源配線や信号配線からなる配線L1と、ダミーパターンDPを形成する。ダミーパターンDPは、配線L1間のスペースを埋めるように配置され、配線L1とスペースによって最上層配線層に生じる凹凸を緩和する。さらに、最上層配線層を覆うように形成される表面保護膜に対してCMP法による平坦化処理を実施する。

(もっと読む)

半導体装置の製造方法

【課題】生産性および信頼性を向上することができる半導体装置の製造方法を提供すること。

【解決手段】第一の接合工程では、半導体チップ10、第一樹脂層11、半導体チップ12、第二樹脂層13、半導体チップ14を積層することにより得られ、半導体チップ10,12同士、半導体チップ12,14同士が半田接合されていない状態の積層体2を加熱して、半導体チップ10,12間、半導体チップ12,14間の半田接合を行う。その後、半田接合した積層体2を基材18上に設置する。積層体2の基材18への接続用端子162と、基材18の積層体2への接続用端子181とが当接するように、積層体2を基材18上に設置する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】2枚の基板の貼り合わせによって電極間接合がなされた構成において、電極材料の拡散を防止しつつも貼り合わせ強度が確保され、これによって信頼性の向上が図られた三次元構造の半導体装置を提供する。

【解決手段】第1電極33、および第1電極33の拡散防止材料で構成され第1電極33の周囲を覆う第1絶縁膜35を含むと共に、第1電極33と第1絶縁膜35とで貼合せ面41が構成された第1基板2と、第1基板2に貼り合わせて設けられ、第1電極33に接合された第2電極67、および第2電極67の拡散防止材料で構成され第2電極67の周囲を覆う第2絶縁膜69を含むと共に、第2電極67と第2絶縁膜69とで第1基板2に対する貼合せ面71が構成された第2基板7とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】前記半導体装置をスクライブ工程により切り離す際に、クラックが歪みを蓄積した保護膜を伝播して半導体装置内部に侵入するのを抑制し、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記保護溝部の底面の一部及び前記保護溝部の内側の側壁面に連続して形成された保護膜と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】基板の側端部に由来する塵の発生を防止して、半導体装置の歩留まりを向上させる。

【解決手段】基板の少なくとも側端部を覆うように保護膜を形成する第1の工程と、フォトレジストパターンを用いたエッチングにより基板の第1の主面に第1の主面に対向して見た形状が環状となる溝を形成する第2の工程と、溝を埋め込むように絶縁膜を形成することにより、絶縁リングを形成する第3の工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】アンダーバリアメタルに起因する応力集中を緩和し、トランジスタの特性の変動を抑制することができるパッド電極構造を備える半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成された電極パッド6と、電極パッド6の上に形成され、且つ、電極パッド6の一部が露出するような第1開口部を有する第1絶縁膜7と、第1絶縁膜の上に形成され、且つ、第1開口部における少なくとも一部が露出するような第2開口部を有する第2絶縁膜8と、第2絶縁膜8及び電極パッド6の上に形成されたアンダーバリアメタル10とを備えている。アンダーバリアメタル10は、第2絶縁膜8の表面における第2開口部の外側である第1領域と電極パッド6の表面における第2開口部の内側である第2領域とにより挟まれる第3領域により分離されている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高アスペクト比の溝内にカバレッジ性良く絶縁膜を埋め込むと表面にスリット状の空孔が形成され、CMPで平坦化すると、CMPで用いた組成物や、研磨された除去物、その他の残渣が空孔内に残り易く、この残渣は後の工程での発塵の一原因となり得る。

【解決手段】基板1の第1の主面に、俯瞰形状が環状となる第1の溝部2Tを形成し、第1の主面全面に第1の絶縁膜2aを形成し、第1の絶縁膜2aの表面から前記第1の溝部の内部まで達する深さの空孔を残しつつ、前記第1の絶縁膜を第1の溝部に埋め込み、空孔内を埋め込むように第1の絶縁膜上に第2の絶縁膜を形成し、第1の溝部内に第1の絶縁膜および第2の絶縁膜を残しつつ、基板表面高さまで化学機械研磨法により平坦化する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜上に下地金属層と上部金属層からなる配線を備えた半導体装置において、下地金属層のサイドエッチングによる絶縁膜と上部金属層との密着性の劣化を抑制することができる半導体装置、及び、その製造方法を提供する。

【解決手段】配線本体16が形成される絶縁膜14の上面には、配線本体16のパターンに対応し、かつ、絶縁膜14の上面から所定の深さの凹部14aが設けられ、当該凹部14aを含む絶縁膜14上面に、配線の一部であり、かつ、密着層であるチタン薄膜15を介して配線本体16が設けられている。凹部14aの幅は、配線本体16の幅よりも狭くなるように設定される。チタン薄膜15は配線本体16の配線幅よりも狭く形成されている。

(もっと読む)

61 - 80 / 1,972

[ Back to top ]