Fターム[5F033XX09]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713) | コンタクト抵抗の低減 (898)

Fターム[5F033XX09]に分類される特許

201 - 220 / 898

現像液耐性に優れた表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ現像液耐性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で透明導電膜と直接接続されるAl合金膜であって、上記Al合金膜は、グループAに属するNiおよび/またはCoの元素を2.0原子%以下(0原子%を含まない)、並びにグループBに属する少なくとも一種の元素を0.05〜2.5原子%含み、上記グループBの元素はGd、Nd、La、Y、Sc、Pr、Dy、Ce、Ho、Er、Tb、Pm、Tm、Yb、Lu、Hf、Zr、Zn、Mg、Ti、Mn、およびGeから構成されている。

(もっと読む)

スパッタリングターゲット及びこれを利用して製造される半導体素子

【課題】スパッタリングターゲット及びこれを利用して製造される半導体素子を提供する。

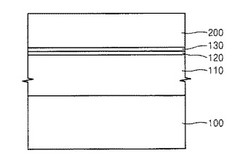

【解決手段】重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成されるスパッタリングターゲットであり、また、バリア層と、バリア層上のシード層と、シード層上の導電層と、を備え、導電層は、重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成される、タングステンとニッケルとの合金薄膜を備える半導体素子である。

(もっと読む)

電気的接続構造の製造方法

【課題】 低抵抗の電気的接続構造を提供する。

【解決手段】 ビアホールの底部の導電体上に導電性触媒担持体層を設け、予め微粒子化した触媒微粒子を当該導電性触媒担持体層上に堆積し、その後リフトオフ法により前記ビアホール底部以外の前記触媒粒子を除去して触媒微粒子層となし、当該触媒微粒子層上に炭素細長構造体を設ける電気的接続構造の製造方法において、前記触媒微粒子が、Co、Ni、Feからなる群から選ばれた金属の微粒子であること。

(もっと読む)

スパッタリングターゲット及び透明導電膜及び透明導電ガラス基板

【課題】 特定の金属を含有する透明導電材料を画素電極、透明電極に使用することにより、バリヤーメタル等を堆積するための工程が不要な簡略化されたTFT(薄膜トランジスタ)基板の製造方法を提供することである。

【解決手段】 酸化インジウムを主成分とし、W、Mo、Nb、Ni、Pt、Pdからなる第1金属群M1から選ばれた1種又は2種以上の金属又はその金属の酸化物と、ランタノイド系金属からなる第2金属群M2から選ばれた1種又は2種以上の金属の酸化物と、を含むスパッタリングターゲットを利用して、透明導電膜を作製する。この透明導電膜を画素電極として利用することによって、ソース電極7等との接触抵抗を小さく抑えることができる。更に、バリヤーメタル等を用いる必要がなくなったため、バリヤーメタル等を堆積する工程をなくすことができ、TFT基板の製造工程が簡略化される。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

表示デバイスおよびその製法

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供する。

【解決手段】基板上に配置された薄膜トランジスタと、透明電極によって形成された透明導電膜、および、これら薄膜トランジスタと透明導電膜を電気的に接続するアルミニウム合金膜を有し、該アルミニウム合金膜と前記透明導電膜の界面には該アルミニウム合金の酸化皮膜が形成されており、該酸化皮膜の膜厚が1〜10nmで、該酸化皮膜中の酸素含有量が44原子%以下である表示デバイスとその製法を開示する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

小臨界次元のタングステン接点装置及び相互接続子の製法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

基板のエッチング方法及びシステム

【課題】シリコンの表面上にシリコン酸化膜が形成された基板をエッチングする方法において、コンタクト抵抗を低くできるエッチング方法を提供する。

【解決手段】ハロゲン元素を含むガス、及び塩基性ガスを基板W上に供給し、シリコン酸化膜にハロゲン元素を含むガス及び塩基性ガスを化学反応させた凝縮層105を生成して、シリコン酸化膜104をエッチングする。F2ガス、XeF2ガス及びClF3ガスの群から選ばれる少なくとも一つを含むシリコンエッチングガスを基板W上に供給し、シリコンエッチングガスによって基板W上のシリコンをエッチングする。シリコン酸化膜104のエッチング及びシリコンのエッチングの後、基板W上の凝縮層105を加熱して除去する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は多層配線構造を有する半導体装置の製造方法に関し、高い集積度が要求される場合に優れた歩留まりと高い信頼性とを確保することを目的とする。

【解決手段】トランジスタのソースドレイン領域の上層にシリコン酸化膜7を形成する。一端面がソースドレイン領域6に導通し、他端面がシリコン酸化膜7の表面に露出するように、シリコン酸化膜7の内部に導電性のパッド10を設ける。シリコン酸化膜7およびパッド10の上層にシリコン酸化膜11を形成する。一端面がパッド10に接触し、他端面が配線層14と導通するようにシリコン酸化膜11の内部にプラグとして機能する導電層を設ける。シリコン酸化膜7の表面と、パッド10の他端面は平滑な同一平面を形成する。プラグとして機能する導電層は、パッド10に比して小さく、かつ、パッド10の中央部近傍に接触するように形成する。

(もっと読む)

表示装置用Al合金膜、薄膜トランジスタ基板および表示装置

【課題】Al合金膜とTFTの半導体層との間のバリアメタル層を省略可能な新規のSiダイレクトコンタクト技術を提供する。詳細には、Al合金膜をTFTの半導体層と直接接続しても、AlとSiの相互拡散を防止でき、良好なTFT特性が得られると共に、TFTの製造工程でAl合金膜に約100〜300℃の熱履歴が加わった場合でも、低い電気抵抗と優れた耐熱性が得られる新規なSiダイレクトコンタクト技術を提供する。

【解決手段】本発明の表示装置用Al合金膜は、表示装置の基板上で、薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、上記Al合金膜は、Geを0.1〜4原子%;La、GdおよびNdよりなる群から選ばれる少なくとも1種を0.1〜1原子%;並びにTa、Nb、Re、ZrおよびTiよりなる群から選ばれる少なくとも1種を含有する。

(もっと読む)

表示装置用Al合金膜、表示装置および該表示装置の製造方法、ならびにAl合金スパッタリングターゲット

【課題】表示装置(LCD)におけるパネルのTAB部引き出し電極の断線を防止することができ、かつ、バリアメタル層を介在させずにAl合金膜を透明画素電極と直接接続することのできるAl合金膜を提供する。

【解決手段】表示装置に用いられるAl合金膜であって、NiおよびCoよりなる群から選択される少なくとも1種の元素(X元素)を0.1〜2.0原子%含み、長径0.01μm超であってNi量とCo量の合計が10原子%以上である化合物が、100μm2あたり3個超析出していると共に、Al結晶粒内の固溶Ni量と固溶Co量の合計が0.1〜0.5原子%であり、かつ、Al合金膜の硬度が1.5GPa以上3.0GPa以下であるところに特徴を有する表示装置用Al合金膜。

(もっと読む)

Al−Ni系合金配線材料及びそれを用いた素子構造

【課題】ITOなどの透明電極層と直接接合が可能なAl系合金配線材料であって、現像液への耐食性に優れ、コンタクトホール形成時における耐食性にも優れ、大面積のガラス基板において素子を形成した場合においても、そのガラス基板面内に形成された素子の接合抵抗値をより均一にすることができるAl−Ni系合金配線材料を提供する。

【解決手段】アルミニウムにニッケルを含有したAl−Ni系合金配線材料において、セリウムとボロンとを含有し、各濃度は、ニッケル含有量をニッケルの原子百分率Xat%とし、セリウム含有量をセリウムの原子百分率Yat%とし、ボロン含有量をボロンの原子百分率Zat%とした場合、式0.5≦X≦5.0、0.01≦Y≦1.0、0.01≦Z≦1.0の各式を満足する領域の範囲内にある。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

半導体装置及びその製造方法

【課題】加工マージンの大きい半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、主面を有する半導体基板と、半導体基板上に形成された第1絶縁膜と、第1絶縁膜に形成された複数のコンタクト孔と、複数のコンタクト孔内にそれぞれ形成された複数の第1コンタクトプラグと、第1絶縁膜上に形成され、該第1絶縁膜の複数の第1コンタクトプラグが形成された領域を含む所定領域を露出させる開口部を有する第2絶縁膜と、第1絶縁膜のうち開口部で露出した部分に形成され、半導体基板の主面に対して垂直方向に見て、開口部が形成されていない第1絶縁膜の上面の位置よりも低い上面の位置を有する凹部と、開口部を横切り、かつ複数の第1コンタクトプラグのそれぞれの上面に接続されるように、第1絶縁膜の凹部から第2絶縁膜の開口部を経て第2絶縁膜の上面にかけて形成された第2導電膜から成る複数の配線と、を有している。

(もっと読む)

半導体記憶装置

【課題】配線間の抵抗値を低減させる、クロスポイント型メモリセルを積層した多層構造の半導体記憶装置を提供する。

【解決手段】半導体基板1と、互いに交差する第1の配線WL及び第2の配線BL並びにこれら第1及び第2の配線の交差部で両配線間に接続されたメモリセルMCを有する1または複数のセルアレイ層MAと、セルアレイ層MAよりも下層の第1配線層M1に形成された第3の配線11と、セルアレイ層MAよりも上層の第2配線層M2に形成された第4の配線12と、第3の配線11及び第4の配線14を接続する積層方向に延びるコンタクト141〜144とを有する。第1配線層M1と第2配線層M2の間には、冗長配線層が形成される。冗長配線層には冗長配線131〜133が形成され、第3の配線11と冗長配線131〜133との間及び第4の配線12と冗長配線131〜133との間は、複数のコンタクト141〜144により接続される。

(もっと読む)

基板処理方法および基板処理装置

【課題】Cu表面の酸化銅の除去および層間絶縁膜に付着したCu含有物残渣の除去を効率良く確実に行うことができる基板処理方法を提供すること。

【解決手段】基板上のCu配線構造におけるCu表面の酸化銅膜および層間絶縁膜に付着したCu含有物残渣を有機酸含有ガスを用いて除去するにあたり、基板温度が相対的に低温の第1の温度になるように基板を加熱しつつ基板に有機酸ガスを含む処理ガスを供給してCu含有物残渣のエッチング除去を行う第1工程と、基板温度が前記第1の温度よりも高温の第2の温度になるように基板を加熱しつつ基板に有機酸ガスを含む処理ガスを供給して前記Cu表面の酸化銅膜を還元を主体とする反応により除去する第2工程とを行う。

(もっと読む)

三次元積層型半導体集積回路及びその製造方法

【課題】スルーシリコンビアの高密度化、製造歩留りの向上及び製造コストの低減を同時に実現する。

【解決手段】本発明の例に係る三次元積層型半導体集積回路は、同一方向を向いて互いに積み重ねられる第一及び第二チップC1,C2と、第一チップC1を構成する第一半導体基板21及び第二チップC2を構成する第二半導体基板21を貫通し、かつ、第一チップC1内に設けられる半導体素子に繋がる第一電極14を貫通するスルーシリコンビア13とを備える。第一及び第二チップC1,C2は、面で結合する。

(もっと読む)

201 - 220 / 898

[ Back to top ]