Fターム[5F033XX09]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713) | コンタクト抵抗の低減 (898)

Fターム[5F033XX09]に分類される特許

121 - 140 / 898

半導体装置及びその製造方法

【課題】ビアホール内のコンタクト材料としてカーボンナノチューブ(CNT)を用いつつ、ビア抵抗の低減及びプロセスの容易化をはかる。

【解決手段】配線層間のビアにCNTを用いた半導体装置であって、表面にCu配線17を有する基板上に設けられた層間絶縁膜19と、層間絶縁膜19に形成されCu配線17に接続されるビアホールと、ビアホール内に露出するCu配線17上に選択的に形成され、Cu配線17に対するバリアとなり、且つCNTの成長の助触媒となる第1の金属膜21と、ビアホール内の少なくとも第1の金属膜21上に形成された、CNTの成長の触媒となる第2の金属膜22と、第1及び第2の金属膜21,22が形成されたビアホール内に形成されたCNT23と、を備えた。

(もっと読む)

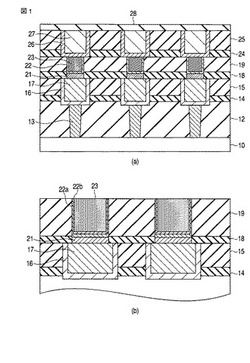

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

半導体装置

【課題】小型化が可能な半導体装置を提供する。

【解決手段】半導体装置において、第1の導電性材料からなる第1のコンタクトと、第2の導電性材料からなり、下端部が第1のコンタクトの上端部に接続された第2のコンタクトと、第3の導電性材料からなり、下面が第1のコンタクトの下面よりも上方に位置し、上面が第2のコンタクトの上面よりも下方に位置し、第1及び第2のコンタクトから離隔した中間配線と、を設ける。そして、第2の導電性材料に対する第1の導電性材料の拡散係数は、第2の導電性材料に対する第3の導電性材料の拡散係数よりも小さい。

(もっと読む)

電子デバイスの製造方法

【課題】カーボン膜の抵抗率を低減することができる電子デバイスの製造方法を提供する。

【解決手段】基板11が載置されたチャンバ4内に炭素を含有する原料ガスを供給する。基板11の周囲からチャンバ4内のアノード1に向けて電子を放出させてチャンバ4内にプラズマ14を発生させ、基板11上にグラファイト、グラフェン等のカーボン膜を形成する。

(もっと読む)

薄膜抵抗を備えた半導体装置の製造方法

【課題】薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供する。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

表示装置

【課題】TFTと接続するソース電極あるいはドレイン電極のスルーホールにおけるコンタクト抵抗を減少させ、表示装置の動作効率を向上させる。

【解決手段】スルーホールにおいて、TFTのソース部とソース電極8が接続している。ソース電極8は、バリヤメタル、Al合金82、キャップメタル83の3層から形成されている。バリヤメタルは半導体層と接触する下層81aとAl合金と接触する上層81bとに分かれている。バリヤメタルの下層81aをスパッタリングして形成した後、熱処理し、その後、ベースメタルの上層81b、Al合金82、キャップメタル83を連続してスパッタリングによって形成する。Al合金82と接触するバリヤメタルの上層81bは酸化されていないので、スルーホールにおけるコンタクト抵抗の上昇を防止することが出来る。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

半導体装置

【課題】電子回路の小型化を実現する。

【解決手段】MOSトランジスタ20が、格子状に形成されたゲート電極22と、ゲート電極22で囲まれたソース領域23およびドレイン領域24と、ゲート電極22の格子の一方向に沿って配置され、ソース領域23およびドレイン領域24とコンタクトを介して接続するソース用メタル配線27およびドレイン用メタル配線28を有する。ソース領域23およびドレイン領域24のそれぞれは、各メタル配線の長さ方向に長辺を有する長方形状に形成される。ソース用メタル配線27およびドレイン用メタル配線28は、その長さ方向にジグザグ形状に形成されて、それぞれソース用コンタクト25およびドレイン用コンタクト26に接続する。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁層のコンタクトホールに埋め込まれたコンタクトプラグを介して上層側の金属配線層と下層側の金属配線層とを電気的に接続する際の接続抵抗を低減する。

【解決手段】第2の層間絶縁層の上に少なくともコンタクトホールを形成する位置に開口部を有するレジスト層を形成する工程S1−4と、レジスト層を用いて第2の層間絶縁層をパターニングすることによって、第2の層間絶縁層を貫通するコンタクトホールを形成する工程S1−5と、コンタクトホールの内部に付着したポリマーを含む残渣をスチーム酸化によって除去する工程S1−7とを有する。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

電界効果型トランジスタ

【課題】電流許容値の低下を抑制する。

【解決手段】Y方向に沿って延在する延在ゲート電極G11と、Y方向に沿って延在するダミーゲート電極DM1と、Y方向に沿って延在する延在ソース電極S11と、Y方向に沿って延在する延在ドレイン電極D11とを含む。延在ソース電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。また、延在ドレイン電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。

(もっと読む)

基板処理方法及び記憶媒体

【課題】低誘電率膜であるSiCOH膜とCu配線との夫々の露出面に炭素の脱落したダメージ層及び酸化物が夫々形成された基板に対してダメージ層を回復させ且つ酸化物を還元すること。

【解決手段】SiCOHを含む層間絶縁膜4とCuを含む配線2との夫々の露出面に炭素の脱落したダメージ層15及び酸フッ化層16が夫々形成されたウエハWに対して、H2ガスの供給とシリコン及び炭素を含むTMSDMAガスの供給とを同一の処理容器51においてこの順番で連続して行うことによって、酸フッ化層16の還元処理及びダメージ層15の回復処理を行う。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

121 - 140 / 898

[ Back to top ]