Fターム[5F033XX09]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713) | コンタクト抵抗の低減 (898)

Fターム[5F033XX09]に分類される特許

41 - 60 / 898

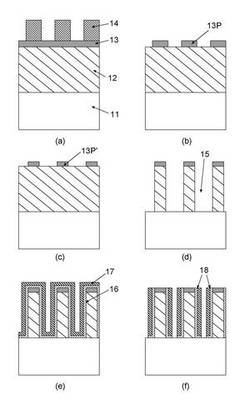

半導体集積回路装置及びその製造方法

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】実施形態によれば、ホールの深さのばらつきを防ぐ半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、複数の第1の開口と第1の開口よりも密に並んだ複数の第2の開口とを有するマスクを用いて層間絶縁層61をドライエッチングし、第1の開口の下で下地層10に達する第1のホールと、第2の開口の下で下地層10に達する第2のホール41とを同時に形成する工程を備えている。第1のホールは他の第1のホールとは接することなく下地層10に達する。ドライエッチングの開始後、複数の第2の開口のそれぞれの下に複数のホールhが形成され、ドライエッチングの進行に伴って、複数のホールhは少なくとも開口端を含む上部42で互いにつながる。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

41 - 60 / 898

[ Back to top ]