Fターム[5F033XX09]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 低抵抗化 (1,713) | コンタクト抵抗の低減 (898)

Fターム[5F033XX09]に分類される特許

81 - 100 / 898

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

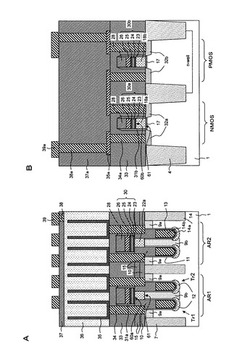

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】プローブ針の先端を研磨する時間を短縮することと接触抵抗を低く安定させること。

【解決手段】半導体基板上に形成された電子回路と、前記半導体基板上に形成され、前記電子回路と電気的に接続し、金属膜34と前記金属膜より硬い材料の層36とを備え、上視した場合前記層と前記金属膜とが配置された第1領域40と、前記金属膜が配置され前記層が形成されない第2領域42とを備えるパッド16と、を具備する半導体装置。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】透明導電膜にピンホール等の欠陥が生じたとしても金属導電膜の腐食を抑制し、透明導電膜と金属導電膜との間の導通を確実にとることが可能な薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】金属導電膜としてのゲート端子121、ドレイン端子122上にOC−SiN膜109を形成し、ゲート端子121及びドレイン端子122が露出するようにコンタクトホールを形成し、コンタクトホールを介してゲート端子121及びドレイン端子122に接触するようにITO膜を成膜してパターニングし、ITO膜に対して酸化膜形成処理を行う。これにより、ITO膜にピンホール等の欠陥が発生していた場合には、欠陥を介してITO膜下のゲート端子121ドレイン端子122の一部が酸化されて酸化膜が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】実施の形態の半導体装置は、シリコンを含む半導体基板10上の層間絶縁膜11に形成されたコンタクトホール12の底部14に形成され、コンタクトホール12に形成されるコンタクトプラグ21と電気的に接続するニッケルシリサイド膜18を有する。このニッケルシリサイド膜18は、ニッケルシリサイド膜18とコンタクトプラグ21の界面18aが半導体基板10と層間絶縁膜11の界面10aより高い。

(もっと読む)

半導体装置

【課題】本発明は、接続不良を抑制したコンタクト形成方法を備える半導体装置を提供するものである。

【解決手段】半導体装置は、配線層を備える第1の回路領域と、第1の回路領域の上に形成された絶縁膜と、絶縁膜の上に形成され、シリサイド膜を備える第2の回路領域と、配線層上に設けられ、配線層と電気的に接続された下部コンタクトと、下部コンタクト上に設けられ、下部コンタクトと前記シリサイド膜とを電気的に接続する上部コンタクトとを有する。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】

支持基板上に形成された第1導電層と、層間絶縁層上に形成された第2導電層とをコンタクトホールによって電気的に接続した半導体装置において、安価に、前記第1導電層と第2導電層とのコンタクト不良を抑制した半導体装置及びその製造方法を提供する。

【解決手段】

開口部内における第1導電層102の状態は、開口部端部付近102bよりも中心部付近102cにおいて表面粗さがより大きい、もしくは導電性は薄膜の粒径がより大きくなるように形成されている。従って、コンタクトホール104における第1導電層102と第2導電層105との電気的接続が良好となってコンタクト不良の発生を抑制可能としている。

(もっと読む)

エッチング方法、エッチングシステムおよびエッチング装置

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFガスおよび不活性ガスを用いたドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

配線構造体、半導体素子、配線基板、表示用パネル及び表示装置

【課題】 酸化物電極との良好な接続を行うことや、絶縁膜等との界面で生じる相互拡散を抑制することができ、かつ製造工程の低コスト化を図ることができる配線構造体、それを用いた半導体素子、配線基板、表示用パネル及び表示装置を提供する。

【解決手段】 アルミニウム層、銅層及び銅合金層からなる群より選択される少なくとも1つの層と、アルミニウム合金層とを含む2層以上の積層体であり、該アルミニウム合金層が表層に配置されている配線構造体である。これにより、液晶表示装置等において、酸化物電極と配線との接続部で酸化膜が形成されず、良好な接続を行うことができる。

(もっと読む)

半導体装置およびその製法

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を提供する。またこのような半導体装置の作製方法を提供する。

【解決手段】半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこのように作製したコンタクトを用いて半導体装置を作製すればよい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上部拡散層が平面積の狭いものであっても、上部拡散層および上部拡散層上に設けられた配線とのコンタクト抵抗を大きくすることなく、上部拡散層と配線とを接続できる半導体装置を提供する。

【解決手段】柱状半導体5と、柱状半導体5上に形成された上部拡散層15と、上部拡散層15上に形成された接続プラグ24とを備え、上部拡散層15が、平面視島状の複数の島状部を有するものであり、接続プラグ24が、導電材料からなり、前記複数の島状部から選ばれる第1島状部と前記第1島状部に隣接する第2島状部との間の隙間を跨って、前記第1島状部の上面の少なくとも一部から前記第2島状部の上面の少なくとも一部まで連続して配置されている半導体装置とする。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

81 - 100 / 898

[ Back to top ]