Fターム[5F038AC14]の内容

Fターム[5F038AC14]の下位に属するFターム

Fターム[5F038AC14]に分類される特許

281 - 295 / 295

MISキャパシタおよびMISキャパシタ作成方法

【課題】 従来と同等の容量値を確保し、かつキャパシタからのリーク電流を低減させることで消費電力を抑制することのできるキャパシタを提供する。

【解決手段】 シリコン基板8が、一方の面の所定の領域に拡散領域7が形成され、キャパシタ10の下部電極を構成する。第1のメタル層2が、第1の電源配線VDDに接続され、キャパシタ10の上部電極を構成する。第2のメタル層6a、6bが、第2の電源配線GNDに接続され、シリコン基板8の拡散領域7が形成された面上に形成される。絶縁体から構成される酸化膜3が、第1のメタル層2とシリコン基板8の拡散領域7が形成された面との間に配置される。

(もっと読む)

シリサイド領域を有する半導体デバイスの製造方法

【課題】本発明は、半導体デバイスの製造方法及び半導体デバイスを含む集積回路の製造方法を提供する。

【解決手段】本発明の半導体デバイス(100)を製造する方法は、とりわけ、基板(110)上にゲート構造(120)を形成するステップオ、及びゲート構造(120)の近くの基板(110)にソース/ドレイン領域(190)を形成するステップを含む。本方法は、更に、ゲート構造(120)及び基板(110)をドライエッチングするステップ、及びゲート構造(120)及び基板(110)をドライエッチングするステップに続いて、ソース/ドレイン領域にフッ素を配置して、フッ化したソース/ドレインを形成するステップを含む。その後、本方法は、ゲート構造(120)とフッ化したソース/ドレインに金属スイサイド領域(510,520)を形成するステップを含む。

(もっと読む)

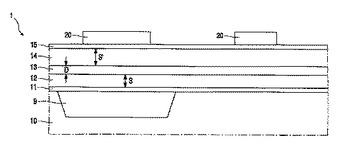

キャパシタ構造および半導体装置

【課題】MOSキャパシタの寄生容量を抑制する。

【解決手段】MOSキャパシタは、P型シリコン基板1の上面部に形成されたN型拡散領域2を下部電極とし、その上に形成されたゲート絶縁膜3を誘電体層とし、当該ゲート絶縁膜3の上に形成されたゲート電極4を上部電極としている。N型拡散領域2は、P型シリコン基板1に形成されたPウェル10の上部に形成される。N型拡散領域2とPウェル10との間に、N型拡散領域2よりも不純物濃度の低いN−型拡散領域11を設ける。

(もっと読む)

集積回路とキャパシタンス素子とを備える電子装置

電子装置(ICD)は、集積回路(AIC)とキャパシタンス素子(PIC)とを備えている。集積回路(AIC)には、複数の回路接点対(CI)が設けられている。キャパシタンス素子(PIC)には、複数のキャパシタンス接点対(CC)が設けられている。キャパシタンス接点対(CC)の少なくとも一部のそれぞれの間にはキャパシタンスが存在する。複数のキャパシタンス接点対(CC)は、複数の回路接点対(CI)と対向する。キャパシタンス接点対(CC)の少なくとも一部は、回路接点対(CI)の少なくとも一部に対して、対ごとに電気的に結合される。  (もっと読む)

(もっと読む)

半導体装置及びその設計方法

【課題】 半導体集積回路において、端子電極の後に積層され、素子の平坦化を担う金属層により、端子電極間のクロストークが生じる。

【解決手段】 回路素子の近接配置される端子電極20〜24に対応して、平坦化金属層に電極領域タイル30〜34を生成する。当該タイルは、たかだか1つの端子電極にしか重ならないように定められる。当該タイル30〜34とパターンルールによって他のタイルが排除される排他領域とからなる電極領域レイアウト70が得られる。この電極領域レイアウト70に、標準タイル72が二次元的に配列されたパターンを合成する。標準タイル72は、電極領域レイアウト72以外の部分に選択的に合成され、2つの端子電極に跨って配置されることが防止される。

(もっと読む)

シングルイベントアップセットに対する抵抗力を増加する集積回路構造

フィールドプログラマブルゲートアレイ(「FPGA」)の集積回路(「IC」)デバイスのコンフィギュレーション・メモリセル(「CRAM」)は、シングルイベントアップセット(「SEU」)に対する増加された抵抗力を与えられる。CRAMの入力ノードのゲート構造の一部分は、そのゲート構造の残りの部分の名目上のサイズに対して、サイズが増加される。拡大されたゲート構造の部位はICのNウェル領域に容量的に近くに配置され、別の部位はICのPウェル領域に容量的に近くに配置される。この配置は、その入力ノードのロジックレベルに関係なく、その入力ノードに、SEUに抵抗するための増加された静電容量を与える。本発明はまた、SEUへの抵抗力を増加させることが所望される任意のタイプのメモリセルの任意のノードに対しても応用可能である。  (もっと読む)

(もっと読む)

半導体装置

【課題】パッド部に流れる過電流が抑制されてパッド部におけるESD耐性が向上された半導体装置を提供する。

【解決手段】基板2上に第1の電位が与えられた第1のパッド8と、パッド8に電気的に接続された第1の導電層5が設けられている。基板2との間に少なくとも1層の第1の導電層5を挟んで第1の電位とは異なる第2の電位が与えられている第2のパッド13が設けられているとともに、少なくとも1層の第2の導電層10がパッド13に電気的に接続されてパッド8,13と基板2との間に設けられている。基板2上には、複数層の絶縁層4が積層されて設けられている。各絶縁層4は、パッド8および導電層5の少なくとも一方とパッド13および導電層10の少なくとも一方との間で容量絶縁膜となる。

(もっと読む)

半導体装置

【課題】 MOSキャパシタのゲート酸化膜の絶縁破壊を防止可能で回路面積の縮小が可能な半導体装置を提供する。

【解決手段】 高電位側の端子VDDにゲート(G)を接続したNMOSトランジスタ1と、低電位側の端子GNDにゲート(G)を接続したPMOSトランジスタ2とを有し、NMOSトランジスタ1のソースまたはドレイン(S/D)と、PMOSトランジスタ2のソースまたはドレイン(S/D)とを電気的に接続する。

(もっと読む)

電子装置

半導体材料の基板の第1の面上に少なくとも1つの薄膜キャパシタ及び少なくとも1つのインダクタの回路網を含む電子装置。前記基板は、前記インダクタの電気的損失を制限するのに十分に高い抵抗を有し、前記第1の面上の電気絶縁表面層を備える。 第1及び第2の横型PINダイオードは前記基板に画定され、前記PINダイオードが互いにp導電型領域、n導電型領域、及び中間真性領域を有する。前記第1のPINダイオードの前記真性領域は前記第2のPINダイオードの真性領域よりも大きい。  (もっと読む)

(もっと読む)

電圧発生回路と半導体集積回路装置

第1電流がエミッタに流れるようにされた第1トランジスタと、上記第1トランジスタよりも大きな電流密度となるような第2電流がエミッタに流れるようにされた第2トランジスタとのベース,エミッタ間の電圧差を第1抵抗に流して定電流を形成し、それと直列にして第2抵抗を回路の接地電位側に設け、上記第1トランジスタと第2トランジスタのコレクタと電源電圧との間に第3抵抗と第4抵抗とを設け、上記第1と第2トランジスタの両コレクタ電圧とCMOS構成の差動増幅回路に供給して、出力出力電圧を形成するとともに、かかる出力電圧を上記第1トランジスタと第2トランジスタのベースに共通に供給する。 (もっと読む)

キャパシタ

集積回路の中にキャパシタを作製する方法。本発明の基本形態にかかるキャパシタは、容量を増大させるために強いフリンジング電界を利用する。これは平面に平行な平板ではなくて、集積回路の中の2つの面の間に垂直な、重畳している導電性電極を持ったキャパシタを作製することによって達成される。本発明のキャパシタは水平な平板、すなわち平行な平板を付加的に備えていてもよい。本方法によるキャパシタも開示されている。  (もっと読む)

(もっと読む)

部分的シリサイド化シリコン層を有する集積回路

この集積回路(1)は、シリサイド化部(122)及び非シリサイド化部(123)を有する第1のシリコン層(120)を有する抵抗素子などの電気的装置(2)と、例えばキャパシタ、電界効果トランジスタ又は不揮発性メモリゲート堆積部などの他の電気的装置(3)とを有する。他の電気的装置(3)は、誘電層厚さ(D)を有する誘電層(130)を有する。電気的装置(2)の非シリサイド化部(123)は、誘電層厚さ(D)を有する他の誘電層(131)により被覆され、シリサイド化部(122)は、他の誘電層(131)により被覆されない。このような集積回路(1)は、リソグラフィ工程数の少ない本発明による方法によって形成可能となる。

(もっと読む)

(もっと読む)

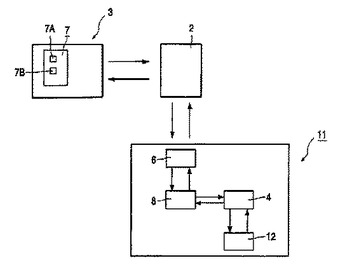

半導体デバイス、認証方法およびシステム

本発明の半導体デバイス(11)は回路と保護構造(50)とを備える。本発明の半導体デバイス(11)は、第1および第2のセキュリティ素子(12A、12B)と、入力および出力(14、15)とを備える。セキュリティ素子(12A、12B)は、異なる第1および第2のインピーダンスをそれぞれ有する。このデバイスはさらに、測定手段、処理手段および接続手段を備える。処理手段は、受け取られた第1の情報を特定の測定プログラムに変換する。これによって、デバイス(例えばスマートカード)のオーセンティシティをチェックし、またはアイデンティティを確立するために、デバイス(11)および読取り装置中にチャレンジ−レスポンス機構が実装される。  (もっと読む)

(もっと読む)

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

絶縁層及び接続孔の形成方法、配線構造及びその形成方法

【課題】 絶縁層及びヴィア形成において、形成された絶縁層の表面が非常に平滑となり、薄膜素子等を信頼性及び歩留り良く、高い自由度を以って形成でき、さらには微小なヴィア形成が可能である絶縁層及びヴィア(接続孔)の形成方法、及びそれを用いた多層配線基板並びにモジュール基板等の配線構造及びその形成方法を提供する。

【解決手段】 台座20を介してマスク基板21を配置し、この基板21とコア基板1との間に感光性エポキシ樹脂などの感光性絶縁材料3Aを介在させ、これをパターン露光して現像してヴィアホール7を形成する。この現像により、微小なヴィアホール7を形成できると同時に、マスク基板21のコア基板対向面21aによって絶縁材料(従って、絶縁層3)を平坦かつ滑らかな表面に、しかも常に設定された厚みに形成することができる。

(もっと読む)

281 - 295 / 295

[ Back to top ]