Fターム[5F038AC14]の内容

Fターム[5F038AC14]の下位に属するFターム

Fターム[5F038AC14]に分類される特許

121 - 140 / 295

半導体装置およびキャパシタの製造方法、成膜装置

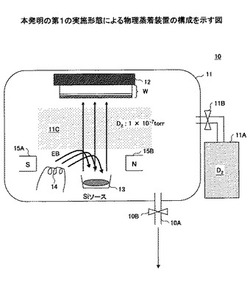

【課題】MOSトランジスタあるいはMIMキャパシタにおいて、導体膜からなる電極に、多量の重水素をドープすることにより、絶縁膜との界面の欠陥を終端し特性劣化を抑制する。

【解決手段】電子ビームEBによりシリコンソース13を加熱し、重水素ガス雰囲気中11Cにシリコン原子を放出することにより、シリコン膜を基板W上に堆積する。このシリコン膜はCVD法による堆積よりも高濃度に重水素ドープされ、ダングリングボンドなどの欠陥が重水素で終端されている。

(もっと読む)

半導体装置およびその製造方法

【課題】電源回路用の容量素子の平面寸法を縮小することにより、不揮発性メモリを混載する論理用半導体装置の低コスト化を図ることのできる技術を提供する。

【解決手段】選択用nMISのゲート絶縁膜または周辺回路のいずれかの電界効果トランジスタのゲート絶縁膜と同一層の絶縁膜を介して設けられた半導体基板の活性領域ACTと選択用nMISのゲート電極と同一層の導体膜からなる下部電極CGcbとの間で第1容量部を構成し、電荷蓄積層を含む多層構造の絶縁膜を介して設けられた下部電極CGcbとメモリ用nMISのゲート電極と同一層の導体膜からなる上部電極MGctとの間で第2容量部を構成し、第1容量部と第2容量部とを並列に接続することによって積層型容量素子C1を構成し、下部電極CGcb下の半導体基板の活性領域ACTに複数の容量素子用の溝1aを形成する。

(もっと読む)

半導体装置の製造方法

【課題】MIMキャパシタの下部電極加工時の酸化を防止する。

【解決手段】酸化量がアッシング時間に依存しない領域を用いて、金属が酸化しない酸素割合で生産上問題にならないアッシング速度を確保してレジスト除去を行う。MIMキャパシタの下部電極加工のレジスト膜アッシング工程において、バイアス無しで所定の温度で行う際の酸素ガスの割合が、第1の金属膜の酸化量がアッシングする時間に依存しない酸素の割合以下に設定する。

(もっと読む)

半導体装置

【課題】半導体基板の近くにインダクタが配置されるときにも、半導体基板の内部インダクタのインダクタンスに影響を与え難い半導体装置を提供する。

【解決手段】半導体基板2と、半導体基板2に形成される絶縁膜3と、絶縁膜3上に形成されるインダクタ7と、を備える半導体装置1にかかり、半導体基板2上には内部インダクタ9が形成され、内部インダクタ9と対向する場所には、インダクタ7が放出する磁力線を減衰させる内部用シールド膜5を有し、内部インダクタ9が内部用シールド膜5により変化するインダクタンスを補正する補正インダクタ6を有することを特徴とする。

(もっと読む)

半導体装置、及び発振器

【課題】Q値が高く、位相雑音特性が優れる半導体装置を提供する。

【解決手段】半導体装置1は、能動素子としての集積回路12と、集積回路12に電気的

に接続される複数の接続電極(14,15)とを含む半導体基板10と、半導体基板10

の接続電極14,15が形成される面に、接続電極14,15を避けて形成される第1の

樹脂層70と、半導体基板10と第1の樹脂層70の間に形成され、複数の接続電極のう

ちの一つに接続される接続配線層25,26と、接続配線層25,26に一端が接続され

、第1の樹脂層の表面に形成されるCu配線層からなる渦巻き形状のスパイラルインダク

タ40,50と、スパイラルインダクタ40,50の表面を覆う第2の樹脂層75と、複

数の接続電極のいくつかと電気的に接続され、第2の樹脂層75から一部が突出してなる

外部端子81〜86と、を備える。

(もっと読む)

半導体装置

【課題】バックバイアス電圧の印加により、製造後においても特性を調整することができる受動素子を備えた半導体装置を提供する。

ゲート電極から電荷蓄積層に正孔を注入する不揮発性メモリにおいて、電荷保持特性を低下させることなく、正孔注入の高効率化を実現する。

【解決手段】支持基板1とBOX層2とSOI層3とからなるSOI基板の主面には、SOI層3の表面に形成されたゲート絶縁膜7と、ゲート絶縁膜7上に形成されたゲート電極8Cと、ゲート電極8Cの両側のSOI層3に形成されたn+型半導体領域17とを含むMOSバラクタQvが形成されている。MOSバラクタQvは、ゲート電極8Cの下部の支持基板1(p型ウエル6)にバイアス電圧を印加することによって、SOI層3とゲート絶縁膜7とゲート電極8Cとで形成される容量が変化するように構成されている。

(もっと読む)

半導体装置およびその設計方法

【課題】直流試験ではキャパシタやそれに接続される配線の切断によるキャパシタの予期しないオープンを検出できない。

【解決手段】半導体装置100は、第1配線層L1、第2配線層L2と、第1配線層L1、第2配線層L2の間に設けられた絶縁層L3と、を有する。キャパシタ2は、第1配線層L1に形成された第1電極10と、第1電極10とオーバーラップするよう第2配線層L2に形成された第2電極12と、を有する。第1電極10には、2つの接続用配線16a、16bが接続され、第2電極12にも2つの接続用配線18a、18bが接続される。接続用配線16a、16bの間は、実質的に第1電極10を介してのみ直流的に低インピーダンスで接続される。同様に2つの接続用配線18a、18b間は、実質的に第2電極12を介してのみ直流的に低インピーダンスで接続される。

(もっと読む)

半導体記憶装置、メモリ搭載LSI、及び半導体記憶装置の製造方法

【課題】半導体記憶装置やメモリ搭載LSIを、チップ面積増加によるチップ単価の増大を防止しつつ、メモリ容量が異なる種々の品種に容易に展開できて、各品種間の特性を均質にできるようにする。

【解決手段】複数のワード線と複数のビット線の各交差位置に行列状に配置された複数のメモリセル121を含んだメモリセルアレイ120が、1段以上積み上げられたメモリセルアレイブロック110を設ける。また、回路素子の構成がそれぞれ同じであり、前記回路素子の1つとしてMOSトランジスタを含む、複数のMOSトランジスタブロックを設ける。そして、前記複数のMOSトランジスタブロックのうちの一部は、前記MOSトランジスタ161が前記複数のワード線又は前記複数のビット線の駆動に使用し、その他のMOSトランジスタブロックの少なくとも一部は、前記MOSトランジスタ161がMOS容量素子として使用する。

(もっと読む)

電気回路素子およびその製造方法

【課題】誘電体層に新たな材料を用いる必要がなく、構造が単純で低コストのキャパシタを実現する。

【解決手段】基板1上に設けられた第1の樹脂層2と、第1の樹脂層2上に設けられた第1の配線層3と、第1の配線層3を覆い第1の樹脂層2上に設けられた第2の樹脂層4と、第2の樹脂層4上に設けられた第2の配線層5とを少なくとも備え、第1の配線層3および第2の配線層5がキャパシタを構成した電気回路素子とする。第1の配線層3または第2の配線層5の少なくとも一方が金属めっき層からなることが好ましい。

(もっと読む)

キャパシタとその製造方法及びキャパシタを備えるSOI基板

【課題】 キャパシタの耐圧を決定する絶縁膜に被覆されているとともに不純物を高濃度に含んでいる半導体領域に、重金属をゲッタリングされにくくする技術を提供する。

【解決手段】 キャパシタ100は、不純物を低濃度に含んでいる第1半導体領域12と、第1半導体領域12の表面に臨む範囲に形成されているとともに不純物を高濃度に含んでいる第2半導体領域8と、第2半導体領域8の表面の所定範囲を被覆している絶縁膜22と、第2半導体領域8に電気的に接続されている第1電極28と、絶縁膜22の表面に形成されているとともに絶縁膜22を介して第2半導体領域8に対向している第2電極24と、第1半導体領域12内に形成されているとともに第2半導体領域8のゲッタリング能力よりも高いゲッタリング能力を備えている第3半導体領域14備えている。

(もっと読む)

半導体集積回路装置、半導体集積回路装置用パターンの生成方法、半導体集積回路装置の製造方法、および半導体集積回路装置用パターン生成装置

【課題】有効に電源ノイズの吸収をはかり、回路の安定動作を実現することを目的とする。特にノイズ発生源のすぐ近くでノイズの吸収を行う。

【解決手段】少なくとも一つの回路ブロックを備えた半導体集積回路装置であって、前記回路ブロック上に第1の導体層1aと、前記第1の導体層1a上に容量絶縁膜1cを介して形成された第2の導体層1bとを具備してなるバイパスコンデンサを具備し、前記バイパスコンデンサの前記第1及び第2の導体層の一方は基板電位を固定する基板コンタクトを介してグランド配線または電源配線の一方に接続され、他方は電源配線またはグランド配線の残る一方に接続される。

(もっと読む)

半導体集積装置およびその検査方法

【課題】精度の高いキャパシタを有する半導体集積装置およびその検査方法を提供する。

【解決手段】キャパシタC1を有する機能回路14と、キャパシタC0を有する発振回路15と、制御信号Vctrlに応じて、キャパシタC1を機能回路14から電気的に切り離すとともに、発振回路15のキャパシタC0に並列接続するスイッチング手段16と、発振回路15の発振出力RFoutを出力する出力部18とを具備する。発振回路15の発振周波数f0を求め、キャパシタC1がキャパシタC0に並列接続された後の発振回路15の発振周波数f1を求め、発振周波数f0と、発振周波数f1とから、キャパシタC1の容量を求める。

(もっと読む)

半導体設計装置および半導体回路

【課題】瞬時電流の発生による電源電圧の低下が懸念される領域に空き領域がなくても、既配置セルを移動させることなく、電源配線に容量成分を付加し瞬時電流ノイズの発生を抑制することのできる半導体設計装置および半導体回路を提供する。

【解決手段】半導体設計装置1は、回路セルの配置配線終了後のレイアウトデータ100に対して、キャパシタ挿入位置決定部11が、瞬時電流の電流経路の解析にもとづいて瞬時電流発生による電源電圧の低下を防止するためのキャパシタの挿入位置を決定し、容量値算出部12が、そのキャパシタに必要とされる容量値を算出し、空き領域検出部13が、そのキャパシタの挿入位置周辺の空き領域を検出し、容量セル配置部14が、容量値算出部12により算出された容量値を満たす分の容量セルをその空き領域に配置し、配線部15が、配置された容量セルのキャパシタ端子とキャパシタ挿入位置の電源配線とを配線で接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】 絶縁破壊を起こすことなく安定的に所望の静電容量を示す微細化されたMIM型コンデンサを有する半導体装置及びその製造方法を提供する。

【解決手段】 P型基板11上に形成された素子分離膜12と、基板11上の素子分離膜12が形成されていない少なくとも2つの活性領域と、素子分離膜12上に下部電極15、電極間絶縁膜16、及び上部電極17がこの順に積層されて構成されるコンデンサ部と、を備え、前記活性領域が、基板11より高濃度のP型領域14a、14bと、基板11よりは高濃度で、P型領域14a、14bよりも領域面積の大きいN型領域13a、13bと、を有するとともに、両拡散領域は、相互に接続されるか、または両拡散領域よりも低濃度の不純物領域を介して離隔形成されることで保護ダイオードを形成しており、下部電極15がN型領域13bと接続され、上部電極17がN型領域13aと接続される。

(もっと読む)

金属絶縁体金属キャパシタの製造方法

【課題】半導体素子において、特に、金属絶縁体金属(MIM:metal−insulator−metal)キャパシタを製造する方法を提供する。

【解決手段】MIMキャパシタを持つ金属膜において、エッチング時に発生するブリッジによるエラーを熱処理により解決し、かつ、MIM構造の電極形成のためのエッチング時に発生する異常現象により後続の下部電極(Bottom Electrode)エッチング工程に誘発されるエラーを防止する。

(もっと読む)

MIMキャパシタ及びその製造方法

【課題】製造工程を改善することで製造効率を向上できるとともに、集積度を向上させることで半導体素子の価格を低下できるMIMキャパシタ及びその製造方法を提供する。

【解決手段】半導体基板110上に形成される下部金属層140と、下部金属層140上に形成される上部金属層160と、下部金属層140と上部金属層160との間に形成される誘電層150と、上部金属層160上に形成される第1ボンディングメタル層170及び下部金属層140上に形成される第2ボンディングメタル層180と、上部金属層160と第1ボンディングメタル層170との間に形成され、上部金属層160と第1ボンディングメタル層170とを直接接続させる第1接続配線172と、下部金属層140と第2ボンディングメタル層180との間に形成され、下部金属層140と第2ボンディングメタル層180とを直接接続させる第2接続配線182とを備えてMIMキャパシタ100を構成する。

(もっと読む)

半導体集積回路

【課題】スタンダードセルを用いた半導体集積回路設計において、電源ノイズ抑制効果を有し、電源安定化の実現が可能な半導体集積回路を提供する。

【解決手段】2つの基準となる電位を持ち、第1又は第2の電位を供給するための電源配線上のいずれか一方に電位固定された拡散領域とゲート電極の部分要素とを持つスタンダードセル604,605を2個1組で隣接して配置することで、ノイズ抑制及び電源安定化のための電源容量を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一半導体基板上にフォトダイオードとトランジスタとを混載した半導体装置の動作速度の更なる高速化と、フォトダイオードにおけるパルスの応答遅延の改善を図る。

【解決手段】第一導電型の半導体基板と、この半導体基板上に形成された第一導電型のエピタキシャル層と、第一導電型のエピタキシャル層上に形成された第二導電型のエピタキシャル層と、第一導電型のエピタキシャル層内に形成された第二導電型のコレクタ領域を有するトランジスタと、第一導電型のエピタキシャル層上に第二導電型の半導体領域を形成してなるフォトダイオードとを有する半導体装置において、コレクタ領域の下方における半導体基板表面の不純物濃度を、コレクタ領域と第一導電型のエピタキシャル層との接合により生じる空乏層の下端が半導体基板に達する不純物濃度とし、フォトダイオードの下方における半導体基板に、トラップ準位を形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】容量密度の電圧依存性が排除され、かつ、さらなる高容量化が図られた容量素子を備える、半導体装置およびその製造方法を提供する。

【解決手段】素子領域分離溝3により半導体素子形成領域16から分離される容量素子形成領域6には、N型ウェル7が形成され、このN型ウェル7内には、容量素子用溝9がシリコン基板2の表面から掘り下げて形成されている。容量素子用溝9の底面および側面に沿って、N型ウェル7の不純物濃度よりも高い不純物濃度を有する高濃度不純物拡散層10が形成されている。また、容量素子用溝9の底面上および側面上には、酸化シリコン膜からなる容量膜11が形成され、この容量膜11上には、ポリシリコン膜からなる上部電極12が形成されている。

(もっと読む)

半導体装置

【課題】パッケージング後であっても、端子容量を調整することができる半導体装置を提供する。

【解決手段】入出力回路10は、外部ピンと初段回路(入力バッファ200又は入出力バッファ300)間の信号配線に接続された端子容量調整回路100を備え、入力された命令をデコードし端子容量の調整のコマンドを検出するコマンドデコーダ20と、端子容量を制御するための情報を保持する端子容量調整レジスタ400を有し端子容量調整レジスタ400の情報を基に、端子容量調整回路100の容量値を制御する端子容量制御回路30を備え、コマンドデコーダ20からの出力に基づき、端子容量調整レジスタ400で保持する前記情報が設定される。

(もっと読む)

121 - 140 / 295

[ Back to top ]