Fターム[5F038AZ04]の内容

Fターム[5F038AZ04]の下位に属するFターム

等価インダクタンス回路 (48)

寄生インダクタンス (138)

Fターム[5F038AZ04]に分類される特許

1 - 20 / 612

可変インダクタ

三次元配置部品を有する化合物半導体集積回路

半導体装置

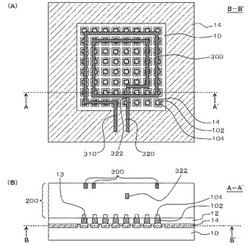

【課題】インダクタの下方に位置する素子分離膜に開口を設けてその開口内に半導体基板を残しつつ、インダクタの下方に位置する半導体基板に渦電流が発生することを抑制する。

【解決手段】インダクタ300は、多層配線層200に形成されており、素子分離膜12の上方に位置している。開口13は、素子分離膜12のうち少なくとも平面視でインダクタ300と重なる領域に形成されている。また、素子分離膜12とインダクタ300の間に位置するいずれの層にも、インダクタ300と半導体基板10の間をシールドするシールド導電部材は形成されていない。

(もっと読む)

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

半導体装置

【課題】半導体基板の上方にコイルが設けられた半導体装置において、コイル直下の半導体基板に回路を形成することができる半導体装置を提供する。

【解決手段】半導体装置は、一面11を有する半導体基板10と、半導体基板10の一面11に形成された絶縁層20と、絶縁層20の上方に形成されたコイル30と、を備えて構成されており、半導体基板10はコイル30の直下にスリット12を備えている。このスリット12は、コイル30のうち、半導体基板10の一面11に平行な面方向のうちの一方向に沿って形成された部分の直下に位置している。これにより、スリット12を境界として半導体基板10の渦電流面積が小さくなるので、半導体基板10に発生する渦電流による損失が低減し、コイル30の下部に位置する半導体基板10に回路を形成することが可能となる。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置

【課題】スパイラルインダクタを有する半導体装置における寄生容量の低減と、Q値の低下を抑制すること。

【解決手段】半導体基板と、前記半導体基板の表面近傍に設けられた複数個の素子分離領域と、前記素子分離領域間の半導体基板上に設けられた能動素子部と、基板上に積層された複数の配線層と、前記素子分離領域のうち第1の素子分離領域の鉛直上方であって、かつ、前記配線層のうち少なくとも最上の配線層に設けられたスパイラルインダクタとを備え、前記スパイラルインダクタが形成されたインダクタ形成領域の鉛直下方であって、かつ、前記第1の素子分離領域の半導体基板表面上にシリサイド形成防止膜が形成されていることを特徴とする半導体装置。

(もっと読む)

配線構造およびその製造方法

【課題】複雑な配線構造であっても、電極パターン同士を簡単な構造で接続できると共に、配線パターンの強度をも確保できるような配線構造、およびこうした配線構造を製造するための有用な方法を提供する。

【解決手段】本発明の配線構造は、基板上に形成された少なくとも第1の配線パターンと第2の配線パターンを有する配線構造であって、前記第1の配線パターンと第2の配線パターンとの間は、金属ワイヤーによる空中配線部によって接続されると共に、少なくとも金属ワイヤー表面には、金属ワイヤーと同じ若しくは異なる素材からなる金属めっきが施されたものである。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

電磁波干渉フィルタ

【課題】小型化が可能な電磁波干渉フィルタを提供すること。

【解決手段】実施形態に係る電磁波干渉フィルタ10は、半導体基板11の表面上に形成された抵抗R、およびこの抵抗Rの両端にそれぞれ電気的に接続された一対のキャパシタC、をそれぞれ具備する複数の電磁波干渉フィルタ回路12と、これらの電磁波干渉フィルタ回路12間の半導体基板11に埋め込み形成された素子分離層13と、を具備する。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

受光デバイス、これを用いた光受信機、及び受光デバイスの製造方法

【課題】 従来のPD製造プロセスと同じ工程で大受光径PDの帯域を拡大して、光受信部の高速化を図る。

【解決手段】 受光デバイスは、半導体基板の上方に形成された第1導電型の第1半導体層、前記第1半導体層上の光吸収層、および前記光吸収層上の第2導電型の第2半導体層の積層構造を有する光検出素子と、前記半導体基板の上方で、前記光検出素子に接続されるインダクタと、前記光検出素子で生成された電流を前記インダクタを介して取り出す出力電極と、前記光検出素子にバイアス電極を印加するバイアス印加用電極と、前記インタダクタの金属配線と交差して、前記光検出素子と、前記出力電極又は前記バイアス印加用電極との間を電気的に接続する交差配線と、を含む。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

半導体装置

【課題】コイル状のアンテナ部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給することが困難になっていた。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高周波配線を含む半導体装置において、エロージョンやディッシングを効果的に防いで半導体装置を安定的に製造するとともに、高周波配線への周囲のダミーメタルからの影響を低減して特性を向上させる。

【解決手段】半導体装置100は、半導体基板上の多層配線層中に設けられた高周波配線102と、多層配線層中の半導体基板と高周波配線102が設けられた層との間の第2の配線層122bに設けられたダミーメタル104とを含む。ダミーメタル104は、平面視で、高周波配線102の外縁で囲まれる第1の領域106とその周囲の第2の領域108とを含む高周波配線近傍領域110と、それ以外の外部領域112とにそれぞれ分散配置され、高周波配線近傍領域110のダミーメタル104間の平均間隔が、外部領域112のダミーメタル104間の平均間隔よりも広い。

(もっと読む)

1 - 20 / 612

[ Back to top ]