Fターム[5F038BH13]の内容

Fターム[5F038BH13]に分類される特許

41 - 60 / 1,330

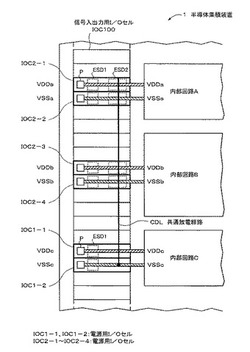

半導体集積装置

【課題】共通放電経路との間の異種電源間ESD保護回路をそれぞれの電源のパッドの近くに配置することのできる半導体集積装置を提供する。

【解決手段】実施形態の半導体集積装置1は、パッドPと、自己電源用ESD保護回路ESD1とを有し、VDDc系統の電源供給に使用の電源用I/OセルIOC1と、パッドPと、自己電源用ESD保護回路ESD1と、異種電源間ESD保護回路ESD2とを有し、VDDa、VDDb系統の電源供給に使用の電源用I/OセルIOC2とを備える。信号入出力用I/OセルIOC100と同一外形寸法の電源用I/OセルIOC1およびIOC2が、列状に配置されたIOC100と同列に配置され、電源用I/OセルIOC2の異種電源間ESD保護回路ESD2へ接続される共通放電経路CDLが、電源用I/OセルIOC1から、列状に配置されたIOC100を貫通して、電源用I/OセルIOC2へ配線される。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置

【課題】ESD耐圧が向上した半導体装置を提供する。

【解決手段】半導体装置は、電源パッドと、電源用配線を有する所定回路と、電源パッドと電源用配線とを接続する第1配線と、所定電位に設定された第2配線と、第1静電保護素子と、第2静電保護素子と、を含む。第1静電保護素子は、第1配線の電位が第1の閾値になった場合に、第1配線から第2配線への電流経路を形成する。第2静電保護素子は、電源用配線と第2配線との間に設けられ、第1配線の電位が第2の閾値になった場合に、電源用配線から第2配線への電流経路を形成する。

(もっと読む)

半導体装置

【課題】精度良く形成されたフィンを有しつつ、十分な特性を有するESD保護素子を形成することができる半導体装置を提供する。

【解決手段】実施形態にかかる半導体装置は、制御整流素子を有し、このシリコン制御整流素子は、半導体基板と、第1のウェル領域と、第2のウェル領域と、複数のフィン領域とを有する。第1のウェル領域は半導体基板の最外周に位置する。さらに、ウェルコンタクト領域よりも外周に位置し、第1の導電型の不純物拡散層領域を有し、且つ、電気的に浮遊状態にある最外周フィン領域を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

(もっと読む)

半導体集積回路

【課題】実装工程中のESD保護とともに、保護用トランジスタのオフリーク電流を低減する。

【解決手段】RCMOS型のESD保護回路において、RC構成の検出回路の出力を、電源配線2のサージを基準電圧配線3に流す保護用トランジスタ5のゲートに伝達するインバータ回路4内で、出力が上記ゲートに接続されたインバータを、電源配線と第3の電源線7との間に接続している。第3の電源線は実装時には、オープンで実装後には負電圧に接続する。

(もっと読む)

半導体装置

【課題】横型IGBTのコレクタ領域側にPN接合によりアバランシェダイオードをさらに設けることにより、ESD保護回路の面積および製造コストを減少させ、かつ、直流電流が重畳した場合にも素子破壊を防止するESD保護回路を含む半導体装置を提供する。

【解決手段】外部電圧を受ける第1のノードと、接地電圧を受ける第2のノードと、第1および第2のノードの間に並列に接続される保護回路および被保護素子を備え、保護回路は、エミッタが第2のノードに接続される横型IGBTと、アノードが横型IGBTのコレクタに接続され、カソードが第1のノードに接続されるアバランシェダイオードと、第1および第2のノードの間に接続され、横型IGBTのゲートに接続されるクランプ駆動回路とを含む。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

半導体集積回路およびその製造方法

【課題】半導体集積回路に電源を投入後の通常の動作時にリーク電流の抑制と同時にクランプ電圧の増大防止または低下を図り、保護用MOSトランジスタのゲート電位が変動しにくい保護回路を有する半導体集積回路及び製造方法を提供する。

【解決手段】RCMOS型のESD保護回路1において、保護用MOSトランジスタ5は、内部回路6の内のチャネルの導電型が同じトランジスタに対して、仕事関数差を有する異なる電極材料からゲート電極が形成され、または、仕事関数差を設けるために異なる導電型の半導体電極材料からゲート電極が形成されることによって、単位チャネル幅あたりのリーク電流量が、より減る向きに閾値電圧が異なっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

信号伝達装置および撮像表示システム

【課題】静電気からの保護をより確実に行うことが可能な信号伝達装置等を提供する。

【解決手段】信号伝達装置は、信号の入力動作および出力動作のうちの少なくとも一方の動作を行う複数の画素と、画素に接続された1または複数の信号線を含む複数の配線と、複数の配線のうちの一の信号線と他の一の配線との間に配設され、第1トランジスタおよび容量素子を有する1または複数の静電気保護回路と、静電気保護回路に接続された第1制御線とを備えている。静電気保護回路では、第1トランジスタのゲートが、第1制御線と直接もしくは間接的に接続され、第1トランジスタにおけるソースおよびドレインのうちの一方が、一の信号線および容量素子の一端に接続されると共に、他方が他の一の配線に接続され、容量素子の他端が、第1トランジスタのゲートに接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

保護回路

【課題】低圧回路10を保護しつつ、かつ、低圧回路10の動作を継続させる保護回路100を提供する。

【解決手段】PチャネルMOSトランジスタMP1は入力電源Vinと低圧回路10との間に設けられている。第1ツェナーダイオードZ1のカソードは、入力電源VinとPチャネルMOSトランジスタMP1のソースとの間に接続されている。第1ツェナーダイオードZ1のアノードは、分岐ノードN1で分岐され、一方は抵抗R1を介して接地されている。分岐ノードN1で分岐された他方は、PチャネルMOSトランジスタMP1のゲートに接続されている。第2ツェナーダイオードZ2のカソードは、低圧回路10とチャネルMOSトランジスタMP1のドレインとの間に接続されている。第2ツェナーダイオードZ2のアノードは、接地されている。

(もっと読む)

半導体集積回路

【課題】 本発明は、過電圧による破壊の回避手段をもつ半導体集積回路に関し、通常動作に悪影響を与えるのを避けつつ過電圧印加に対する保護を図る。

【解決手段】 第1の端子と入力部が接続している入力回路と、入力回路の出力部と接続する第1の手段と、入力回路と第2の端子との間に接続する第1のスイッチとをもち、上記第1のスイッチは、通常状態では入力回路と第2の端子との接続を維持し、過電圧の入力を検知すると接続を解除し、上記第1の手段は、第1の端子に過電圧が印加されると出力部の電位を上昇させ、入力部との電位差を小さくして入力回路の破壊を防止する。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かす

には、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上

においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層

103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層10

4aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170

aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導

体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可

能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

半導体装置

【課題】 ESD対策のための特別な工程や専用マスクを増やすことなく、ESD放電能力の向上を図る事が可能な半導体装置を実現する。

【解決手段】

基板上の所定の領域に、MOSFET構造のHVトランジスタ23と保護抵抗回路25からなる高耐圧用のESD保護素子21、及び、MOSFET構造のLVトランジスタ24と保護抵抗回路26からなる低耐圧用のESD保護素子22が形成されている。当該保護抵抗回路25(26)は、ゲート電極8b(8d)を挟んで互いに対抗するようにウェル2(3)の表層に分離形成される抵抗ドリフト領域16(17)の双方が、同導電型の低濃度ドリフト領域5c(5d)により電気的に接続されていることを除き、HVトランジスタ23(LVトランジスタ24)と同一の構造である。

(もっと読む)

41 - 60 / 1,330

[ Back to top ]