Fターム[5F038BH13]の内容

Fターム[5F038BH13]に分類される特許

21 - 40 / 1,330

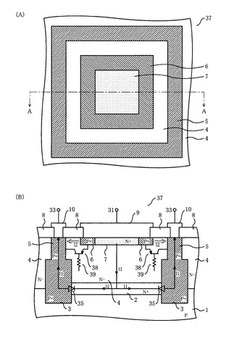

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

シミュレーション装置およびシミュレーション方法

【課題】ESD保護素子を有する半導体回路の回路シミュレーションを高速かつ精度よく行うことができるシミュレーション装置を提供する。

【解決手段】ESD保護素子を有する半導体回路の動作検証を行うシミュレーション装置は、ESD保護素子の等価回路のパラメータファイルを作成する第1のパラメータファイル作成部と、半導体回路内のESD保護素子以外の内部回路のパラメータファイルを作成する第2のパラメータファイル作成部と、作成したパラメータファイルを記憶するパラメータファイル記憶部と、記憶したパラメータファイルを選択するパラメータファイル選択部と、選択したパラメータファイルを利用して半導体回路のネットリストを作成するネットリスト作成部と、ネットリストに基づいて半導体回路の動作検証を行うシミュレーション実行部とを備える。

(もっと読む)

EMIフィルタ

【課題】EMIフィルタが形成された半導体素子の小型化を図る。

【解決手段】本発明の実施形態のEMIフィルタは、第1のダイオードD1、第1のキャパシタC1、及び抵抗体Rを備える。第1のダイオードは、第1の半導体層中に設けられ、上記第1の電極、上記第1の半導体層、その表面に形成されたn形の第2の半導体層2A、及びその表面上に形成された第2の電極11を有する。第1のキャパシタは、上記第1の半導体層1表面に形成され、上記第1の電極、上記第1の半導体層、その表面上に形成された第1の誘電体膜10A、及びその上に形成され第2の電極と電気的に接続された第3の電極12を有する。抵抗体は、第1の半導体層上に形成され、第1のダイオードの第2の電極と電気的に接続された第4の電極14を有する。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

低減したクランプ電圧を有するESD保護デバイス

【課題】寄生容量に悪影響を与えることなく、より低いクランプ電圧が達成できるESD保護回路を提供する。

【解決手段】ESD保護回路は、第1および第2端子(T1,T2)の間にある主要なESD電流伝導経路において、複数のバイポーラトランジスタ、即ち、複数のESD電流伝導トランジスタ(q1,q2,q4)を備え、ESD電流伝導トランジスタの少なくとも1つ(q1)と並列に接続され、ESDイベントの発生時に、ESD電流伝導トランジスタの1つ又はそれ以上(q2)に駆動電流(Ib2)を伝導するために設けられた少なくとも1つの駆動トランジスタ(q3)をさらに備える。

(もっと読む)

半導体集積回路及び保護回路

【課題】 より効率的にESDサージ電流を流すことができるESD保護回路を備える半導体集積回路を提供する。

【解決手段】 半導体集積回路100は、クランプMOSトランジスタ30と、第1トリガー回路部10と、第2トリガー回路部20と、内部回路2とを備える。第1トリガー回路部10は、出力端がクランプMOS30のゲートに接続され、クランプMOSトランジスタ30内のサージ電流のチャネル経路を開閉制御する。そして、第2トリガー回路部20は、出力端がクランプMOS30のウエルに接続され、クランプMOSトランジスタ30内のサージ電流のバイポーラ経路を開閉制御する。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体装置

【課題】パッド下のクラックによるショート不良が抑制された半導体装置を提供する。

【解決手段】パッド開口部18aの下の層間絶縁膜16はコンタクト17で囲われているので、ワイヤボンディング時に生じたパッド開口部18aの下の層間絶縁膜16のクラックはコンタクト17の外周縁17aよりも外側に入らない。よって、クラックを通し、パッド開口部18aは、外周縁17aよりも外側のアルミやポリシリコンなどの金属膜や拡散層とショートしない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

相互接続構造体及びその形成方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置

【課題】駆動用のスイッチ素子によって出力端子からの出力を制御する半導体装置において、端子に静電気が印加されたときに、スイッチ素子をより確実に保護し得る構成を、装置構成の大型化を抑えて実現する。

【解決手段】半導体装置1は、高電位側電源又は低電位側電源の一方からなる基準部にスイッチ素子の第1端子が接続され、出力端子P1にスイッチ素子の第2端子が接続されている。また、スイッチ素子と並列に第1保護素子が設けられている。また、基準部とは逆側の電源(他方部)と出力端子の間には第2保護素子が接続されている。そして、基準部とは逆側の電源(他方部)側には無効化手段が接続され、出力端子へのサージ電圧の印加によって駆動電圧が発生した場合に、当該駆動電圧の発生後の所定時間、制御入力端子への通電信号の入力を無効化し、所定時間の経過後に無効化を解除するように機能している。

(もっと読む)

半導体装置

【課題】異なる電源系統を含む半導体装置において、静電気による破壊から出力回路を保護する保護素子を備えた半導体装置の提供。

【解決手段】半導体装置は、第1の電源電圧と第1の接地電圧からなる第1の電源系統と、第2の電源電圧と第2の接地電圧からなる第2の電源系統と、第2の電源系統から電源供給を受ける出力回路と、第1の電源系統から電源供給を受け、出力回路を駆動する信号を出力する第1の駆動回路と、第1の接地電圧と第2の接地電圧との間に接続された第1の保護回路と、一端が、出力回路の出力ノードに接続され、他の一端が、第1の接地電圧に接続されている第1の保護素子と、を備えている。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

半導体素子の製造方法、ESD保護素子の製造方法

【課題】半導体ウエハに厚みばらつきがある前提で、コストアップをすることなく高品質の半導体素子を提供すること。

【解決手段】第1導電型の活性層の下に第1導電型の埋込拡散層を有する半導体基板を準備するステップと、活性層と埋込拡散層の総厚を測定し、測定した総厚から前記活性層の厚さを求めるステップと、活性層に、埋込拡散層との間で電流が流れる第1導電型のコレクタ領域をイオン注入によって形成するステップと、活性層に、埋込拡散層との間で電流が流れる第2導電型のベース領域をイオン注入によって形成するステップと、ベース領域内に、ベース領域との間で電流が流れる第1導電型のエミッタ領域をイオン注入によって形成するステップとを備え、ベース領域を形成するステップは、活性層の厚さに応じてイオン加速エネルギーを変化させるステップであることを特徴とする。

(もっと読む)

保護ダイオード及びこれを備えた半導体装置

【課題】PN接合容量が小さい保護ダイオード及びこれを備えた半導体装置を提供する。

【解決手段】

第1領域と当該第1領域を囲う第2領域と当該第2領域を囲う第3領域とを備える半導体基板と、当該第2領域と当該第3領域との間に設けられた第1絶縁層と、当該第3領域に設けられた第1導電型半導体と、当該第2領域に設けられた第2導電型半導体と、当該第1領域に設けられた容量緩和層と、を備えている保護ダイオード。当該保護ダイオードと、これに接続された第1のパッドと、当該容量緩和層を有しない構造の保護ダイオードと、これに接続された第2のパッドと、を備えている半導体装置。

(もっと読む)

21 - 40 / 1,330

[ Back to top ]