Fターム[5F038EZ02]の内容

Fターム[5F038EZ02]に分類される特許

61 - 80 / 547

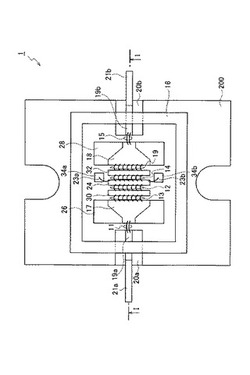

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かす

には、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上

においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層

103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層10

4aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170

aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導

体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可

能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、動的コンフィギュレーションにも対応可能なプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントを有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有する。複数のロジックエレメントそれぞれは、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更する。コンフィギュレーションメモリは、揮発性の記憶回路と、不揮発性の記憶回路との組を有し、不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子と、を有する。

(もっと読む)

電力増幅器

【課題】MMICとMMIC外部回路とを接続するボンディングワイヤの影響を比較的簡単な構成で低減し、かつ省スペース化された電力増幅器を提供する。

【解決手段】MMIC基板と、MMIC基板上に配置された高周波プローブパッドと、MMIC基板上に高周波プローブパッドに隣接して配置され、MMIC外部回路とのボンディングワイヤ接続用のメタルプレートとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタを備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い半導体装置を提供する。

【解決手段】半導体装置2は、半導体チップ10と、半導体チップ10の表面10Tに形成された電子回路と、半導体チップ10の少なくとも1つの側面10L、10Rに形成され、半導体チップ10側から内部電極21と絶縁膜22と外部電極23との積層構造を有するMIMキャパシタ20とを備えている。半導体装置2は、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に、第1の主電極Dswと第2の主電極Sswの間に配置された制御電極Gswを有するスイッチング素子Tswと、スイッチング素子Tswの第1の主電極Dswにアノード端子が接続された第1の整流素子D1、第1の整流素子D1のカソード端子に第1の主電極DD1が接続され、スイッチング素子Tswの制御電極Gswに第2の主電極SD1が接続された第1の駆動素子TD1、スイッチング素子Tswの制御電極Gswに第1の主電極DD2が接続され、スイッチング素子の第2の主電極Sswに第2の主電極SD2が接続された第2の駆動素子TD2、及び、第1の駆動素子TD1の制御電極GD1と第2の駆動素子TD2の制御電極GD2にそれぞれ入力される制御信号を受信する入力端子IN_H,IN_Lを有する駆動回路10とを備える。

(もっと読む)

キャパシタの形成とともに不揮発性メモリのゲートスタックをパターニングするための方法

【課題】キャパシタのエッチングはNVMセルのエッチングの終点検出に有用になるようにキャパシタおよびNVMセルを集積するように形成する。

【解決手段】NVM領域およびキャパシタ領域上に2つの導電体層を用いるように達成される。第1導電体層は後のパターニングステップの準備にパターニングされ、これが、NVM領域およびキャパシタ領域の両方に第1導電体層および第2導電体層の両方をパターニングするステップを含む。後のエッチングが、同一マスクを用いて両方の導電体層をエッチングされることによって制御ゲート上に浮遊ゲートの重要な配列を提供する。この後のエッチングの間、キャパシタ領域に第1導電体材料をエッチングされることが、NVM領域における第1導電体層のエッチングの終点検出を補助する。

(もっと読む)

低電圧デバイス保護付き高電圧複合半導体デバイス

【課題】低電圧デバイス保護付き高電圧複合半導体デバイスを提供する。

【解決手段】電圧保護されたデバイスを含複合半導体デバイスの1つの好適な実現では、ノーマリオフ複合半導体デバイス300が、第1出力キャパシタンス318を有するノーマリオンIII-窒化物パワートランジスタ310と、このノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイス320を具えて、このノーマリオフ複合半導体デバイスを形成し、このLVデバイスは第2出力キャパシタンス348を有する。第1出力キャパシタンス対第2出力キャパシタンスの比率を、ノーマリオンIII-窒化物パワートランジスタのドレイン電圧対LVデバイスの降伏電圧の比率に基づいて設定して、LVデバイスの電圧保護を行う。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

パワーモジュール

【課題】センス電流を抵抗で検出する場合であっても、カレントミラー回路を用いて検出する場合であっても、誤検出や電流検出精度の低下を起こさないパワーモジュールを提供する。

【解決手段】IGBT1の電流センス素子STのセンスエミッタにエミッタが接続されたトランジスタQ5と、トランジスタQ5のコレクタに一方端が接続され、他方端が共通接続部BPに接続された電流検出抵抗SRとを有し、トランジスタQ5のベースがGNDに接続された電流検出回路C3と、電流検出抵抗SRによって発生する共通接続部BPを基準とした電位差を電流検出電圧Vsとして検出し、所定の閾値電圧との比較を行い、両者の大小関係によってIGBT1に過電流が流れているか否かを判定する。

(もっと読む)

半導体回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)が高く、消費電力が少なく、端子数および配線数が少ない回路を提供する。

【解決手段】半導体回路は、複数個のNOT回路が縦続接続され、最終段のNOT回路の出力端子と初段のNOT回路の入力端子とが接続されている。NOT回路は、ゲート11とソース13とが一体構造で形成され、ゲート10が入力端子3に接続され、ドレイン12が出力端子5に接続され、ゲート11およびソース13がグランド端子6に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23が一体構造で形成され、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子4に接続された自己バイアス型インプレーントランジスター2とから構成される。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

定電圧回路とその半導体装置

【課題】 ツェナーダイオードと同等の動作を行える回路ないしは半導体装置を提供することを目的とする。

【解決手段】 実施形態の基準電圧発生回路は、第1のFETと、第2のFETと、一方を電源に接続し他方を前記第1のFETのドレインに接続した第1の抵抗と、前記第1のFETのドレイン−ゲート間に接続した第2の抵抗とを有し、前記第2のFETのゲート−ソース間を接続し、前記第2のFETのドレインを前記第1のFETのゲートに接続し、前記第1のFETのドレインが基準電圧を出力し、前記第1のFETのソースと前記第1のFETのソースがグランド又は他の回路と接続していることを特徴とする。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

コンデンサ及びその製造方法

【課題】金属−絶縁体−金属コンデンサや、内部接続構造の金属間誘電体として使用して、その素子や構造の平均故障寿命を改善できる誘電体構造を提供すること。

【解決手段】酸化膜層、誘電体材料層及び誘電体材料層の上に第2酸化膜層を有する、炭化ケイ素用のコンデンサ及び内部接続構造が提供される。酸化膜層の厚みは、酸化膜層と誘電体材料層の約0.5から約33パーセントであってよい。誘電体構造として酸窒化ケイ素層を有する炭化ケイ素用のコンデンサおよび内部接続構造もまた提供される。こうしたコンデンサ及び構造を作製する方法もまた提供される。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的小さい面積で形成することができ、かつ、素子サイズの微小化が進んでも保護素子として動作させることを可能にする、保護素子を提供する。

【解決手段】半導体基板1に形成された、第1導電型のウェル領域3と、この第1導電型のウェル領域3に隣接して形成された、第2導電型のウェル領域4と、第1導電型のウェル領域3に形成された、第2導電型チャネルのMOSトランジスタと、第1導電型のウェル領域3とMOSトランジスタのソース領域とMOSトランジスタのゲートとに電気的に接続された第1の配線と、MOSトランジスタのドレイン領域と第2導電型のウェル領域4とに電気的に接続された第2の配線とを含む保護素子を構成する。

(もっと読む)

61 - 80 / 547

[ Back to top ]