Fターム[5F038EZ02]の内容

Fターム[5F038EZ02]に分類される特許

21 - 40 / 547

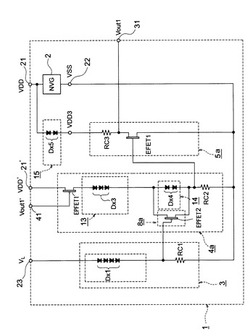

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

電力増幅器

【課題】本発明は、発振電力を吸収する抵抗の抵抗値を容易に制御できる電力増幅器を提供することを目的とする。

【解決手段】本願の発明に係る電力増幅器10は、複数のトランジスタセルが形成された半導体基板12と、該半導体基板上に形成された、該複数のトランジスタセルのドレイン電極40と、該半導体基板上に該ドレイン電極と接続されるように形成された、ドレインパッド42と、該半導体基板に、該ドレインパッドに沿って該ドレインパッドと接するように形成されたイオン注入抵抗44と、該半導体基板上に該イオン注入抵抗を介して該ドレインパッドと接するように形成されたフローティング電極46と、該半導体基板の外部に形成された出力整合回路16と、該ドレインパッドと該出力整合回路を接続する配線18a,18b,18c,18dと、を備える。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

ネスト化複合スイッチ

【課題】高いスイッチング速度及び低いオン状態抵抗を有し、電圧降伏耐性を強化したネスト化複合スイッチを提供する。

【解決手段】ネスト化複合スイッチ240は、複合スイッチに結合されたノーマリオン・プライマリ・トランジスタを含む。複合スイッチは、中間型トランジスタ222とカスコード接続された低電圧(LV)トランジスタ224を含み、中間型トランジスタは、LVトランジスタよりは大きく、ノーマリオン・プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、ノーマリオン・プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVトランジスタはIV族LVトランジスタとすることができる。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】同一基板上に酸化物半導体を用いたオフセットトランジスタとオフセットでないトランジスタを形成する。

【解決手段】酸化物半導体層202とゲート絶縁物203とゲート配線となる第1層配線204a、第1層配線204bを形成する。その後、オフセットトランジスタをレジスト206で覆い、酸化物半導体層に不純物を導入し、N型酸化物半導体領域207を形成する。その後、第2層配線209a、第2層配線209b、第2層配線209cを形成する。以上の工程により、オフセットトランジスタとそうでないトランジスタ(アラインドトランジスタ等)を形成することができる。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に互いに離間して配置された第1及び第2の主電極、及び前記第1の主電極と前記第2の主電極間で前記主面上に配置された制御電極を有するスイッチング素子TSWと、コレクタ端子とエミッタ端子と制御端子とを有する第1の駆動素子TD1及び入力端子を含む駆動回路10と、を備え、前記第1の駆動素子の前記コレクタ端子は前記スイッチング素子の前記第1の主電極に接続され、前記第1の駆動素子の前記エミッタ端子は前記スイッチング素子の前記制御電極に接続され、前記第1の駆動素子の前記制御端子は前記入力端子及び前記エミッタ端子に接続される。

(もっと読む)

21 - 40 / 547

[ Back to top ]