Fターム[5F038EZ02]の内容

Fターム[5F038EZ02]に分類される特許

101 - 120 / 547

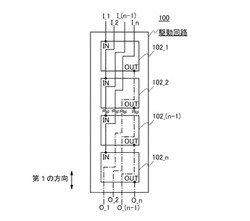

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

酸化プラセオジムを備えた誘電体、酸化プラセオジムを備えたトランジスタ及びその製造方法

【課題】酸化プラセオジムの誘電体、酸化プラセオジムを備えたトランジスタ及びその製造方法を提供し、以って半導体素子のリーク電流及び等価酸化物膜厚の過大の問題を解決すること。

【解決手段】本発明では、酸化プラセオジムを備えたトランジスタは、少なくとも一つのIII−V族基板と、一つのゲート誘電層と、一つのゲート電極とを含む。また、III−V族基板にゲート誘電層が設けられ、ゲート誘電層にゲート電極が設けられ、誘電層は酸化プラセオジム(PrxOy)である。本発明は、誘電層材料として高誘電率及び高エネルギーギャップを備えた酸化プラセオジム(Pr6O11)を用いることにより、リーク電流を有効に抑制する外、更にIII−V族材料を基板とした素子の等価酸化膜厚(EOT)を薄くさせることもできる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

化合物半導体装置

【課題】容量耐性を高めると共に信頼性の向上を図った容量付PDを提供する。

【解決手段】PD、ダイオードを含む素子と複数のMIM容量を基板上に集積した化合物半導体装置において、前記素子からの引き出し配線とMIM容量の下部配線を結ぶ線を第1配線、MIM容量の上部電極とボンディングパッドを結ぶ線を第2配線としたときに前記第1配線と第2配線をスルーホールで接続し、MIM容量に印加する電圧方向を1方向に揃えるように、MIM容量の上下メタルに電圧を印加した。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置及びこれを用いた電気回路、電気回路の制御方法

【課題】消費電力を増大させずにオンチップでHEMTの動作状況をモニターする。

【解決手段】

この半導体装置10においては、第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層側に、2次元電子ガス(2DEG)層13が形成される。この半導体装置10において、電子は、電子供給層12の表面に形成された第1の主電極であるソース電極14と、同様にこの表面に形成された第2の主電極であるドレイン電極15との間を、この2DEG層13を通って流れる。ゲート電極16とソース電極14との間の電子供給層12上に電位検出電極17が設置される。この電位検出電極17には、動作時にこの電位検出電極17に流れる電流がドレイン電流と比べて無視できる程度となるような、充分に高い抵抗値をもつ抵抗18が接続される。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】ゲートリセスの深さの制御を安定的に行なえるようにして、ノーマリオフ動作のデバイスを安定的に作製できるようにする。

【解決手段】半導体装置を、基板1の上方に設けられたGaN電子走行層2と、GaN電子走行層2上に設けられた第1AlGaN電子供給層3と、第1AlGaN電子供給層3上に設けられたAlN電子供給層4と、AlN電子供給層4上に設けられた第2AlGaN電子供給層5と、第2AlGaN電子供給層5及びAlN電子供給層4に設けられたゲートリセス9と、ゲートリセス9に設けられたゲート電極12とを備えるものとする。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】キャパシタ装置及びその製造方法を提供する。

【解決手段】本発明に係るキャパシタ装置10は、第1導電型を有して第1電圧が印加される第1ウェル105及び第2導電型を有して第2電圧が印加される第2ウェル110を有する基板100、及び第1または第2ウェル105,110と絶縁されるように第1または第2ウェル105,110の上部に配されたゲート電極126を含み、キャパシタ装置10のキャパシタンスは、第1ウェル105と第2ウェル110との間の第1キャパシタンス及び第1または第2ウェル105,110とゲート電極126との間の第2キャパシタンスを含む。

(もっと読む)

半導体装置、半導体回路基板および半導体回路基板の製造方法

【課題】化合物半導体材料を節減しつつ化合物半導体を用いた高性能な半導体素子を得ることができる半導体装置、半導体回路基板および半導体回路基板の製造方法を提供する。

【解決手段】半導体回路基板が、トランジスタ形成基板10と回路形成基板50とを有する。トランジスタ形成基板10は、GaN基板であり、表面にBJT40が形成されている。トランジスタ形成基板10の裏面は平滑であり、かつ裏面にコンタクト領域を有する。回路形成基板50は、化合物半導体以外の材料で形成され、半導体能動素子を有さない。回路形成基板50は、平滑な表面、表面に露出するように埋め込まれたコンタクト領域52、54、および受動回路(図示せず)を有する。トランジスタ形成基板10と回路形成基板50は、絶縁膜等の他の膜を介在させずに直接に接合している。

(もっと読む)

DCDCコンバータ、電源回路及び半導体装置

【課題】電力変換効率の向上を実現するDCDCコンバータの提供を目的の一とする。

【解決手段】出力電力を制御するためのスイッチング素子として機能するトランジスタが、通常のゲート電極に加えて、閾値電圧を制御するためのバックゲート電極を備える。そして、DCDCコンバータから出力される出力電力の大きさに従って、バックゲート電極に与える電位の高さを制御するための、バックゲート制御回路を備える。バックゲート制御回路により、バックゲート電極に与える電位を制御することで、出力電力が大きい場合にはオン抵抗が下がるように閾値電圧を調整し、出力電力が小さい場合にはオフ電流が下がるように閾値電圧を調整することができる。さらに、スイッチング素子として機能するトランジスタが、オフ電流の極めて小さい絶縁ゲート電界効果型トランジスタである。

(もっと読む)

システムインパッケージおよびソケット

【課題】サイズやコストを増大させることなく、テスト容易なシステムインパッケージを実現するとともに、そのシステムインパッケージをテストボードとして活用する。

【解決手段】テスト容易化回路内装SIP1cは、少なくともその1つに集積回路チップが搭載された複数のコア基板を、絶縁樹脂層を介して貼り合わせて構成するとともに、コア基板に形成された配線層を、スルーホールを介して接続して構成される。そのコア基板の1つであるテスト容易化回路内装基板10cには、テスト対象の集積回路であるDUT121を装着するソケット122が搭載されており、また、そのソケット122内に設けられたポゴピン1220には、インピーダンス整合用のチップ抵抗1224、インダクタ1225などの受動素子が設けられている。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】直列に複数個接続されたそれぞれのMISFETQN1〜QN5のソース領域とドレイン領域の間に、ソース領域の電位を基準としてドレイン領域に正電圧を印加する場合と、ソース領域の電位を基準としてドレイン領域に負電圧を印加する場合のいずれの状態においても、ソース領域の電位とドレイン電極の電位が同電位の状態よりも容量が減少する電圧依存性を持つ歪補償用容量回路CAPC2が接続されている。

(もっと読む)

半導体装置

【課題】

マイクロ波帯域において容易に設計可能な半導体チップおよび半導体パッケージ(ディジタル受信装置)を提供することを目的とする

【解決手段】

半導体チップと、前記半導体チップ上に配置されたディジタル部と、前記半導体チップ上に配置されたアナログRF部と、前記ディジタル部から伝播するノイズを遮断するような位置に配置された周期構造を有する誘電体と、を備えた半導体装置である。

(もっと読む)

ハイパワーGaNベースFET用のレイアウトデザイン

【課題】FETを提供する。

【解決手段】FETは、基板と、基板上に配置されたバッファ層と、バッファ層上に配置されたチャネル層と、チャネル層上に配置された障壁層とを含む。ソース、ゲート及びドレイン電極は障壁層上に配置されて長手方向に延伸する。チャネル及び障壁層の一部分は長手方向に延伸するメサ部を形成し、ソース及びドレイン電極がメサ部の縁を超えて延伸する。ゲート電極はメサ部の縁側壁に沿って延伸する。導電性ソース相互接続部は障壁層上に配置されソース電極に電気的に接続された第一の端部を有する。第一の誘電体層はバッファ層及びソース相互接続部上に配置される。ゲートビアは第一の誘電体層に形成される。導電性ゲートノードがバッファ層に沿って延伸して前記メサ部の側壁に沿って延伸するゲート電極の一部分に電気的に接続する。ゲートパッドはメサ部に隣接する第一の誘電体層上に配置される。

(もっと読む)

ダイオード回路

【課題】十分な逆方向耐圧を有し、順方向電圧が0Vに近い理想的なダイオード特性を有するダイオード回路を提供する。

【解決手段】アノード端子A及びカソード端子Kを有するアクティブダイオード100であって、ゲート端子111と、アノード端子A及びカソード端子Kの一方に接続されたドレイン端子112と、アノード端子A及びカソード端子Kの他方に接続されたソース端子113とを有するトランジスタ110と、トランジスタ110の閾値電圧に等しくなるように調整されたゲート電圧を、ゲート端子111に供給するゲート電圧発生回路120とを備える。

(もっと読む)

内部回路と静電保護回路を具備する半導体集積回路

【課題】電源電圧の分離数や接地電圧の分離数の増大により静電保護回路の回路数もしくは静電保護素子数の増大を軽減する。

【解決手段】半導体集積回路1は、第1と第2と第3の動作電圧供給端子21、22、23と、第1と第2と第3の内部回路11、12、13と、第1と第2と第3の静電保護回路41、42、43と、接続中Cdとを具備する。第1と第2と第3の内部回路11、12、13は、第1と第2と第3の動作電圧供給端子21、22、23の第1と第2と第3の動作電圧でそれぞれ動作する。第1と第2と第3の静電保護回路41、42、43は、第1と第2と第3の動作電圧供給端子21、22、23と接続中点Cdの間にそれぞれ接続される。すなわち、第1と第2と第3の静電保護回路41、42、43は、従来のΔ(デルタ)接続ではなく、接続中点Cdに関してY(スター)接続される。

(もっと読む)

双方向スイッチ、2線式交流スイッチ、スイッチング電源回路および双方向スイッチの駆動方法

【課題】部品点数増加を抑制する双方向スイッチを提供する。

【解決手段】双方向スイッチにおいて半導体装置101は、第1の電極109A、第2の電極109B、第1のゲート電極112Aおよび第2のゲート電極112Bとを備え、過渡期間において、前記第1の電極109Aの電位が前記第2の電極109Bの電位よりも高い場合、第1の閾値電圧よりも低い電圧を第1のゲート電極112Aに印加し、かつ、第2の閾値電圧よりも高い電圧を前記第2のゲート電極112Bに印加し、逆の場合、第1の閾値電圧よりも高い電圧を前記第1のゲート電極に印加し、かつ、第2の閾値電圧よりも低い電圧を前記第2のゲート電極に印加する。

(もっと読む)

半導体装置

【課題】演算処理や電力消費を増大させることなく、温度特性が安定する半導体装置を提供することを課題とする。

【解決手段】高周波信号を処理する半導体装置1であって、高周波信号を処理する複数の素子2〜8が形成された半導体基板を備え、半導体基板には、複数の素子2〜8のうち温度に応じて特性が変化する特定の素子2,3,5〜8に隣接して該特定の素子2,3,5〜8を加熱する発熱素子9A〜Fが形成されている。

(もっと読む)

101 - 120 / 547

[ Back to top ]