Fターム[5F038EZ02]の内容

Fターム[5F038EZ02]に分類される特許

81 - 100 / 547

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

グラフェン素材の製造方法

【課題】所望形状のグラフェン素材を容易に作製する。

【解決手段】まず、基板本体12を用意し、その基板本体12の全面にNiの結晶層14を成膜する。続いて、リソグラフィ法により結晶層14をジグザグ状にパターニングし、触媒金属層16とする。さらに、触媒金属層16の側面にTiを形成してこれをマスク材17とする。次に、触媒金属層16に対してアセチレンとアルゴンとの混合ガスによりC原子を供給する。すると、Ni表面は(111)面に再配列されると共に、供給されたC原子は六角格子を形成してグラフェンが成長していく。グラフェンは触媒金属層16上に形成されるため、触媒金属層16と同じ形状つまりジグザグ状となる。次に、ジグザグ状のグラフェンの両末端に四角形の電極18,20を取り付ける。その後、触媒金属層16を酸性溶液で溶かし、グラフェンをグラフェン素材10として取り出す。

(もっと読む)

半導体装置

【課題】複数のフローティング領域の間の電位差の不均一を軽減することができる半導体装置を提供する。

【解決手段】半導体装置は、領域3(k)と領域3(k+1)間に、外部容量6(k)を備えている。複数の外部容量6(k)は、その容量がkの増加とともに(即ち、図1の紙面右側から紙面左側に向かうほど)大きくなるように選定されている。この構造により、領域3(k)と領域3(k+1)間の電位差の不均一を軽減することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】実用上限温度をより向上させた炭化珪素半導体装置の製造方法を提供する。

【解決手段】ゲート窓6が形成された炭化珪素基板1の表面に、前駆酸化シリコン膜を成膜する工程と、前駆酸化シリコン膜を酸化窒素ガス雰囲気で熱処理して第1の酸化シリコン膜(O)とする工程と、窒化シリコン膜(N)を積層する工程と、窒化シリコン膜を酸化させて、表面から所定の深さまで第2の酸化シリコン膜(O)を形成して、ONO絶縁膜を形成する工程と、ONO絶縁膜の上にゲート電極を形成する工程とを備える。ゲート電極を形成する工程は、ONO絶縁膜の上に多結晶シリコン膜を成膜する工程と、所望のマスクを用いて、多結晶シリコン膜、第2の酸化シリコン膜、窒化シリコン膜、を連続的にエッチングして、ゲート電極と第2の酸化シリコン膜と窒化シリコン膜の外縁を定義する工程と、ゲート電極の側面及び上部と窒化シリコン膜の外縁を酸化する工程を備える。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置の製造方法

【課題】シート抵抗のバラツキの少ない、さらに製造工程を短くすることができる製造方法を提供する。

【解決手段】半導体層が積層した半導体領域に不純物イオンを注入して、抵抗素子を形成する半導体装置の製造方法において、第1の半導体層4上に第2の半導体層5が積層され、第1の半導体層からなる抵抗素子を形成する際、第2の半導体層の厚さを変えることで、第1の半導体層に達する不純物イオンの量を制御し、予め設定されたシート抵抗の抵抗素子を形成する。

(もっと読む)

DC−DCコンバータ及びその作製方法

【課題】単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ること、及び、DC−DCコンバータの占有面積の増大を抑制する。

【解決手段】入力電圧が印加される入力端子と、入力端子と接続され第1のトランジスタを有する電圧変換回路と、電圧変換回路を制御し珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、入力端子と制御回路との間に設けられ入力電圧を入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、第1のトランジスタ及び第3のトランジスタは酸化物半導体材料をチャネル形成領域に有するトランジスタであり、第2のトランジスタ、並びに、第1のトランジスタ及び第3のトランジスタは、絶縁膜を介して積層されているDC−DCコンバータ及びその作製に関する。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】フェルミ準位ピン止めが低減された化合物半導体を用いたMOS型の化合物半導体装置がより容易に製造できるようにする。

【解決手段】化合物半導体からなる第1半導体層101を形成し、次に、第1半導体層101より小さいバンドギャップエネルギーの化合物半導体からなる臨界膜厚以下の第2半導体層102を、第1半導体層101の上に接して形成し、次に、第2半導体層102の上にアモルファス状態の金属酸化物からなる絶縁層103を形成する。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

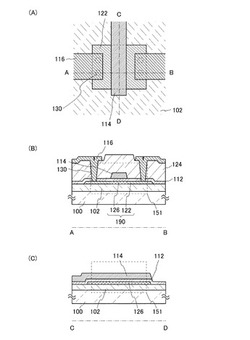

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

半導体装置

【課題】チップ面積を大きくすることなく、チップの空いている外周部分を利用しながら、直列抵抗が小さく、かつ、充分に保護機能を果たすことができる保護ダイオードを有する半導体装置を提供する。

【解決手段】半導体層4に複数個のトランジスタセルTが配列されて形成されている。その複数個のトランジスタセルTより外周側(チップ端部側)の絶縁膜6上にポリシリコン膜によるリング状のp形層1bとn形層1aとが交互に設けられることにより、保護ダイオード1が形成されている。保護ダイオード1は、その一番外側の層にAlなどの金属膜がリング状に接続され、そのング状に設けられている金属膜はソース配線3と金属膜14によりコンタクトされ、一番内側の層にリング状に接続された金属膜がゲート配線2と接続されると共にトランジスタセルTの外周側の一部セルのゲートと接続されている。

(もっと読む)

高周波スイッチおよび高周波モジュール

【課題】挿入損失およびチップサイズの増大を生じることなく、歪特性に優れた高周波スイッチおよび高周波モジュールを提供する。

【解決手段】高周波スイッチであって、高周波信号を入出力するための複数の入出力端子101〜103と、2つの入力端子101、103間に設けられた基本スイッチ部104、105と、基本スイッチ部104、105の導通および遮断を制御するための制御電圧が入力される制御端子106、107とを備え、基本スイッチ部104、105は、メアンダ形状のゲート電極を有するメアンダ型のFET110〜113及びFET120〜123が多段に接続されて形成され、FET110〜113、及び120〜123のうち、入出力端子103からの電気的距離が最も短いFET113、及び120のフィンガー長は、他のFET110〜112、及び121〜123のフィンガー長よりも短い。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

半導体装置

【課題】特性をさらに向上する半導体装置を提供する。

【解決手段】高電圧側電界効果トランジスタ20aの高電圧側ドレイン電極11aと、高電圧側ドレイン電極11aの一側方に間隔をおいて形成される高電圧側ゲート電極12aと、高電圧側ゲート電極12aの一側方に間隔をおいて形成され、高電圧側電界効果トランジスタ20aのソース電極であり、低電圧側電界効果トランジスタ21aのドレイン電極であるソース兼ドレイン電極13aと、ソース兼ドレイン電極13aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ゲート電極14aと、低電圧側ゲート電極14aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ソース電極15aとを有する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

81 - 100 / 547

[ Back to top ]