Fターム[5F038EZ07]の内容

Fターム[5F038EZ07]に分類される特許

1 - 20 / 417

半導体チップ及びその抵抗測定方法、並びに半導体装置

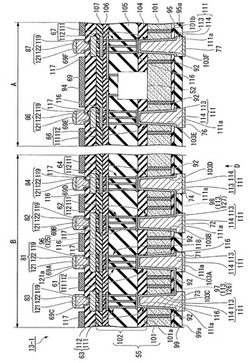

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

リドライバIC、半導体装置、及びその製造方法

【課題】低損失で差動信号を伝送することができるリドライバIC、半導体装置、及びその製造方法を提供する。

【解決手段】本実施の形態に係る半導体装置は、差動信号が伝送される差動配線が形成された配線基板10と、配線基板10に搭載され、外部機器に対して差動信号を送受信するコネクタ11と、配線基板10に搭載され、コネクタ11から受信した差動信号を中継する受信系のリドライバIC21と、受信系のリドライバIC21と離間した位置において配線基板10に搭載され、コネクタ11に送信する差動信号を中継する送信系のリドライバIC20と、を備えるものである。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

半導体集積回路、電子機器及びマルチチップ半導体パッケージ

【課題】比較的簡単な構成でありながらも動的で高分解能の電圧制御可能な半導体集積回路、電子機器及びマルチチップ半導体パッケージを提供すること。

【解決手段】電子機器100は、電源IC110と、電源IC110から出力される電源電圧Vsrcで動作するSoC#0〜2とを備える。SoC#0〜2は、三次元実装されたマルチチップ半導体パッケージに搭載される。SoC#0〜2は、第3の端子123から入力されるアナログ制御信号の電位と、内部配線124の電位とに基づいて、第2の端子122から出力するアナログ制御信号を生成する電位制御回路125と、電源フィードバック(FB)電圧入力端子である第2の端子122及び第3の端子123と、を備える。SoC#0〜2は、FB出力端子FB_out/FB入力端子FB_inをカスケード接続し、最終段のSoC#0のFB出力を電源IC110に接続している。

(もっと読む)

半導体集積回路

【課題】クランプ電圧を正確な値に設定できる半導体集積回路を提供することを目的とする。

【解決手段】第1の電圧である電源を供給されて定電流を発生する定電流部60と、定電流部60で発生された定電流を供給されて第1の電圧より低い第2の電圧を発生し、第1の電圧の電源を第2の電圧にクランプするクランプ部71と、クランプ部71でクランプされた電源を供給されて基準電圧を発生する基準電圧発生部72とを有し、クランプ部71は、ゲートとドレインに接続され縦型接続された複数段のMOSトランジスタM11−1〜M11−nである。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

スタックエラーを測定することのできる三次元集積回路

【課題】スタックエラーを測定することのできる三次元集積回路を提供する。

【解決手段】三次元集積回路100は、第1ウェハ110および第2ウェハ120を含む。第1ウェハ110は、第1導電パターン112を含む。第2ウェハ120は、第2導電パターン122を含み、第1導電パターン112に電気接続される。第1ウェハ110と第2ウェハ120の間の変位は、第1導電パターン112と第2導電パターン122の抵抗に基づいて決定される。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

基板導通を利用した積重ねダイ式の構成をもつ集積回路

【課題】積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供すること。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】不良電流パスの選別に要する時間を短縮する。

【解決手段】半導体装置は、それぞれ少なくとも1つの貫通電極を含み、インターフェイスチップ内に第1のノードn1を有する複数の電流パス101Xと、互いに異なる複数の電圧値からなる比較電圧DACOUTを生成する比較電圧生成部102と、複数の電流パス101Xそれぞれの第1のノードn1の電圧TSVCXと、比較電圧DACOUTの上記複数の電圧値それぞれとを比較し、比較の結果を示す比較結果信号CMPXを電流パス101Xごとに出力する比較部103と、比較結果信号CMPXに応じて、複数の電流パス101Xのそれぞれが高抵抗化しているか否かを示す結果信号RESLTXを生成する結果信号生成部104とを備える。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

低フラックス及び低ノイズの検出回路

【課題】低フラックスを用いている間のノイズレベルを減少することを可能にするような検出回路を提供する。

【解決手段】ソースフォロワ検出器型の検出回路は、結合ノードNに接続されたフォトダイオード1を備える。バイアス回路3は、逆バイアスである第1の状態とフローティングである第2の状態との間にフォトダイオード1をバイアスすることを可能にする。読み出し回路4は、結合ノードNに接続され、フォトダイオード1により測定された現状を示す信号を生成する。金属シールド5は結合ノードNの周りに配置される。金属シールド5は、読み出し回路4の出力に接続され、結合ノードNの電位と同じ方向に変動する電位を持つように構成される。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

受光デバイス、これを用いた光受信機、及び受光デバイスの製造方法

【課題】 従来のPD製造プロセスと同じ工程で大受光径PDの帯域を拡大して、光受信部の高速化を図る。

【解決手段】 受光デバイスは、半導体基板の上方に形成された第1導電型の第1半導体層、前記第1半導体層上の光吸収層、および前記光吸収層上の第2導電型の第2半導体層の積層構造を有する光検出素子と、前記半導体基板の上方で、前記光検出素子に接続されるインダクタと、前記光検出素子で生成された電流を前記インダクタを介して取り出す出力電極と、前記光検出素子にバイアス電極を印加するバイアス印加用電極と、前記インタダクタの金属配線と交差して、前記光検出素子と、前記出力電極又は前記バイアス印加用電極との間を電気的に接続する交差配線と、を含む。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

1 - 20 / 417

[ Back to top ]