Fターム[5F038EZ14]の内容

Fターム[5F038EZ14]に分類される特許

121 - 140 / 1,200

半導体チップ、半導体装置、及び半導体チップの製造方法

【課題】2次電池パックの保護回路を更に小型化すること。

【解決手段】本発明に係る半導体チップは、双方向スイッチを構成する2個のパワートランジスタと、抵抗素子とを備える。2個のパワートランジスタのドレイン同士は接続されている。抵抗素子の一端は、2個のパワートランジスタのうち一方のソース電極と電気的に接続され、その他端は、第1外部パッドと電気的に接続されている。それら2個のパワートランジスタと抵抗素子とは、同一の半導体チップ上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

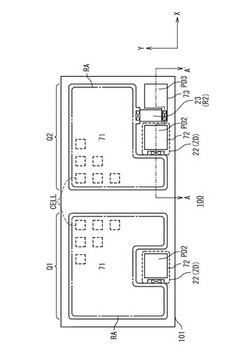

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】半導体装置に用いられるキャパシタを効率よく、しかも少ない占有床面積で行うことができる半導体装置の製造方法および基板処理装置を提供する。

【解決手段】基板200上に下電極を形成する工程(S104)と、下電極の上に、それぞれ異なる金属元素を含む3種の金属酸化膜を積層して誘電膜を形成する工程(S106、S108、S110)と、誘電膜の上に、上電極を形成する工程(S112)と、を有し、各工程は同一の装置で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流が検出された場合に、ハイサイドスイッチだけでなくハイサイドスイッチに接続される回路を保護することが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ゲート電圧降圧部31は、過電流検出部20からの電流制限信号に応じて、MOSトランジスタ15のゲート電圧を第1の電圧から、第1の電圧と第2の電圧との間の第3の電圧まで、第1の時間変化率で低下させる。これによりMOSトランジスタ15のオン抵抗がMOSトランジスタ15の完全オン時のオン抵抗より高くなる。ゲート電圧降圧部32は、ゲート電圧が第3の電圧に達した後に、ゲート電圧を第3の電圧から第2の電圧まで第2の時間変化率で低下させる。第1の時間変化率は、第2の時間変化率よりも大きい。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流の検出精度を高めることが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ハイサイドスイッチ回路10は、入力端子11と出力端子12との間に電気的に接続されるスイッチ(MOSトランジスタ15)と、ゲート制御部16と、過電流検出部20とを備える。過電流検出部20は、抵抗素子21と、比較器22とを含む。比較器22は、抵抗素子21の電圧V1がしきい電圧を超える場合に、過電流を検出する。比較器22は、過電流時の検出電圧V1がしきい電圧を上回るように、予め調整される。抵抗素子21の抵抗値の精度が高くない場合にも、比較器22の調整によって、過電流の検出精度が高められる。

(もっと読む)

キャパシタ構造体およびその製造方法

【課題】シリコン基板に設けられた穴の内部に導電体と誘電体を配置することにより、キャパシタを構成してなるキャパシタ構造体において、穴をより深くしたり、穴の平面形状を複雑な形状とすることなく、導電体間の対向面積を増加させて容量値の増大が実現できるようにする。

【解決手段】穴20は、シリコン基板10の一方の主面に開口する有底穴であり、穴20の内部にはシリコン基板10よりなる突起21が設けられ、穴20の底面は、突起21による凹凸面とされており、穴20の内部では、穴20の底面および側面に、これらの面側から第1の導電体31、誘電体40、第2の導電体32が順次積層されているとともに、第1の導電体31および誘電体40は、突起21による凹凸面の形状を承継した層形状とされている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に設けられた穴に、絶縁体を介して2つの導電体を充填してなる電極部を有する半導体装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の第1の領域1には、表面11に開口する複数個の有底穴20が設けられ、第2の領域2には貫通穴30が設けられ、有底穴20は貫通穴30よりも小さい穴幅を有する。絶縁体50を両導電体40、60で挟んでなる積層構造体が、有底穴20および貫通穴30に充填され、さらに、第1の領域1において複数個の有底穴20間にて連続して形成されており、第1の領域1は、当該積層構造体による容量形成部として構成される。有底穴60における各導電体40、60は、それぞれ貫通穴30における各導電体40、60に電気的に接続されて、半導体基板10の表裏両面11、12に取りだされている。

(もっと読む)

保護装置

【課題】 差動信号ラインに、第1入力端子と第2入力端子を有し、ダイオードにより構成される1パッケージの保護装置を接続する場合、第1入力端子と第2入力端子間のアイソレーションを十分確保し、また、第1入力端子に接続するダイオードと第2入力端子に接続するダイオードの部品ばらつきを抑制する必要がある。また、差動信号ラインに用いる保護装置の場合、部品容量とESD破壊耐量を所望の範囲に収めるようにする必要がある。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域、第2n+型不純物領域、第3n+型不純物領域を設け、第1入力端子に接続する第1n+型不純物領域と、第2入力端子に接続する第3n+型不純物領域との間に、接地端子に接続する第2n+型不純物領域を配置して、横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

コンデンサとその製造方法ならびに多層配線基板

【課題】簡便・安価に製造可能な浮遊インダクタンスの小さいコンデンサ部品と、その製造方法を提供する。また、前記コンデンサ部品を低背化した部品と、その低背コンデンサを内蔵した多層配線基板を提供する。

【解決手段】有機材料の単分子膜を誘電体とするコンデンサにおいて、コンデンサ用電極のうち少なくとも一つが、誘電体単分子膜に担持された触媒物質によって開始する無電解めっきで形成されることを特徴とするコンデンサ。コンデンサを支持基材の上に形成することで、薄膜コンデンサを部品として扱うことが可能となる。また、前記支持基材を薄く研削することで、部品の低背化が可能となる。

(もっと読む)

半導体装置

【課題】リードフレーム上に半導体チップが載置された半導体装置において、サージに対する耐性の向上を図る。

【解決手段】ICチップ10Aを構成するP型の半導体基板10の表面には、N型の埋め込み層11及びエピタキシャル層12と、P型の半導体層13が配置されている。半導体基板10の裏面には金属薄膜30が配置され、その金属薄膜30と、金属のアイランド51の間には銀粒子等を含む導電性ペースト40が挟まれている。半導体層13の表面に配置されたパッド電極16にサージが印加されると、半導体層13から半導体基板10に流れるサージ電流は、金属薄膜30を通って金属のアイランド51に向かう。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や耐圧の汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面に互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、これらの周囲に互いに離間する第1p+型不純物領域と第2p+型不純物領域を設け、第1n+型不純物領域とコンタクトし、入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトし、接地端子に電気的に接続する第2電極とを設ける。第1n+型不純物領域および第2n+型不純物領域は140μm以上離間され、それぞれ角丸四角形状でp+型半導体基板の対角線に沿って配置される。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、第1n+型不純物領域とコンタクトする第1導電層と、第1導電層にコンタクトし入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトする第2導電層と、第2導電層にコンタクトし接地端子に電気的に接続する第2電極とを設けて横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】ゲートリセスの深さの制御を安定的に行なえるようにして、ノーマリオフ動作のデバイスを安定的に作製できるようにする。

【解決手段】半導体装置を、基板1の上方に設けられたGaN電子走行層2と、GaN電子走行層2上に設けられた第1AlGaN電子供給層3と、第1AlGaN電子供給層3上に設けられたAlN電子供給層4と、AlN電子供給層4上に設けられた第2AlGaN電子供給層5と、第2AlGaN電子供給層5及びAlN電子供給層4に設けられたゲートリセス9と、ゲートリセス9に設けられたゲート電極12とを備えるものとする。

(もっと読む)

121 - 140 / 1,200

[ Back to top ]