Fターム[5F038EZ14]の内容

Fターム[5F038EZ14]に分類される特許

161 - 180 / 1,200

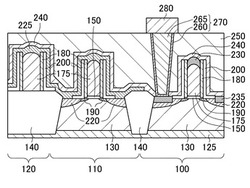

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】フューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置を提供する。

【解決手段】半導体基板上にフィールド酸化膜を介して抵抗体を設け、抵抗体上に第一の金属配線を設け、第一の金属配線上に吸湿性膜を含む平坦性の良い金属間層間膜を形成する。抵抗体のトリミング用フューズは吸湿性膜を含む金属間層間膜の上に形成することで吸湿性膜の露出を防止する。

(もっと読む)

半導体集積回路装置の検査方法及び半導体集積回路装置

【課題】複数の集積回路層が厚さ方向に積層されて成る半導体集積回路装置の層間接続不良の有無を、一層積層する毎に短時間で検査することが可能な検査方法及び半導体集積回路装置を提供する。

【解決手段】互いに積層される集積回路層10及び20に、複数の検査用整流素子部15及び25をそれぞれ形成する。複数の検査用整流素子部15(25)は、複数の接続用端子14(24)のそれぞれと正電源配線13a(23a)及び接地配線13b(23b)との間に接続され、整流素子15a,15b(25a,25b)を含み電流により発光する。複数の接続用端子14及び24を互いに電気的に接続したのち、正電源配線13a(又は接地配線13b)と接地配線23b(又は正電源配線23a)との間にバイアス電圧を印加し、検査用整流素子部25の発光に基づいて、接続用端子14及び24の接続状態を検査する。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量保護ダイオードを採用した静電破壊防止用保護ダイオードからなる半導体装置において、半導体基板の表面に電圧制限素子としてのツェナーダイオード形成のための占有面積を不要とする。

【解決手段】P+型半導体基板1にP+型埋め込み拡散層1bを形成する。次に、その上をノンドープの第1エピタキシャル層4aで被覆する。次に、該第1エピタキシャル層4a上にN型の高比抵抗の第2エピタキシャル層4bを形成する。該第2エピタキシャル層4bをP+分離層6で第1保護ダイオード形成領域50と第2保護ダイオード形成領域51に分離する。第1保護ダイオード形成領域50の第1エピタキシャル層4aの表面から第1エピタキシャル層4a及び第2エピタキシャル層4bに延在するN+型埋め込み層2等を形成する。P+型埋め込み拡散層1bから延在するP+型這い上がり層1cとN+型埋め込み層2でツェナーダイオードTD等を形成する。

(もっと読む)

薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板

【課題】静電気による薄膜トランジスタの閾値電圧変動や絶縁破壊短絡を抑制できる薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板を提供する。

【解決手段】薄膜トランジスタと、静電気誘導素子と、を基板上に有する薄膜トランジスタ回路基板の製造方法であって、基板に設けられた半導体層の上に、薄膜トランジスタの半導体層のパターンを形成する第1のフォトリソ工程と、静電気誘導素子の半導体層のパターンを形成する第2のフォトリソ工程と、基板に設けられた半導体層をエッチングする工程と、を実施することにより薄膜トランジスタの半導体層及び静電気誘導素子の半導体層を形成し、第1のフォトリソ工程におけるフォトレジストの硬化温度は、第2のフォトリソ工程におけるフォトレジストの硬化温度よりも高いことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】経年劣化および分極反転の繰り返しによる劣化の少ない強誘電体キャパシタまたは高誘電率を有する誘電体キャパシタを提供する。比抵抗の増大なしに信頼性の高い配線を有する半導体装置を提供する。

【解決手段】半導体基板表面上に形成された電極を含み、前記電極が、配向性を有する導電体層からなり、前記電極に加え、

下式

M1xM21-x

M1:Au、Pt、Ir、Pd、Os、Re、Rh、Tu、Cu、Co、Fe、Ni、V、Cr

M2:Ta、Ti、Zr、Hf、W、Y、Mo、Nb

で表されるアモルファスまたは微結晶からなるバリア層を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、製造コストの増加を抑制可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板部10、誘電体膜22、再配線24、上部電極25、絶縁膜26、及び外部接続端子28を有する。半導体基板部10は、回路が形成され、回路にそれぞれ接続される下部電極15、上部電極パッド16、接続パッド17、18を上面に有する。誘電体膜22は、下部電極15を被い、上部電極パッド16、接続パッド17、18の上面に達する開口部を有する。再配線24は、一部の接続パッド17、18に電気的に接続される。上部電極25は、誘電体膜22を介して下部電極15の上面に対向して配置され、上部電極パッド16に接続され、再配線24を含む。絶縁膜26は、誘電体膜22、再配線24、及び上部電極25を被う。外部接続端子28は、絶縁膜26を貫通し再配線24に接続され、絶縁膜26の上面から露出する。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの特性を劣化させることなくポリシリコン抵抗素子を製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板30の抵抗素子形成領域に抵抗素子となるポリシリコン膜35aを形成するとともに、トランジスタ形成領域にポリシリコンゲート35b及び高濃度不純物領域40を形成する。その後、全面に絶縁膜41を形成した後、トランジスタ形成領域をフォトレジスト膜42で覆い、ポリシリコン膜35aに導電性不純物をイオン注入する。次いで、フォトレジスト膜42をアッシングにより除去する。このとき、トランジスタは絶縁膜41に覆われているため、アッシングによるダメージが回避される。また、抵抗素子領域に導入された導電性不純物が大気中のO及びHと反応して酸が発生しても、ポリシリコンゲート及び高濃度不純物領域40が酸により溶解することが回避される。

(もっと読む)

半導体装置

【課題】出力用素子から半導体基板の内部に進入する電子により、被保護素子が誤動作を起こすことを抑制する半導体装置を提供する。

【解決手段】半導体基板と、出力用素子と、被保護素子TRSと、タップ部ATDと、第1のアクティブバリア構造ABRとを備える。第1のアクティブバリア構造ABRは、被保護素子TRSとタップ部ATDとの間に配置される。第1のアクティブバリア構造ABRは、p型不純物領域PSRに接続されたn型領域と、n型領域とオーミック接続されたp型領域とを含む。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

半導体集積回路及びその製造方法

【課題】金属層からなるガードリングで囲まれたトリミング素子形成領域のヒューズ上の保護膜の開口からヒューズ上の層間絶縁膜に浸入した水分等がガードリングに形成されたヒューズ引き出し電極用の開口を通ってデバイス形成領域に浸入することを防止する。

【解決手段】ヒューズ5aを取り囲む第1ガードリング30とその外側の第2ガードリング40に囲まれたヒューズ電極引き出し領域41を形成する。ヒューズ5aと連続し層間絶縁膜6とフィールド酸化膜4の間をヒューズ電極引き出し領域41まで延在するヒューズ電極5と、該ヒューズ電極5と接続する第1ヒューズ引き出し電極7cと、該第1ヒューズ引き出し電極7cと接続する第2ヒューズ引き出し電極9cとを形成し、該第2ヒューズ引き出し電極9cを層間絶縁膜8上に形成された第2ガードリング40を構成する第2電極の開口24を通してデバイス素子形成領域80に引き出す。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

半導体装置の製造方法

【課題】FEOLにおいても半導体装置のチャージングを効果的に抑制できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に、被保護素子のゲート絶縁膜となる第1の絶縁膜122を形成する工程(a)と、保護素子部302において第1の絶縁膜122の少なくとも一部を除去する工程(b)と、工程(b)よりも後に、被保護素子部301において第1の絶縁膜122の表面を窒化する工程(c)と、工程(c)よりも後に、被保護素子部301及び保護素子部302の上に跨るように導電膜を選択的に形成することにより、互いに接続された被保護素子のゲート電極141及び保護素子の電極142を形成する工程(d)とを備えている。

(もっと読む)

半導体装置及びその作製方法

【課題】書き込み電圧が小さいアンチヒューズを提供する。

【解決手段】アンチヒューズは読み出し専用の記憶装置のメモリ素子に用いられる。アンチヒューズは、第1導電層、絶縁層、半導体層、及び第2導電層を有する。アンチヒューズに含まれる絶縁層は、原料ガス中にアンモニアを添加して形成した酸化窒化シリコンであり、層中に1.2×1021以上3.4×1021atoms/cm3以下の水素、または3.2×1020以上2.2×1021atoms/cm3以下の窒素を含むことで、低電圧での書き込みが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】補償容量素子のキャパシタ構造に起因したリーク電流の増加を抑制するとともに、立体構造のキャパシタ構造を採用して、占有面積を削減した半導体装置を提供する。

【解決手段】メモリセル領域に形成されたクラウン型のキャパシタ21aと、周辺回路領域に形成されたコンケイブ型の補償容量素子10と、を有することを特徴とする半導体装置20を提供する。また、第1層間絶縁膜上にパッド47a,47bを形成する工程と、パッド47a,47b上に有底筒形状の下部電極66a,66bを形成する工程と、メモリセル領域の下部電極66aの内壁面及び外壁面と、周辺回路領域の下部電極66bの内壁面のみを誘電体膜67a,67bで覆う工程と、誘電体膜上に上部電極69a,69bを形成する工程と、を有することを特徴とする半導体装置20の製造方法を提供する。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる静電気保護装置の面積を大きくすることなく、その破壊耐量及び維持電圧を大きくする。

【解決手段】第1導電型である半導体基板1と、半導体基板の上又は上部に形成された第2導電型である第1拡散層3と、第1拡散層の上部に形成され、第1導電型である第2拡散層5と、第2拡散層の上部に形成され、第2導電型である第3拡散層6と、第1拡散層の上部で且つ第2拡散層から間隔をおいて形成された第2導電型である第4拡散層8と、少なくとも第3拡散層の下に、第2拡散層と間隔をおき且つ下端部が第1拡散層の下端部よりも下に位置するように形成された第1導電型の第5拡散層2とを備えている。第3拡散層から第5拡散層までの最短距離と、第5拡散層から第4拡散層までの最短距離及び第1拡散層の下端部から第4拡散層までの最短距離のいずれか短い方の距離との和は、第3拡散層から第4拡散層までの最短距離よりも小さい。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

161 - 180 / 1,200

[ Back to top ]