Fターム[5F038EZ14]の内容

Fターム[5F038EZ14]に分類される特許

101 - 120 / 1,200

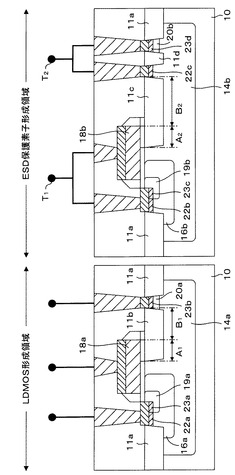

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、光電変換膜が半導体基板上に積層された積層型の半導体装置に関する。

【解決手段】半導体基板と、半導体基板上に形成され、交互に積層された層間絶縁膜と配線層とからなる多層配線層と、多層配線層内において、半導体基板の周縁に沿って環状に形成されたシールリングとを備え、シールリングは、各配線層に形成された環状のシール配線と、各層間絶縁膜に少なくとも1つ形成された環状のシールビアとが積層された構造であり、シールビアを介して積層方向に隣接する少なくとも1組のシール配線では、下方のシール配線の外周面の位置が、上方のシール配線の外周面の位置よりも外側にあることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ダミーアクティブ領域の配置に伴うチップ面積の増大を引き起こすことなく、半導体基板の表面の平坦性を向上させる。

【解決手段】ダミーアクティブ領域であるn型埋込み層3の上部には、厚い膜厚を有する高耐圧MISFETのゲート絶縁膜7が形成されており、このゲート絶縁膜7の上部には、内部回路の抵抗素子IRが形成されている。n型埋込み層3と抵抗素子IRとの間に厚いゲート絶縁膜7を介在させることにより、基板1(n型埋込み層3)と抵抗素子IRとの間に形成されるカップリング容量が低減される構造になっている。

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的小さい面積で形成することができ、かつ、素子サイズの微小化が進んでも保護素子として動作させることを可能にする、保護素子を提供する。

【解決手段】半導体基板1に形成された、第1導電型のウェル領域3と、この第1導電型のウェル領域3に隣接して形成された、第2導電型のウェル領域4と、第1導電型のウェル領域3に形成された、第2導電型チャネルのMOSトランジスタと、第1導電型のウェル領域3とMOSトランジスタのソース領域とMOSトランジスタのゲートとに電気的に接続された第1の配線と、MOSトランジスタのドレイン領域と第2導電型のウェル領域4とに電気的に接続された第2の配線とを含む保護素子を構成する。

(もっと読む)

半導体装置

【課題】大量生産が可能で、かつ従来の小型素子とは異なる構造を有する半導体装置を提供する。また、強度を向上させることが可能であり、作製段階における素子の破壊を抑制することができ、信頼性及び歩留まりの高い半導体装置の構造、及び半導体装置の作製方法を提供することを目的としている。

【解決手段】集積回路を有する層と、集積回路を有する層上に形成され、集積回路を有する層と電気的に接続された第1の端子と、第1の端子上に形成され、第1の端子と電気的に接続されたアンテナとして機能する導電層と、集積回路を有する層上に形成され、集積回路を有する層と、アンテナとして機能する導電層と、第1の端子と電気的に接続されていない第2の端子を有する。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

グラフェン素材の製造方法

【課題】所望形状のグラフェン素材を容易に作製する。

【解決手段】まず、基板本体12を用意し、その基板本体12の全面にNiの結晶層14を成膜する。続いて、リソグラフィ法により結晶層14をジグザグ状にパターニングし、触媒金属層16とする。さらに、触媒金属層16の側面にTiを形成してこれをマスク材17とする。次に、触媒金属層16に対してアセチレンとアルゴンとの混合ガスによりC原子を供給する。すると、Ni表面は(111)面に再配列されると共に、供給されたC原子は六角格子を形成してグラフェンが成長していく。グラフェンは触媒金属層16上に形成されるため、触媒金属層16と同じ形状つまりジグザグ状となる。次に、ジグザグ状のグラフェンの両末端に四角形の電極18,20を取り付ける。その後、触媒金属層16を酸性溶液で溶かし、グラフェンをグラフェン素材10として取り出す。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】実用上限温度をより向上させた炭化珪素半導体装置の製造方法を提供する。

【解決手段】ゲート窓6が形成された炭化珪素基板1の表面に、前駆酸化シリコン膜を成膜する工程と、前駆酸化シリコン膜を酸化窒素ガス雰囲気で熱処理して第1の酸化シリコン膜(O)とする工程と、窒化シリコン膜(N)を積層する工程と、窒化シリコン膜を酸化させて、表面から所定の深さまで第2の酸化シリコン膜(O)を形成して、ONO絶縁膜を形成する工程と、ONO絶縁膜の上にゲート電極を形成する工程とを備える。ゲート電極を形成する工程は、ONO絶縁膜の上に多結晶シリコン膜を成膜する工程と、所望のマスクを用いて、多結晶シリコン膜、第2の酸化シリコン膜、窒化シリコン膜、を連続的にエッチングして、ゲート電極と第2の酸化シリコン膜と窒化シリコン膜の外縁を定義する工程と、ゲート電極の側面及び上部と窒化シリコン膜の外縁を酸化する工程を備える。

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的簡易な構成であり、かつ、Vt1を3つ以上の多くの電圧値に設定することを可能にする、ESD(静電気放電)対策用の保護素子を提供する。

【解決手段】半導体層に形成された、ソース領域12及びドレイン領域13と、半導体層上にゲート絶縁膜14を介して形成されたゲート15と、ソース領域12の表面に接続され、グラウンドに電気的に接続されたソース電極と、ドレイン領域12の表面に接続され、サージ入力が入力されるドレイン電極と、ソース電極とゲート15との間に接続されたダイオード21(21A,21B)とを含んで、回路素子を保護するための保護素子を構成する。

(もっと読む)

集積回路装置およびその調製方法

【課題】 非常に複雑で費用がかかるバンプ・パッドを形成せずに、集積回路装置を製造する。

【解決手段】 集積回路装置100は、第1の環状誘電体ブロック21Aを有する底部ウェハー10Aと、底部ウェハー10A上に配置される、第2の環状誘電体21Bを有する少なくとも1つの積層ウェハー10Bと、実質的に直線状に底部ウェハー10A中へと積層ウェハー10Bを貫通する導電性ビア49とを備える。底部ウェハー10Aと積層ウェハー10Bはその間の接着層41により接合されている。底部ウェハー10Aと積層ウェハー10Bとの間にはバンプ・パッドは配置されない。導電性ビア49は、第1の環状誘電体ブロック21Aおよび第2の環状誘電体ブロック21Bの内部に位置している。

(もっと読む)

マイクロローディング効果を軽減するためのSiGe埋め込みダミーパターンを備えたSiGe装置

【課題】SiGe装置を取り囲んで、SiGeのエピタキシャル成長時にマイクロローディング効果を軽減できるように特別に設計されたSiGe埋め込みダミーパターンを備えた改良されたSiGe装置を提供する。

【解決手段】マイクロローディング効果を軽減するためのダミーパターンを備えた半導体装置は、内部領域200と外部領域400の間に中間環状領域300が設けられた半導体基板1と、基板上、内部領域200に設けられたSiGe装置100と、基板上、中間環状領域300に設けられた複数のダミーパターン20とを含む。複数のダミーパターン20のうち少なくとも1つがSiGeを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

チップの製造方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

半導体装置、および半導体装置の検査方法

【課題】高抵抗回路の面積の狭小化を図り、集積率の高い半導体装置への高抵抗回路の形成を容易とする。

【解決手段】配線層2に形成された下層配線20および下層配線22と、配線層2上に形成された層間絶縁膜12と、層間絶縁膜12に形成され、下層配線20と接続するビア30と、層間絶縁膜12に形成され、下層配線22と接続するビア32と、層間絶縁膜12上に形成され、ビア30とビア32とを接続する上層配線24と、を備え、ビア30およびビア32の抵抗値は、上層配線24の抵抗値よりも大きい。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離酸化膜上に所望の形状の抵抗素子を形成して、抵抗値の精度を高めて信頼性を向上させる。

【解決手段】半導体基板1の表面に形成された所定領域の素子分離酸化膜2上に複数の抵抗素子4が形成された半導体装置であって、抵抗素子4と近接する位置に活性領域3を設けた。抵抗素子4近傍の素子分離酸化膜2を必要な範囲に区切ることができ、CMP法による素子分離酸化膜2の研磨の際に素子分離酸化膜2の中央部に凹みが形成されてしまうことを抑止できるため、抵抗素子4の形状の寸法精度を向上させることが可能となる。

(もっと読む)

半導体チップ、半導体装置、及び半導体チップの製造方法

【課題】2次電池パックの保護回路を更に小型化すること。

【解決手段】本発明に係る半導体チップは、双方向スイッチを構成する2個のパワートランジスタと、抵抗素子とを備える。2個のパワートランジスタのドレイン同士は接続されている。抵抗素子の一端は、2個のパワートランジスタのうち一方のソース電極と電気的に接続され、その他端は、第1外部パッドと電気的に接続されている。それら2個のパワートランジスタと抵抗素子とは、同一の半導体チップ上に形成されている。

(もっと読む)

101 - 120 / 1,200

[ Back to top ]