Fターム[5F038EZ14]の内容

Fターム[5F038EZ14]に分類される特許

81 - 100 / 1,200

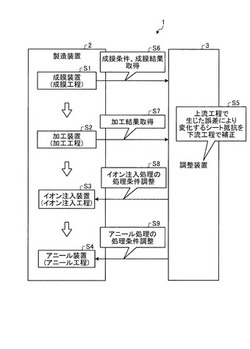

半導体装置の製造方法、製造システムおよび調整装置

【課題】製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供すること。

【解決手段】実施形態にかかる半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に薄膜抵抗体15を構成する金属薄膜およびバリアメタル16を構成するバリアメタル薄膜を形成する。そして、金属薄膜およびバリアメタル薄膜をパターニングし、薄膜抵抗体15と当該薄膜抵抗体15上にバリアメタル膜16aを形成する。その後、バリアメタル膜16a上に絶縁膜17を形成し、絶縁膜17にバリアメタルエッチング部16bを露出させる開口部17aと、コンタクト部を露出させるコンタクトホール17bを形成する。続いて、コンタクトホール17bを介してバリアメタル膜16aと電気的に接続される導電性薄膜18cを形成する。その後、導電性薄膜18cのうちバリアメタルエッチング部16b上に位置する部分をウェットエッチングによってパターニングし、バリアメタル膜16aのうちバリアメタルエッチング部16bをパターニングする。

(もっと読む)

半導体装置

【課題】絶縁耐量を改善することができる半導体装置を得る。

【解決手段】Si基板10(基板)上にゲート抵抗7(下配線)が設けられている。ゲート抵抗7を層間絶縁膜12が覆っている。層間絶縁膜12上に、互いに分離したアルミ配線5a,5b(第1及び第2の上配線)が設けられている。アルミ配線5a,5bを半絶縁性の保護膜4が覆っている。ゲート抵抗7の直上であってアルミ配線5aとアルミ配線5bとの間の領域に、保護膜4が設けられていない。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

抵抗回路を有する半導体装置

【課題】高抵抗・高精度の抵抗素子からなる抵抗回路を提供する。

【解決手段】500Å以下に薄膜化した薄膜材料からなる抵抗素子の上にシリコン窒化膜などの絶縁膜を形成する。この窒化膜により抵抗素子に対するコンタクトホールの突き抜けを防止する。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】同一半導体基板上に、トランジスタ素子、及び、容量素子、及び、抵抗素子を有する半導体装置において、十分な機能を有する容量素子を提供する。

【解決手段】容量素子をアクティブ領域上、抵抗素子を素子分離領域上に同一の多結晶シリコンで形成した後、CMPやエッチバック等で、所望の抵抗体の膜厚になるまで、基板表面を平坦化させながら削る。この時、アクティブ領域と、素子分離領域との高さの違いによって、膜厚の薄い抵抗素子と、膜厚の厚い容量素子の上部電極が形成される。容量素子の上部電極が十分な膜厚を持つので、コンタクトの突き抜けや、高抵抗化に伴う電圧依存性の増加などの特性劣化が防止され、アナログ回路に必要な高抵抗素子とプロセスを共通化することが可能であり、かつ、十分な機能を有する容量素子を製造することができる。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

半導体装置

【課題】不要な寄生素子の影響を排除できる低容量の過渡電圧保護素子を提供する。

【解決手段】半導体基板上に第1のエピタキシャル層210を形成し、第1のエピタキシャル層の表面近傍に埋め込み層220を形成し、埋め込み層上に第2のエピタキシャル層211を形成し、第2のエピタキシャル層内に第1のディープ拡散層250を形成し、第1のディープ拡散層内にツェナーダイオードを形成し、ツェナーダイオードから離れた位置に第1のPNダイオードを形成し、ツェナーダイオードは第1の分離層240により分離されており、第1のPNダイオードは第2の分離層241で分離されており、ツェナーダイオードと第1のPNダイオードが埋め込み層を経由して逆方向に直列接続されることにより、不要な寄生素子の影響を排除でき、かつ低容量の過渡電圧保護素子を実現する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

半導体装置およびそれを用いた発光装置

【課題】 層間絶縁膜を挟んでゲート電極と容量電極が対向してできる容量の占有面積を小さくする。

【解決手段】 チャネル領域上の層間絶縁膜が周囲よりも膜厚が薄く、その部分で容量電極がゲート電極と対向して容量を形成している半導体装置。

(もっと読む)

半導体装置、及びそれを用いた装置

【課題】信頼性を向上させることができる半導体装置,半導体装置を用いた回転電機または車両を提供する。

【解決手段】ショットキ接合と、pn接合を備える半導体装置であって、pn接合は高濃度P型拡散層5とN型拡散層4で形成され、低濃度P型拡散層6と金属電極7により、ショットキ接合が形成され整流領域のpn接合部の降伏電圧を、前記ショットキ接合及びガードリング部Z2のpn接合より低くすることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子について、レイアウト面積の増大を防ぎつつ、周辺の電荷の影響を受けずに安定した抵抗値を得ることができ、しかも、抵抗体に印加できる電位の極性に制限のない半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1上のLOCOS酸化膜3上に形成された抵抗素子10と、を備え、抵抗素子10は、LOCOS酸化膜3上に形成されたシールド用ポリシリコン膜11と、シールド用ポリシリコン膜11上に形成されたシリコン酸化膜13と、シリコン酸化膜13上に形成されたポリシリコン抵抗体15と、ポリシリコン抵抗体15の一方の端部に接合された第1の電極21と、ポリシリコン抵抗体15の他方の端部に接合された第2の電極22と、シールド用ポリシリコン膜11に接合された第3の電極23と、を有し、第1の電極21及び第2の電極22うちの一方が、配線25を介して第3の電極23と電気的に接続されている。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

シリコン構造体、当該シリコン構造体を用いた容量素子および当該シリコン構造体の作製方法

【課題】3次元的に複雑な形状のシリコン構造体を提供する。また、当該シリコン構造体を、自然と秩序が生じて自分自身で秩序的なパターン形成が行われる現象を用いて簡便に作製する方法を提供する。

【解決手段】アモルファスシリコン層に水素雰囲気下でプラズマ処理を行って、当該シリコン層表面に微結晶シリコンを成長させる反応過程と、露出しているアモルファスシリコン層をエッチングする反応過程を並行して進行させ、当該シリコン層上に微結晶状の上部構造体とアモルファス状の下部構造体からなるナノ構造体を形成することにより、3次元的に複雑な形状のシリコン構造体を提供することができる。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、光電変換膜が半導体基板上に積層された積層型の半導体装置に関する。

【解決手段】半導体基板と、半導体基板上に形成され、交互に積層された層間絶縁膜と配線層とからなる多層配線層と、多層配線層内において、半導体基板の周縁に沿って環状に形成されたシールリングとを備え、シールリングは、各配線層に形成された環状のシール配線と、各層間絶縁膜に少なくとも1つ形成された環状のシールビアとが積層された構造であり、シールビアを介して積層方向に隣接する少なくとも1組のシール配線では、下方のシール配線の外周面の位置が、上方のシール配線の外周面の位置よりも外側にあることを特徴とする半導体装置。

(もっと読む)

81 - 100 / 1,200

[ Back to top ]