Fターム[5F038EZ14]の内容

Fターム[5F038EZ14]に分類される特許

141 - 160 / 1,200

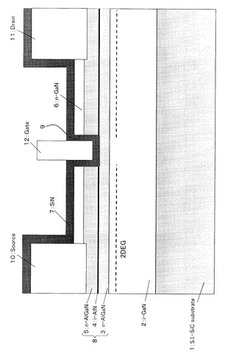

半導体装置及びその製造方法、電源装置

【課題】ゲートリセスの深さの制御を安定的に行なえるようにして、ノーマリオフ動作のデバイスを安定的に作製できるようにする。

【解決手段】半導体装置を、基板1の上方に設けられたGaN電子走行層2と、GaN電子走行層2上に設けられた第1AlGaN電子供給層3と、第1AlGaN電子供給層3上に設けられたAlN電子供給層4と、AlN電子供給層4上に設けられた第2AlGaN電子供給層5と、第2AlGaN電子供給層5及びAlN電子供給層4に設けられたゲートリセス9と、ゲートリセス9に設けられたゲート電極12とを備えるものとする。

(もっと読む)

半導体装置

【課題】トレンチゲート型パワーMOSFETのゲート電極の微細化に伴って、トレンチ底部の曲率が大きくなり、その部分に電界が集中し、ゲート酸化膜(絶縁膜)の劣化が起きる。このゲート絶縁膜の劣化は、Nチャネル型パワーMOSFETの場合、ゲート側バイアスが負である場合に起こりやすく、Pチャネル型パワーMOSFETの場合、ゲート側バイアスが正である場合に起こりやすい。

【解決手段】本願発明は、絶縁ゲート型パワー系トランジスタ等をチップ内に具備する半導体装置であって、ゲート保護素子は双方向ツェナーダイオードを具備し、前記双方向ツェナーダイオードは、そのゲート側がマイナスバイアスされたときの耐圧と、そのゲート側がプラスバイアスされたときの耐圧とは相互に異なるように、複数の濃度の異なるP型不純物領域(またはP型不純物領域)を有する。

(もっと読む)

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1インダクタと第2インダクタを構成する金属材料のマイグレーションに起因して第1インダクタと第2インダクタの絶縁が確保できなくなることを、抑制する。

【解決手段】半導体チップ100は配線基板200の第1面上に実装されており、多層配線層を有している。第1インダクタ112は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は第1インダクタ112に対向している。封止樹脂400は、配線基板200の少なくとも第1面と、半導体チップ100とを封止している。溝500は、封止樹脂400と多層配線層の界面のうち、少なくとも第1インダクタ112と第2インダクタ122の間に位置している部分の全域に形成されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】トランジスタが有するしきい値相当分の電圧/電流のロスを低減し、プロセスの簡略化、及び回路構成の簡素化を目的とした整流特性を有する半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子に整流回路を設ける。整流回路において、電波を受信するアンテナと整流回路のトランジスタのゲートとドレイン端子との間に、コイルを重ねて配置することで、電波を受信するアンテナとコイルの結合を利用して、ダイオード単体と比較しダイオードとコイルが出力する電圧を大きくし、整流効率を向上させる。

(もっと読む)

半導体装置およびその製造方法

【課題】より低コストで、より信頼性の高いMIMキャパシタを有する、より信頼性の高い半導体装置、およびその製造方法を提供する。

【解決手段】本製造方法は、半導体基板SUBを準備する工程と、半導体基板SUBの一方の主表面上に、アルミニウム層AC1を有する第1の金属電極LEL1と、第1の金属電極LEL1上の誘電体層DECと、誘電体層DEC上の第2の金属電極UELとを形成する工程とを備える。第1の金属電極LEL1を形成する工程においては、表面がRmax<80nm、Rms<10nm、Ra<9nmの関係を満たすように、アルミニウム層AC1が形成される。第1の金属電極LEL1を形成する工程には、少なくとも1層の第1のバリア層T1を形成する工程と、第1のバリア層T1上に、アルミニウム層AC1を形成する工程と、アルミニウム層AC1を構成する結晶を再結晶化する工程とを含んでいる。

(もっと読む)

増幅回路装置

【課題】J−FETを増幅回路装置として採用する場合に、意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発することを回避する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。n型半導体基板上にバックゲート領域となるp型半導体層を設けてpn接合を形成し、この接合容量をハイパスフィルタ5の容量とする。

(もっと読む)

薄膜キャパシタの製造方法及び該方法により得られた薄膜キャパシタ

【課題】薄膜キャパシタにおける諸特性低下の原因となるヒロックを抑制し、リーク電流特性及び絶縁耐圧特性に優れた薄膜キャパシタを製造する。

【解決手段】下部電極を形成した後、300℃よりも高い温度のアニール処理を行わずに薄膜形成前駆体溶液を下部電極上に塗布し、乾燥は室温〜450℃の範囲内の所定の温度で行い、焼成は乾燥温度よりも高い450〜800℃の範囲内の所定の温度で行い、塗布から焼成までの工程は塗布から焼成までの工程を1回又は2回以上行うか或いは塗布から乾燥までの工程を2回以上行った後、焼成を1回行い、初回の焼成後に形成される誘電体薄膜の厚さは20〜600nmにする。下部電極の厚さと初回の焼成後に形成される誘電体薄膜の厚さの比(下部電極の厚さ/誘電体薄膜の厚さ)は0.10〜15.0の範囲とするのが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】エッチング装置の経時変化や状態変化等によらずトレンチの深さのばらつきを低減することができる半導体装置の製造方法を得る。

【解決手段】まず、所望の深さよりも浅い深さを持つトレンチ16をSi基板10の主面に形成する。次に、トレンチ16の深さを測定する。トレンチ16の底面からSi基板10に酸素イオン18を注入する。この際に、測定したトレンチ16の深さと所望の深さの差に基づいて酸素イオン18の注入エネルギーを調整して、Si基板10の所望の深さに酸素イオン18が注入されるようにする。次に、熱処理を行って酸素イオン18を注入した位置にSiO2膜22を形成する。次に、SiO2膜22をエッチングストッパとして用いて、トレンチ16の底面からSi基板10を更にエッチングしてトレンチ24を形成する。その後、SiO2膜22を除去する。

(もっと読む)

半導体装置及びその検査方法並びにその設計方法

【課題】不良箇所を容易に特定し得る半導体装置及びその形成方法並びにその設計方法を提供する。

【解決手段】配線パターン32aと、ダミーパターン32bと、一方の端部が配線パターンに電気的に接続され、他方の端部がダミーパターンに電気的に接続されたヒューズ32cとを有している。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

半導体装置及びその製造方法

【課題】小さいサイズでラッチアップの発生を防止できる半導体装置を提供する。

【解決手段】第1導電型の半導体基板1と、前記半導体基板内に形成された第1導電型の第1ウェル領域4と、前記半導体基板内に形成され、第1ウェル領域と隣り合う領域に配置された第2導電型のエピタキシャル領域2と、前記エピタキシャル領域内下方の領域に形成され、前記エピタキシャル領域よりも不純物濃度が高い第2導電型の埋め込み領域6と、第1ウェル領域と前記エピタキシャル領域及び前記埋め込み領域との境界に形成されたトレンチ8と、第1ウェル領域上に形成され、第2導電型のソース及びドレイン領域を有する第1半導体素子と、前記エピタキシャル領域上に形成され、第1導電型のソース及びドレイン領域を有する第2半導体素子と、を備える。

(もっと読む)

固体撮像装置、および、その製造方法、電子機器

【課題】撮像画像の画像品質、装置の小型化、装置の信頼性、製造効率などの各特性について向上させる。

【解決手段】複数の転送電極31が間を隔てて垂直方向yに並ぶように単一の導電材料層313を加工して形成する。また、第1キャパシタ電極C11および第2キャパシタ電極C21について、転送電極31へ加工される導電材料層313から形成する。

(もっと読む)

DCDCコンバータ、電源回路及び半導体装置

【課題】電力変換効率の向上を実現するDCDCコンバータの提供を目的の一とする。

【解決手段】出力電力を制御するためのスイッチング素子として機能するトランジスタが、通常のゲート電極に加えて、閾値電圧を制御するためのバックゲート電極を備える。そして、DCDCコンバータから出力される出力電力の大きさに従って、バックゲート電極に与える電位の高さを制御するための、バックゲート制御回路を備える。バックゲート制御回路により、バックゲート電極に与える電位を制御することで、出力電力が大きい場合にはオン抵抗が下がるように閾値電圧を調整し、出力電力が小さい場合にはオフ電流が下がるように閾値電圧を調整することができる。さらに、スイッチング素子として機能するトランジスタが、オフ電流の極めて小さい絶縁ゲート電界効果型トランジスタである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

容量素子の製造方法

【課題】基板上に耐圧が異なる容量素子を共通の工程で形成する際に、基板上に残渣を残さないようにする。

【解決手段】基板10の上に半導体不純物がドープされた第1ポリシリコン層40を形成し、第1ポリシリコン層40の上にCVD法により第1酸化膜41を層状に堆積する(図2(a))。これにより、1回目の酸化で第1酸化膜41を第1ポリシリコン層40の粒界部に入り込ませないようにする。そして、第1酸化膜41を第1ボトム膜24にパターニングした後(図2(b))、第1ポリシリコン層40の上に第2酸化膜42を形成する(図2(c))。2回目の酸化は短時間で終わるので、第1ポリシリコン層40の増速酸化が進行する前に第2酸化膜42の形成が完了する。このため、第1ポリシリコン層40をエッチングする際に第2酸化膜42の一部がマスクとならないようにすることができる。

(もっと読む)

光電変換装置

【課題】電圧降下が小さい整流素子を得ること、及び、コンバータ回路の作製コストを抑制することを課題とする。

【解決手段】光電変換素子と、当該光電変換素子の出力を昇圧又は降圧し、スイッチング素子及び整流素子を有するコンバータ回路と、を有する光電変換装置において、当該スイッチング素子として、ノーマリオフの第1の酸化物半導体トランジスタと、当該整流素子として、ダイオード接続されたノーマリオンの第2の酸化物半導体トランジスタとを有する光電変換装置に関する。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】フューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置を提供する。

【解決手段】半導体基板上にフィールド酸化膜を介して抵抗体を設け、抵抗体上に第一の金属配線を設け、第一の金属配線上に吸湿性膜を含む平坦性の良い金属間層間膜を形成する。抵抗体のトリミング用フューズは吸湿性膜を含む金属間層間膜の上に形成することで吸湿性膜の露出を防止する。

(もっと読む)

141 - 160 / 1,200

[ Back to top ]