Fターム[5F041CA64]の内容

Fターム[5F041CA64]の下位に属するFターム

MOCVD(有機金属気相熱分解法) (2,918)

Fターム[5F041CA64]に分類される特許

361 - 367 / 367

III族窒化物半導体発光素子

【課題】 本発明は、発光特性に優れ、エージングによる発光出力低下、逆耐電圧減少等の特性変化が極めて少ないIII 族窒化物半導体発光素子を得ることを目的とする。

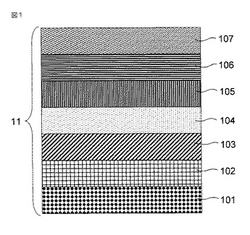

【解決手段】 結晶基板上に形成された、III 族窒化物半導体(組成式AlxGayInzN1-aMa:0≦x≦1、0≦y≦1、0≦z≦1で且つ、x+y+z=1であり、そしてMは窒素(N)とは別の第V族元素を表し、0≦a<1である。)を含むIII 族窒化物半導体発光素子であって、結晶基板側よりn型層、発光層およびp型層をこの順序で有し、n型層にゲルマニウム(Ge)がドープされた領域を含み、かつn型層よりもキャリア濃度の低い下地層をn型層と結晶基板との間に有することを特徴とするIII 族窒化物半導体発光素子。

(もっと読む)

III族窒化物半導体結晶およびその製造方法、III族窒化物半導体デバイスおよびその製造方法ならびに発光機器

【課題】 半導体デバイス程度の大きさのIII族窒化物半導体結晶およびその製造方法、III族窒化物半導体デバイスおよびその製造方法ならびに発光機器を提供する。

【解決手段】 下地基板1上に1以上のIII族窒化物半導体結晶基板11を成長させる工程と、III族窒化物半導体結晶基板11上に1層以上のIII族窒化物半導体結晶層12を成長させる工程と、III族窒化物半導体結晶基板11およびIII族窒化物半導体結晶層12から構成されるIII族窒化物半導体結晶10を下地基板1から分離する工程とを含み、III族窒化物半導体結晶10の厚さが10μm以上600μm以下、幅が0.2mm以上50mm以下であるIII族窒化物半導体結晶の製造方法。

(もっと読む)

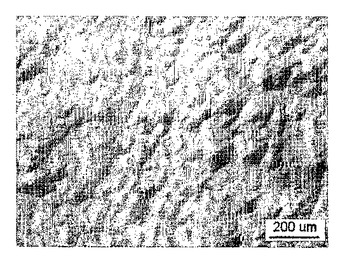

ハイドライド気相成長法による平坦で低転位密度のm面窒化ガリウムの成長

【課題】非常に平坦性で完全な透明性と鏡面性をもつm面窒化ガリウム(GaN)膜を成長する方法。

【解決手段】本方法は、選択横方向成長技術によって構造欠陥密度の大幅な低減を実現する。高品質で、一様で、厚いm面GaN膜は分極のないデバイスの成長のための基板として用いるために作製される。

(もっと読む)

テクスチャ出しされた半導体層を特徴とする光学装置

半導体センサ、太陽電池又はエミッタあるいはそれらの前駆体は、基板と、この基板上に堆積されたテクスチャ出しされた半導体層とを有する。この層は、基板上に成長されるときにテクスチャ出しされるか、テクスチャ出しされた基板表面を複製することによってテクスチャ出しされる。それから基板又は第1の層は、装置から他の半導体層を成長させたりテクスチャ出しするためのテンプレートとなる。テクスチャ出しされた層は、基板から表面に複製されて、光取り出しや光吸収を強化する。いくつかの障壁及び量子井戸層からなる複合的量子井戸は、テクスチャ出しされた層を交互に繰り返しながら堆積される。量子井戸層の領域におけるテクスチャ出しは、半導体が有極性であり、そして量子井戸が極性方向に沿って成長される場合に、内部量子効率を大幅に強化する。これは、窒化物半導体が極性[0001]又は[000−1]方向に沿って成長される場合である。 (もっと読む)

大面積で均一な低転位密度GaN基板およびその製造プロセス

15cmを超える大面積と、少なくとも1mmの厚さと、5E5cm−2を超えない平均転位密度と、25%未満の転位密度標準偏差比率と、を有する大面積で均一な低転位密度単結晶III−V族窒化物材料、たとえば窒化ガリウム。かかる材料は、(i)たとえばIII−V族窒化物材料の成長表面の少なくとも50%にわたってピットを形成するピット化成長条件下で、III−V族窒化物材料を基板上に成長させる第1段階であって、成長表面上のピット密度が、成長表面において少なくとも102ピット/cm2である段階と、(ii)ピット充填条件下でIII−V族窒化物材料を成長させる第2段階と、を含むプロセスによって基板上に形成することができる。  (もっと読む)

(もっと読む)

犠牲層上のヘテロエピタキシによるIII族窒化物の自立基板の実現方法

本発明は、III族窒化物の自立基板の作製に関するものである。本発明は、より詳細には、エピタキシによって初期基板からIII族窒化物、とくに窒化ガリウム(GaN)の自立基板を実現する方法であって、III族窒化物のエピタキシ工程の際に自然に蒸発させるための犠牲層として、単結晶珪素ベースの中間層の蒸着を含むことを特徴とする方法を対象とする。この方法はとくに、平坦で直径が2”を超えるIII族窒化物自立基板を得ることを可能にする。 (もっと読む)

LED照明光源およびLED照明装置

【課題】従来に比べてLEDベアチップの熱劣化を防止し、発光効率を向上させることで、優れた性能を有するLEDモジュール等のLED照明用光源と、これを光源に利用したLED照明装置を提供する。

【解決手段】 LEDベアチップ2において、p電極405に設けられた金バンプG1、G2の総面積(接合面積)が、その表面が金属であるp電極405と実装パターン201Bの間で、p型半導体層404および活性層403に略等しいp電極405の面積の20%以上になるように設定する。

この金バンプG1、G2の直径の設定によって基板10の熱抵抗を3.0℃/W以下に設定し、ヒートシンクと熱的密着させることで、LEDベアチップ温度を80℃以内に抑制する。

(もっと読む)

361 - 367 / 367

[ Back to top ]