Fターム[5F043FF01]の内容

Fターム[5F043FF01]に分類される特許

1 - 20 / 127

光電変換素子の製造方法

【課題】 電極を形成する工程が増えることを抑制することが可能な光電変換素子の製造方法を提供する。

【解決手段】 本発明の光電変換素子の製造方法は、受光面を有し、該受光面から入射した光を光電変換する光電変換層を有する基板を準備する工程と、該基板の前記受光面の上にアルミニウムを主成分とする被覆層を形成する工程と、該被覆層の一部の上に、アルミニウムと異なる材料を主成分とするマスクを形成する工程と、前記被覆層および前記マスクを酸性溶液に浸すとともに、該酸性溶液内に配置した陰極と前記基板との間に電界を印加して前記マスクから露出している前記被覆層を陽極酸化して、前記基板の前記受光面に到る多数の貫通孔を有する、陽極酸化された該被覆層を形成する工程と、前記被覆層の前記貫通孔を通して前記基板の前記受光面のうち対応する部分をエッチングする工程と、前記マスクを除去して、前記被覆層の前記一部を電極とする工程とを有する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

エッチング方法、これに用いられるシリコンエッチング液、及び半導体基板製品の製造方法

【課題】多結晶シリコン及び/又はアモルファスシリコンについて、シリコン等を的確かつ高速に除去し、一方で残される電極部材等を損傷させずに維持することができるシリコンエッチング液及びこれを用いたエッチング方法、これを用いた半導体基板製品を提供する。

【解決手段】アニオン性基を有する炭素数3以上の化合物と硝酸とフッ化水素酸とを水性媒体中に含有するシリコンエッチング液を準備し、該シリコンエッチング液を多結晶シリコン及び/又はアモルファスシリコンからなるシリコン膜に適用して、キャパシタとなる凹凸形状を形成するエッチング方法。

(もっと読む)

光抽出構造を備えた垂直型発光素子

【課題】発光素子の発光効率と信頼性を向上させる。

【解決手段】p−型窒化物半導体層30と、該p−型窒化物半導体層30上に位置する発光層20と、該発光層20上に位置するn−型窒化物半導体層10と、該n−型窒化物半導体層10上に位置するエッチング障壁層40と、該エッチング障壁層40上に位置する光抽出構造50と、を含んで構成され、前記エッチング障壁層40は、前記n−型窒化物半導体層10よりも大きいエネルギーバンドギャップを有し、前記エッチング障壁層40の少なくとも一部が前記光抽出構造50と接している。

(もっと読む)

太陽電池の製造方法

【課題】光利用効率が高く、光電変換効率に優れた太陽電池の製造方法を得ること。

【解決手段】複数の開口部を有するエッチングマスクを第1導電型の半導体基板の一面側に形成し、前記エッチングマスクを用いたウエットエッチングにより前記開口部の下部領域およびその周辺領域の前記半導体基板をエッチングしてテクスチャーを形成するテクスチャー形成工程と、前記半導体基板の一面側に第2導電型の不純物元素を拡散して不純物拡散層を形成する不純物拡散層形成工程と、前記半導体基板の一面側における電極形成領域および前記半導体基板の他面側に電極を形成する電極形成工程と、を含む太陽電池の製造方法であって、前記テクスチャー形成工程では、前記ウエットエッチングの途中において、前記ウエットエッチングにより発生した水素ガスを前記開口部から外部に放出した後に再度ウエットエッチングを実施する。

(もっと読む)

エッチング方法及びこれに用いられるシリコンエッチング液

【課題】少なくとも無機アルカリ化合物、ヒドロキシルアミン化合物、及びアニオン性化合物を含むシリコンエッチング液を、多結晶シリコン膜またはアモルファスシリコン膜に適用して、該膜の少なくとも一部を除去するエッチング方法。

【解決手段】アモルファスシリコン又は多結晶シリコン膜を的確かつ効率よく除去して半導体基板に凹凸を形成するに当たり、ウエハの中央部から端部に至るまでバランスよくエッチングするシリコンエッチング液及びこれを用いたエッチング方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】オン電流が大きい半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、単結晶シリコンからなり、上面が(100)面であり、前記上面にトレンチが形成された基板と、少なくとも前記トレンチの内部に設けられたゲート電極と、前記基板における前記トレンチを挟む領域に形成されたソース・ドレイン領域と、前記基板と前記ゲート電極との間に設けられたゲート絶縁膜と、を備える。前記トレンチは、シリコンの(100)面からなる底面、前記底面に接し、シリコンの(111)面からなる一対の斜面、及び前記斜面に接し、シリコンの(110)面からなる一対の側面により構成されており、前記ソース・ドレイン領域は、前記側面及び前記斜面に接し、前記底面の中央部には接していない。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】成長用基板に形成された窒化物半導体層を容易に剥離できる窒化物半導体発光素子の製造方法を提供する。

【解決手段】窒化物半導体発光素子の製造方法では、第1のサイズd1を有する第1基板31に窒化物半導体層11を形成する。窒化物半導体層11上に第1のサイズd1より小さい第2のサイズd2を有する第1接着層12aを形成し、第2基板32上に第2接着層12b形成する。第1および第2接着層12a、12bを重ね合わせ、第1および第2基板31、32を張り合わせる。第2のサイズd2より大きいまたは等しい第3のサイズd3を有する凹部31aを生じるように第1基板31を除去する。凹部31aに薬液を注入し、窒化物半導体層11が露出するまで第1基板31をエッチングする。薬液で、露出した窒化物半導体層11を更にエッチングし、窒化物半導体層11の露出面を粗面化する。

(もっと読む)

電界効果型トランジスタ

【課題】実用上十分なプロセスマージンを備える状態で、リーク電流の増大およびキャリア濃度の低下を招くことなく、ゲート電極とチャネル層との距離が短縮できるようにする。

【解決手段】InPからなる基板101の上に形成された電子供給層102と、電子供給層102の上に形成されたスペーサ層103と、スペーサ層103の上に形成されたチャネル層104と、チャネル層104の上に形成された障壁層105とを備え、障壁層105は、GaおよびAlの少なくとも1つと、Inと、Pとを含んだアンドープの化合物半導体から構成し、InPよりショットキー障壁高さが高いものとされている。

(もっと読む)

発光ダイオード及びその製造方法

【課題】放熱効率の高い発光ダイオードを低コストで製造する。

【解決手段】半導体層20等がチップ間で分離された状態で金属板70のウェットエッチングを行う(金属板切断工程)。このエッチングに際しては、放熱板30の材料に応じたエッチング液を用いることができる。また、このウェットエッチングの際にフォトレジスト層50が残存するような設定とされる。これにより、ダイシングシート100上で放熱板30も発光ダイオードチップ毎に分離され、図4(j)の形態が得られる。分離後にフォトレジスト層50を剥離液で除去することにより、最終的に図4(k)のように、分離された個々の発光ダイオード10が得られる。この製造方法において、最終的なチップの分離は、図4(j)に示されるウェットエッチングにより行われる。

(もっと読む)

基材表面処理方法

【課題】MEMSデバイス等の基材となる基板を研削し、形成されるデバイスに適した所望の厚さに基材を研削する工程において、研削によって薄板化された基材の処理面に生じる研削キズの平滑化と、研削クズの溶解および除去とをエッチングする際に、処理面以外の基材がエッチングによって溶解されない基材表面処理方法を提供する。

【解決手段】第1基材面と当該第1基材面に基材表面処理を行う処理面を有する基材を備え、第1基材面の少なくとも外縁に沿って保護膜を形成する保護膜形成工程と、第1基材面に形成した保護膜の内縁となる処理面を研削することで基材を薄板化する薄板化工程と、薄板化工程によって研削された処理面を、エッチングによって平滑化するエッチング工程とを備える。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】チャネル領域の低抵抗化を図りながら、ノーマリオフを実現する。

【解決手段】半導体装置を、キャリア走行層3及びキャリア供給層5を含む窒化物半導体積層構造と、窒化物半導体積層構造の上方に設けられ、活性化領域10と不活性領域10Aとを有するp型窒化物半導体層6と、p型窒化物半導体層の不活性領域上に設けられたn型窒化物半導体層7と、p型窒化物半導体層の活性化領域の上方に設けられたゲート電極13とを備えるものとする。

(もっと読む)

半導体発光装置の製造方法

【課題】光取り出し効率が高く、高出力、高効率で信頼性に優れた半導体発光素子の製造方法を提供する。

【解決手段】AlGaInP多重量子井戸からなる活性層13を有する発光ダイオードにおいて、光取り出し層であるn型AlGaInPクラッド層12の表面に光取り出し効率向上のための凹凸構造を設ける。凹凸構造は臭化水素酸を含む水溶液をエッチャントとして用い、マスクを形成する工程を用いることなく異方性エッチングにより形成する。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

微細パターンの形成方法及びこれを用いた半導体発光素子の製造方法

【課題】本発明は、微細パターンの形成工程に関する。

【解決手段】微細パターンの形成方法は、c面六方晶系半導体結晶を設ける段階から始まる。上記半導体結晶上に所定のパターンを有するマスクを形成する。次いで、上記マスクを用いて上記半導体結晶をドライエッチングすることで上記半導体結晶上に1次微細パターンを形成し、上記1次微細パターンが形成された半導体結晶をウェットエッチングすることで上記1次微細パターンが水平方向に延びた2次微細パターンを形成する。ここで、上記ウェットエッチング工程から得られた2次微細パターンの底面と側壁は夫々固有の結晶面を有することができる。本微細パターンの形成工程は、半導体発光素子に非常に有益に採用されることができる。特に微細パターンが求められるフォトニック結晶構造または表面プラズモン共鳴原理を用いた構造に有益に採用されることができる。

(もっと読む)

半導体基板の製造方法

【課題】厚みのある半導体基板に対し、正確な位置でのへき開を可能とするような十分な深さのガイド溝を形成する半導体基板の製造方法を提供する。

【解決手段】本発明に係る半導体基板の製造方法は、インジウムリン化合物半導体またはガリウムヒ素化合物半導体からなる基板本体の表面に、開口幅が略40um以下である開口部が形成されたマスクを、その開口部が基板本体のへき開線に沿って延びるように転写する工程と、基板本体の表面に臭素系のエッチング液を用いてウエットエッチング処理を施すことによって、縦断面で略V字型を有するガイド溝を形成する工程と、ガイド溝に反応性ガスを用いてドライエッチング処理を施すことによって、底部の縦断面形状を略V字型に保持したままガイド溝の溝深さを深くする工程と、を含むものである。

(もっと読む)

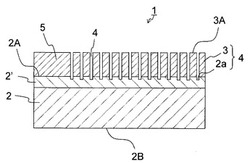

実質的に垂直な側面を有するAlN層を得る方法

【課題】層がその上に作製される基板に対して実質的に垂直な側面を有するAlN層を作製する方法を提案する。

【解決手段】基板(2)の表面(2’)に対して実質的に垂直な側面を有するAlN層を作製する方法において、基板(2)上にAlN成長層(4,4’)を形成する段階と、少なくとも前記成長層上にAlN層(31)を堆積する段階と、その少なくとも1つの縁部が、前記基板(2)の表面(2’)または前記成長層(4)の表面(4’)に実質的に垂直な平面において少なくとも1つの縁部(10,12,14)または前記成長層(4,4’)の側面(10a,10b)と整列されるように、AlN層を覆ってマスク層(40,40’)を形成する段階と、を有する方法が開示される。

(もっと読む)

半導体装置の製造方法および半導体装置の製造装置。

【目的】シリコンウェハに形成する溝の深さを高精度に制御できる半導体装置の製造方法およびその製造装置を提供する。

【解決手段】シリコンウェハ21に形成する溝の深さをモニタウェハ22の貫通時間と追加エッチング時間により制御する。まず、所望の深さの溝をシリコンウェハ21に形成する時間より短い時間で貫通するモニタウェハ22を準備し、このモニタウェハ22をシリコンウェハ21と同時にエッチングする。続いて、モニタウェハ22が貫通する時間(貫通時間)からエッチングレートを算出する。続いて、このエッチングレートから追加エッチング時間を割り出す。さらに、この追加エッチング時間でシリコンウェハ21をエッチングすることで、実験によるエッチングレートに関する事前データに頼ることなく、リアルエッチングでシリコンウェハ21に所望の深さの溝を正確に形成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

1 - 20 / 127

[ Back to top ]