Fターム[5F044KK17]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724) | バンプ (984) | 形状、配置 (280)

Fターム[5F044KK17]に分類される特許

161 - 180 / 280

半導体装置の製造方法

【課題】先ダイシング法と、フリップチップボンディングを採用した実装プロセスとを連続して行うことが可能であり、製造プロセスの簡素化と、製品中にボイドが無く信頼性の向上に寄与しうる半導体装置の製造方法を提供する。

【解決手段】回路表面に接着フィルム3が接着され、かつ該回路毎に区画する溝6が形成されてなるウエハ1の回路表面側に表面保護シートを貼着する工程、上記ウエハの裏面研削をすることで個々のチップへの分割を行う工程、個別のチップを接着フィルムとともにピックアップし接着フィルムを介して、チップ搭載用基板にダイボンドする工程、およびダイボンドされた接着フィルム付きチップを加熱しチップ搭載用基板に固着する工程を含み、かつ接着フィルムをウエハに接着した後、チップをチップ搭載用基板に固着するまでの段階で、接着フィルムを含む積層体を、常圧に対し0.05MPa以上の静圧により加圧する工程を1回以上含む。

(もっと読む)

電子部品およびその製造方法。

【課題】2つの電子部品を基板と垂直な方向に積み重ね、狭小なピッチで二次元的に配列された端子間を接続するためのコネクタを備える電子部品を提供する。

【解決手段】電子部品1は、突起電極201を備える他の電子部品2に接続される電子部品であって、基板10と、前記基板に形成された導電性の配線要素102と、前記配線要素から前記基板の接合面10aに対して垂直な方向に複数部位が突出している脚部101と、前記脚部のそれぞれの突端から前記脚部の内側に向かって突出しているストッパ面103と、前記ストッパ面のそれぞれの突端から前記脚部の外側に向かって後退しながら前記脚部の基端から突端に向かう方向に延びるガイド面104とを備えるとともに前記配線要素の上に堆積した導電性15の膜からなり、前記突起電極に対してスナップフィットするコネクタ100と、を備える。

(もっと読む)

半導体装置

【課題】十分な接合の基に実装した半導体に所定の電気特性が得られる信頼性の高い半導体装置とする。

【解決手段】基板2に半導体1を基板電極2A、半導体電極3を介し圧接してそれらを電気的に接合した状態で、基板2、半導体1間を接着・封止材4により接着・封止した半導体装置において、基板電極2Aと半導体電極3との少なくとも1つの組は、それら基板電極2Aおよび半導体電極3の一方または双方が前記圧接の方向に直角な向きに対して傾斜した圧接面2A−1などを有して接合されていることを特徴として、上記の目的を達成する。

(もっと読む)

基板の接合方法及び基板接合体

【課題】短絡や導通不良のような不具合の発生を抑えて信頼性を向上させることができる基板の接合方法及び基板接合体を提供することを目的とする。

【解決手段】リジッド基板2に半田粒子6a入りの熱硬化性樹脂7aを供給し、基板2の上方にフレキシブル基板3を配置した後、降下させた熱圧着ツール10によりフレキシブル基板3を介して熱硬化性樹脂7aを押圧加熱し、熱硬化性樹脂7aに含まれる半田粒子6aを溶融させるとともに熱硬化性樹脂7aを熱硬化させて両基板2,3を接合させる。そして、熱硬化物7から熱圧着ツール10を離間させて熱硬化物7を冷却し、半田粒子6aの溶融物(半田溶融物6b)が固化した半田固化物6によって両電極4,5を接合させる。接合される両電極4,5の少なくとも一方の表面に両電極4,5の並設方向と直交する方向に延びた複数の溝8を設けておき、半田溶融物6bが溝8に沿って濡れ広がった状態で固化するようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、X線による電極と半田バンプとの接合状態の検査を、簡易かつ迅速に行うことができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体装置100は、半導体チップ10と、半導体チップ10に設けられた第1形状90を有する第1電極30と、半導体チップ10が実装された実装部20と、実装部20に設けられた、第1形状90とは異なる第2形状92を有する第2電極32と、第1電極30及び前記第2電極32を接合する第1半田バンプ40と、を具備し、第1半田バンプ40は、第1電極30及び前記第2電極32の表面全体を覆っている。第1半田バンプ40に対してX線による検査を行い、第1半田バンプ40の形状から接合状態の良否を判定する。

(もっと読む)

半導体実装用基板

【課題】半導体実装用基板のソルダーレジスト開口部全面にハンダを供給した場合に、従来各半導体接合用電極端子に略定量のハンダが供給されず、特定の電極端子に過多のハンダ量が供給されたり、逆にハンダ不足になり、高品質のハンダプリコートができなかった。

【解決手段】前記接合用基板電極端子の配列パターンが不均一となっている領域に、前記接合用基板電極端子4と同一形状のダミー用基板電極端子9を付加して、前記領域内に前記接合用およびダミー用電極端子(以下、両者を配置電極端子という)を、略均一に配列し、互いに隣接する前記配置電極端子と前記ソルダーレジスト開口部とが略均一な配列パターンとなるようにした。

(もっと読む)

半導体装置およびそれに用いる配線基板

【課題】配線基板に搭載する半導体チップ等の電子部品のファインピッチ化に伴い、配線基板のランド上に形成されるはんだバンプが小さくなっても、はんだリフロー時に電子部品の電極ポストと配線基板のランドとの直接接触の発生を防止して、良好な接続信頼性を維持できる構造を備えた半導体装置およびそれに用いる配線基板を提供する。

【解決手段】配線基板上に少なくとも一体の電子部品をはんだバンプ接続により搭載した半導体装置において、上記配線基板上に、実質的に同一サイズで配設ピッチの異なる複数のランドが、配設ピッチの大きさによって区分された複数の区域に配設され:個々の区域のランド上には、区域間での比較において配設ピッチの大小関係に対応する大小関係となるバンプサイズではんだバンプが形成されており:配設ピッチが異なり、それに対応してバンプサイズが異なる複数の区域に亘って、前記一体の電子部品がはんだバンプ接続されている。

(もっと読む)

発光装置及びその製造方法

【課題】応力が低減され、信頼性が改善された発光装置及びその製造方法を提供する。

【解決手段】半導体発光層を含む積層体と、前記積層体の上に設けられた電極と、前記電極の上に設けられたパッド電極と、を含む発光素子と、金属ボンディング層を有する実装部材と、前記パッド電極と、前記金属ボンディング層と、を接着し金を含む合金半田と、を備え、前記パッド電極は、前記電極の上に設けられ前記電極よりも厚い第1の金層及び前記第1の金層の上に設けられた第1の金属バリア層を少なくとも有し、前記合金半田の融点は、前記第1の金属バリア層と前記合金半田を構成するそれぞれの元素との合金の融点よりも低いことを特徴とする発光装置が提供される。

(もっと読む)

ICチップ

【課題】ICチップをACFによって固定した場合に、バンプ間の絶縁性を高めることができるICチップを提供する。

【解決手段】ICチップ12の底面に千鳥状に配置されたバンプ14において、第1列のバンプ14と第2列のバンプ14との間に間隙を設け、この間隙AがACF18に含まれる導電性粒子20の直径の2倍以上である。

(もっと読む)

半導体装置およびそれに用いる配線基板

【課題】両面または多層の配線基板に半導体チップをフリップチップ方式を用いて実装される半導体装置において、半導体チップと配線基板との接合状態を安定させ、高い接続信頼性を有する半導体装置、およびそれに用いる両面または多層の配線基板を提供する。

【解決手段】半導体装置1は、略矩形状の一主面の対向する二辺に複数の電極パッド55a〜55hが形成されたICチップ50と、前記電極パッドと対応するIC接続端子35a〜35hが形成された多層配線基板10とを有している。複数のIC接続端子35a〜35hと対応する電極パッド55a〜55hとは、それぞれ半田バンプ56a〜56hにより接合されている。電極パッド55a〜55hと対応するIC接続端子35a〜35hの直下には、接合部支持ビア36a〜36hが、各接合部支持ビアの中心点C5a〜C5hを結んで形成される多角形T1の略中心にICチップ50の重心Gがあるように配設されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ESD保護素子対策が十分の特定の端子を優先的に最初に除電する事により、残りの端子の保護素子のサイズを小さくでき、チップ全体としてESD保護素子サイズを小さくできる半導体装置及びその製造方法を提供する。

【解決手段】複数の端子を有する半導体チップを複数個積層する半導体装置の製造方法において、隣接する2つの半導体チップ1A、1Bを電気的に接続する前記複数の端子のうち、少なくとも一方の半導体チップ1Aの端子2、3の一部(ボール端子3)は、一方の半導体チップ1の残りの端子(ボール端子2)より先に他方の半導体チップ1Bの端子(金バンプ10)に接触する。即ち、ボール端子3はボール端子2よりも径が大きいので高さが高く、他の端子より先に金バンプ10に接触する。

(もっと読む)

半導体素子実装用基板およびその製造方法ならびに半導体装置

【課題】 超音波ボンディングによる突起電極の接合強度を高めた半導体素子実装用基板およびその製造方法ならびに半導体装置を提供する。

【解決手段】 絶縁基板11の上面に、下面に複数の電極端子22が形成されて電極端子22に突起電極23を備えた半導体素子21を実装するための、電極パッド12が形成された実装部11を有して成り、電極パッド12に突起電極23を当接させて半導体素子21の上面から超音波を印加して突起電極23を電極パッド12に接合する半導体素子実装用基板19であって、電極パッド12は、突起電極23が当接する領域の中央部12aが外周部12bよりも低く、かつ中央部12aと外周部12bとの間に環状に隙間12cが設けられている。電極パッド12の中央部12aと外周部12bとが突起電極23と噛み合うとともに隙間12cにより接合時の応力を緩和できるので、接合強度および実装信頼性を高めることができる。

(もっと読む)

部品付き配線基板の製造方法、はんだバンプを有する配線基板の製造方法、配線基板

【課題】はんだバンプのコプラナリティの測定値を低減でき、しかもボイドの発生を防止できる部品付き配線基板の製造方法を提供する。

【解決手段】はんだバンプ成形工程では、複数のはんだバンプ22の頂部27を平坦化及び粗化する。フラックス供給工程では、平坦化及び粗化された複数のはんだバンプ22の頂部27にフラックス28を供給する。加熱溶融工程では、ICチップ45における複数の接続端子47を、フラックス供給済みの複数のはんだバンプ22に対応させて配置し、この状態で複数のはんだバンプ22を加熱溶融する。これにより、はんだバンプ22に含まれているフラックス28は、加熱溶融工程において加熱溶融される際に気化して確実に頂部27から外部に放出される。

(もっと読む)

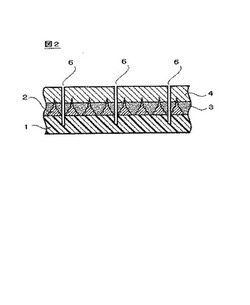

半導体パッケージ基板とその製造方法

【課題】Cuを主体とする金属層と絶縁性樹脂層との密着性に優れた、実装信頼性の高い半導体パッケージ基板とその製造方法を提供すること。

【解決手段】外部部品と電気的に接続される突起状電極部6を有する、Cuを主体とする金属層4bと、金属層4b上の、突起状電極部6の外部部品との接続面を除いた領域に形成され、且つ、突起状電極部の側面を覆う絶縁性樹脂層2と、金属層4bと絶縁性樹脂層2との間に形成されたNi合金層4aと、金属層4bの、Ni合金層4aが形成された面と反対の面上に形成され、半導体素子が接着される接着層とを有する。

(もっと読む)

回路基板接合構造体およびその製造方法

【課題】第1の回路基板と第2の回路基板との接合信頼性を向上させる回路基板接合構造体を提供する。

【解決手段】第1のバンプ電極2の第1の中心線L1と、第2のバンプ電極4の第2の中心線L2とが、重ならずに偏移するように、上記第1のバンプ電極2の頂面と上記第2のバンプ電極4の頂面とが、対向して接合されている。小面積の第2のバンプ電極4が塑性変形するときに、大面積の第1のバンプ電極2の側面までの距離が短い方は、自由端となり、バンプ電極の変形拘束をうけないため、小面積バンプ電極4が塑性変形するとき、大面積バンプ電極2の自由端の方向へ接合界面での横すべりが生じやすく、その結果、小面積バンプ電極4が容易に変形しやすくなる。

(もっと読む)

半導体装置

【課題】半導体素子とインタポーザ基板との接合品質を安定化させる。

【解決手段】半導体装置1は、フィルム基板8に実装されてシリコンにより構成されたインタポーザ基板2と、液晶を駆動するためにインタポーザ基板2に実装された半導体素子3とを備え、インタポーザ基板2は、半導体素子3側に形成された基板突起電極4を有し、半導体素子3は、基板突起電極4と接合する素子突起電極5を有し、素子突起電極5の素子接合面の面積が、基板突起電極4の基板接合面の面積よりも大きい。

(もっと読む)

チップキャリア及び半導体装置並びにチップキャリアの製造方法

【課題】チップキャリアの配線層とバンプ形成面を分離することによりICチップ実装後の高い接合信頼性が得られるチップキャリア及び半導体装置を提供することを目的とする。

【解決手段】絶縁基板13の片面に電極パッド16と接合ろう15からなるバンプ21が、もう一方の面に配線層17及び配線層19からなる多層配線を形成してチップキャリア10を得る。さらに、ICチップのパッドとチップキャリア基板のバンプ21とを接合し半田フリップチップ実装して半導体装置を得る。

(もっと読む)

電気光学装置、電気光学装置用基板、半導体素子、及び電子機器

【課題】すべてのバンプ部と端子部との接続抵抗を小さく抑えるとともに接続抵抗を均一化し、半導体素子の導通不良を少なくできる電気光学装置、電気光学装置用基板、半導体素子、及び電子機器を提供する。

【解決手段】半導体素子が実装された電気光学装置用基板を備えた電気光学装置であって、半導体素子は複数のバンプ部を備え、電気光学装置用基板は複数の端子部を備え、複数のバンプ部と複数の端子部とは導電粒子を含む異方性導電膜を用いて電気的に接続され、複数のバンプ部及び端子部は、半導体素子の所定の辺に沿ってそれぞれ配列する複数の列をなすとともに、所定の辺に近い側の第1の列と第1の列よりも所定の辺から遠い側の第2の列とを含み、第2の列を構成するバンプ部及び端子部の平面投影面積を第1の列を構成するバンプ部及び端子部の平面投影面積よりも小さくする。

(もっと読む)

プリント配線板、プリント配線板の電極形成方法およびハードディスク装置

【課題】フリップチップ実装される半導体素子接合用の電極を、ソルダーレジスト被膜により規定した配線パターンの露出部分により形成したプリント配線板に於いて、強固なはんだ接合を可能にするとともに、接合部の高密度化が図れるプリント配線板を提供する。

【解決手段】プリント配線板11は、フリップチップ実装される半導体素子の実装面部に所定の間隔を存して配列された、半導体素子接合用の電極形成部分を有する多数本の配線パターン12p,12P,…と、部品実装面部を電極形成部分を残しソルダーレジスト(SR)で被覆することにより電極形成部分に露出形成された多数の電極12,12,…と、各電極12,12,…に一体に設けられ、半導体素子の電極に接合する部分の電極幅を他の部分より広幅に形成し、この広幅の部分が上記電極の配列方向に隣接しないように該電極の延長方向に位置的にずらせて配置した電極拡張部12a,12a,…とを有して構成される。

(もっと読む)

半導体装置

【課題】半導体チップや回路基板の微細化に対応すると共に、信号や電源、電極位置の配線自由度向上を図る。これによって半導体チップの小型化や複数の半導体チップの積層を容易にする技術を提供する。

【解決手段】金属細線1の先端の金属ボール2からなる突起部が接触半導体チップもしくは電気的接続配線層を有する基材の主面にある絶縁層5の上に配置され、さらに前記金属細線1が前記絶縁層5に倣うように配置され、且つ前記金属細線1が前記金属ボール2以外の部位で前記絶縁層5の開口に露出する電極4に接合されて、前記半導体チップもしくは前記基材の主面上に外部配線を形成する。

(もっと読む)

161 - 180 / 280

[ Back to top ]