Fターム[5F044KK17]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724) | バンプ (984) | 形状、配置 (280)

Fターム[5F044KK17]に分類される特許

261 - 280 / 280

基板間の電極間接合方法及び構造体

【課題】基板間の接合の際の印加荷重の加え過ぎが防止され、基板間での線膨張係数差などに起因する内部応力によって歪を生じる恐れを少なくした基板間の電極間接合方法ないし構造体である。

【解決手段】第一の基板1に、電極バンプ5、補強バンプ6、ストッパーバンプ7を形成し、第二の基板8に、対応する電極バンプ5に当接する電極パッド10、対応する補強バンプ6に当接する補強パッド11、対応するストッパーバンプ7に当接して第一の基板1と第二の基板8間の接合間隔を規定するストッパーパッド12を形成し、両基板1,8を相対向して整合し、荷重を印加しながら電極バンプ5及び補強バンプ6を変形して行き、ストッパーバンプ7とストッパーパッド12が互いに押圧力を受けるまで電極バンプ5及び補強バンプ6を変形する。これにより電極バンプ5と電極パッド10及び補強バンプ6と補強パッド11を接合させ、この接合により両基板1,8間の電極同士を接合する。

(もっと読む)

半導体装置及びその製造方法。

【課題】 チップ搭載基板のバンプとベース基板のバンプとを積層し接続する半導体装置において積層時の位置ずれを抑制する構造を提供する。

【解決手段】 半導体チップ1が搭載され、この搭載された半導体チップの周辺に沿って設けられたバンプ10が複数個形成されたチップ搭載基板2と、配線パターン5が形成され、この配線パターンと電気的に接続されたバンプ7が複数個形成されたベース基板3とは積層され、チップ搭載基板側バンプの各個は、対応するベース基板側バンプのそれぞれに積層されて接続され、ベース基板側バンプにおいて、対向する2辺に対向して配置された1対のベース基板側バンプにはその上に積層された1対のチップ搭載基板側バンプが、1対のベース基板側バンプ間の外側もしくは内側にずれるように積層され、これを前記プレス時まで仮固定する事により、積層時の位置ずれを抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体チップがバンプを介して配線基板に電気的接続された半導体装置であって、半導体チップを配線基板に実装する際に、バンプからの反作用により半導体チップおよび配線基板に負荷される荷重が低減された信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 半導体チップの電極表面および配線基板に接合された小さなばね定数を有するバンプの接合端面を平坦化および活性化し、高温高圧を負荷する必要のない常温接合技術を用い、バンプを介して半導体チップの電極と配線基板の電極とを電気的接続する。

(もっと読む)

電極気密封止を用いた高信頼性半導体装置

【課題】 半導体チップが配線基板に電気的接続された半導体装置であって、分解が容易でリペアやリサイクルに有利で、高い信頼性を有する半導体装置を提供する。

【解決手段】 半導体チップ上に形成された電極および配線基板上に形成された電極を真空または電極と反応しないガスを封止した枠構造を用いて封止することによって、封止樹脂を用いることなく、これらの電極が酸素や水分からの攻撃により劣化することを防止し、さらに、半導体チップ上に形成された電極と配線基板上に形成された電極とを接触により電気的接続を達成することによって、分離可能性を向上させる。

(もっと読む)

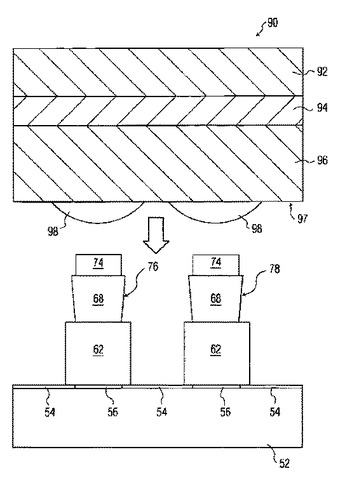

2次元超音波トランスデューサアレイ

超音波トランスデューサ(100)は、集積回路(52)、及び集積回路にフリップチップバンプ(76、78)を介して結合された音響素子(92、94、96)のアレイを有する。フリップチップバンプは1:1より大きいアスペクト比を有する高アスペクト比バンプを有する。アスペクト比はバンプ高さ(82)のバンプ幅(84)に対する比から成る。  (もっと読む)

(もっと読む)

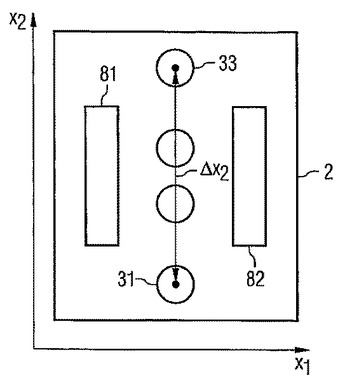

フリップチップ構造の電気素子

本発明は、熱拡散係数αpを有する支持体基板(1)およびこの支持体基板上にバンプ(31〜34)を介して固定されたフリップチップ構造のチップ(2)を有する電気素子に関する。チップ(2)は第1の方向x1において熱拡散係数α1を有し、ここで第1の拡散差はΔα1=|αp−α1|である。さらにチップ(2)は第2の方向x2において熱拡散係数α2を有し、ここで第2の拡散差はΔα2=|αp−α2|である。Δx1は第1の方向x1での各端部バンプ(31,32)の中心(310,320)間の距離である。Δx2は第2の方向x2での各端部バンプ(33,34)の中心(330,340)間の距離である。ここでΔα1>Δα2のときΔx1<Δx2が相当し、Δα1<Δα2のときΔx1>Δx2が相当する。これにより、温度変化があった場合に端部バンプへ作用するせん断応力が最小化される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の組み立てにおいてフリップチップ接続の信頼性の向上を図る。

【解決手段】 パッケージ基板5において複数のフリップチップ用端子5eの列の端部にダミー端子5dが設けられていることにより、フラックスや半田の流れをダミー端子5dによって抑制して複数のフリップチップ用端子5e上に半田層4を形成することができ、これにより、フリップチップ用端子5eに近接して設けられたワイヤ接続用端子5fに半田を付着させることなく、各フリップチップ用端子5e上に形成する半田層4の厚さを十分に確保することができ、その結果、フリップチップ接続の信頼性の向上を図ることができる。

(もっと読む)

半導体チップの接続構造及びこれに用いる配線基板

【課題】半導体チップの厚みが薄い場合でも優れた接続信頼性を得ることが可能な半導体チップの配線基板への接続構造及びこれに用いる配線基板を提供する。

【解決手段】周縁部に多数の電極2を有する半導体チップ1と、これに相対する電極5を有する配線基板4の接続構造であって、前記半導体チップおよび/または配線基板の電極が絶縁面より突起してなり、少なくとも接続後の半導体チップの周縁部電極に囲まれた領域内に前記突起電極と略同等高さのダミー電極6が設けられ、前記ダミー電極は接続面を投影した時、三角状、エル(L)字状のいずれかもしくはこれらの2種が接続領域内に複数個存在し、さらにこれらの頂点が接続領域の中央部に向けて形成されており、厚みが0.3mm以下の前記半導体チップと配線基板とが接着剤11で接続されてなる半導体チップの接続構造。

(もっと読む)

半導体装置及び電子機器

【課題】電極又はリードの間隔の狭小化を防止することができる半導体装置及び電子機器を提供することにある。

【解決手段】半導体装置は、電極12を有する半導体チップ10と、リード22が形成された基板20と、電極12とリード22との接合部30と、を有する。接合部30は、共晶合金32を含む。電極12のリード22に対する接合面と、リード22の電極12に対する接合面とは、異なる大きさを有するように形成されている。共晶合金32を含む接合部30の外形は、電極12及びリード22のうち接合面の大きい方の外形と同等又はそれより小さく形成されてなる。

(もっと読む)

半導体部品の実装方法および実装装置

【課題】 十分に信頼性の高い理想的な接合状態を得るのに最適な半田バンプを有する半導体部品の実装方法および実装装置を提供することを目的とする。

【解決手段】 半田バンプ26aを有する半導体部品26および半田バンプ42aを有する基板42を加熱し、半田バンプ26a、42aの一端部を凹凸を有するステージに押圧して塑性変形させ、十分な面積の新生面を形成する。前記新生面にフラックス塗膜32を転写して塗布する。半導体部品26の半田バンプ26aを基板42の半田バンプ42aの上に載置して、半導体部品26を基板42に搭載する。半導体部品26および基板42を加熱して半田バンプ26a、42aを溶融接合する。

(もっと読む)

低耐熱性表面実装部品及びこれをバンプ接続した実装基板

【課題】回路基板にはんだ付けされている低耐熱性表面実装部品を、回路基板や低耐熱表面実装部品の性能に影響を与えることなく、回路基板から取り外すことができるようにする。

【解決手段】低耐熱性表面実装部品1の面の外周寄り2でのはんだバンプ3を、中央寄りのはんだバンプ3よりも、低融点のはんだで形成する。回路基板の低耐熱性表面実装部品1の部分を局所的に加熱し、はんだバンプを溶融して取り外すのであるが、このように局部加熱すると、低耐熱性表面実装部品1の中央寄りに対し、外周寄りでは加熱温度が低い。このため、外周寄りでは、融点の低いはんだによるはんだバンプを用い、このような低い加熱温度でも、はんだバンプが溶融するようにする。これにより、低耐熱性表面実装部品1の面全体のはんだバンプが溶融する。

(もっと読む)

実装構造およびその製造方法

【課題】半導体装置と回路基板との間の接続部位におけるショートの防止。

【解決手段】端子電極2を有する半導体装置100が、入出力端子電極8を有する回路基板9に実装され、端子電極2と入出力端子電極8とが対向配置されて電気接合層13を介して電気接続されている。IC基板1の一面1aに設けられた端子電極2と、一面1aに設けられたパッシベーション4と、パッシベーション4を覆う保護膜5とを有する。端子電極2の上部はパッシベーション4と保護膜5とが除去されており、端子電極2上に凹部45が形成されている。電気接合層13は、その周囲が凹部45によって囲まれることで周囲への流出が阻止される。

(もっと読む)

配線回路基板および半導体装置

【課題】 大きな圧力を加えずとも、突起電極と接続端子とを確実に接続することができ、導体パターンを高密度に形成しても、断線を防止することのできる、配線回路基板、および、その配線回路基板に半導体素子が搭載された半導体装置を提供すること。

【解決手段】 接続端子4を一体的に有する導体パターン3を備える配線回路基板1において、接続端子4には、接続側の表面に、接続端子4の幅方向の中央部において、その長手方向にわたって凸部5を設ける。接続端子4とバンプ14とは、圧着(熱圧着)により、凸部5をバンプ14に減り込ませて接続する。この接続では、接続端子4の基部6がバンプ14に減り込まなくても、凸部5のバンプ14に対する減り込みにより、これらを接続することができる。

(もっと読む)

半導体チップの接続構造及びこれに用いる配線基板

【課題】 半導体チップの厚みが薄い場合でも優れた接続信頼性を得ることが可能な半導体チップの配線基板への接続構造及びこれに用いる配線基板を提供する。

【解決手段】半導体チップ1と配線基板4の接続構造であって、半導体チップおよび/または配線基板に突起電極2が設けられ、突起電極表面の平均粗さ(JIS、B0601、10点平均粗さ)が0.5μm以上であり、接続後の半導体チップの周縁部電極に囲まれた領域内に突起電極と略同等高さのダミー電極6が設けられ、ダミー電極は接続面を投影した時、三角状、エル(L)字状のいずれかもしくはこれらの2種、または、半円弧状、コの字状のいずれかもしくはこれらの2種が複数個存在し、さらにこれらの頂点が接続領域の中央部に向けて形成されており、厚みが0.3mm以下の前記半導体チップと配線基板とが接着剤11で接続されてなる半導体チップの接続構造。

(もっと読む)

部品実装配線基板および配線基板への部品の実装方法

【課題】 配線基板にバンプを形成し、接合する半導体チップのフラックス洗浄を不要とし、応力がかかっても部品側や配線基板側には影響が及び難い部品実装配線基板、および配線基板への部品の実装方法を提供すること。

【解決手段】 配線基板21には、銅メッキ膜をエッチングした円錐台形状の銅核26とそれを覆う球殻状の半田27とからなるバンプを設ける。半導体チップ11には、接合パッドとその周縁部に、銀の超微粒子が分散されたペーストによる導電性膜を形成し、耐食性付与のメッキ膜を形成して接合パッド18とし、それを覆って一面にフラックス樹脂膜19をペースト状として塗布する。半導体チップ11を配線基板21に位置合わせして加熱し、半田27をリフローさせ、フラックス樹脂膜19を垂れ下がらせ完全硬化させて実装する。

(もっと読む)

実装済基板、電子部品実装方法、電子部品、及び配線基板

実装済基板(40)は、基板電極(22)が形成された配線基板(20)と、バンプ(13)が形成された電子部品(10)と、配線基板(20)と電子部品(10)とを接着する非導電性樹脂(30)とを備える。バンプ(13)の先端部(131)と基板電極(22)との間の領域は、先端部(131)と基板電極(22)とが接触している複数の接触領域(51)と、複数の接触領域(51)の周囲において非導電性樹脂(30)が介在する樹脂介在領域(52)とを有する。複数の接触領域(51)はバンプ(13)の先端部(131)に形成された複数の突起が押圧により基板電極(22)に接して潰れた領域であり、これにより、バンプ(13)と基板電極(22)との電気的接続の信頼性が高められる。 (もっと読む)

平坦な上面を有するパッドの製造方法

電子部品において平坦な上面を有するパッドを作製する方法であって、a)第一電子基板上に硬化性シリコーン組成物の平坦な上面を有する堆積物をステンシル印刷する過程であって、第一電子基板が半導体ダイ又は半導体ダイ取り付け部材から選択され、平坦な上面を有する堆積物のステンシル印刷がダウンステップステンシルを通したスクイジーにより行われる、堆積物をステンシル印刷する過程と、b)平坦な上面を有する堆積物を硬化させる過程であって、それにより、平坦な上面を有するパッドを形成する、堆積物を硬化させる過程と、任意にc)平坦な上面を有するパッドの上面に第二電子基板を接着する過程であって、第二電子基板は半導体ダイ又は半導体ダイ取り付け部材から選択される、第二電子基板を接着する過程、並びに、任意にd)過程a)、b)及びc)を反復する過程を包含する、パッドを作製する方法。

(もっと読む)

(もっと読む)

集積型電子チップ及び相互接続デバイス、並びにそれを製造するための方法

【課題】 集積型電子チップ及び相互接続デバイス、並びにそれを製造するための方法を提供すること。

【解決手段】 半導体デバイスと、マザーボードに接続するためのコネクタとを含む集積構造を形成するための方法が説明される。第1の層(26)が除去用放射線を通すプレート(23)上に形成され、第2の層(32)が半導体デバイス(31)上に形成される。第1の層は、マザーボードへの接続に必要とされる間隔に応じた第1の間隔距離だけ離されたボンディング・パッド(27p)に接続される導体の第1の組(27)を有する。第2の層は、半導体デバイスに接続される導体の第2の組(33)を有する。第1の層及び第2の層は、ボンディング・パッドの間隔より短い間隔を有するスタッド/バイア・コネクタ(29、36)を用いて接続される。このようにして、半導体デバイスが第1の層に取り付けられ、導体の第1の組と第2の組とがスタッドを通して接続される。第1の層とプレートとの間の界面が、該プレートを透過する除去用放射線(45)によって除去され、それによって該プレートが分離される。次いで、コネクタ構造(47、48、49)がボンディング・パッドに取り付けられる。本方法は、低コストで、高密度にパッケージされたデバイスを製造することを可能にする。

(もっと読む)

半導体装置

【課題】 はんだ接合部の応力集中を緩和しディバイスに発生する内部熱を効率的に放熱して信頼性の向上を図る。

【解決手段】 実装面2aに接続電極6と周辺補強用ダミー電極7と中央補強用ダミー電極8が形成されたディバイス2と、接続ランド10と周辺補強ランド11と中央補強ランド12とが形成されディバイス2をディバイス実装面3a上に実装する実装基板3とを備える。実装基板3には、中央補強ランド12に接続される放熱ビア14と、裏面3bに放熱パターン15が形成され、中央補強ランド12がディバイス2からの発生部を兼用して裏面3bからの放熱を行う。

(もっと読む)

フリップチップ搭載用多層プリント配線板

【課題】 内層金属芯と外層金属箔との接続性、放熱性、吸湿後の耐熱性等に優れたフリップチップボンディング用多層プリント配線板を得る。

【解決手段】 表面は台形状の金属突起、裏面は複数個の円錐台形状金属突起を有する金属芯を用いたボールグリッドアレイの半導体プラスチックパッケージ用プリント配線板であって、多層積層時に表面平坦な両面銅張多層板とし、表面の半導体チップを搭載する台形状突起部上に流れ出した樹脂層をサンドブラスト法で除去して露出し、裏面は円錐台形状突起部先端が裏層銅箔と接続するように形成された熱放散用ハンダボールパッドとする。さらに、熱硬化性樹脂として多官能性シアン酸エステル系樹脂組成物を用いる。

【効果】 内層金属芯と裏面外層金属箔層との接続性、熱の放散性、吸湿後の耐熱性、プレッシャークッカー後の絶縁性、耐マイグレーション性などに優れ、大量生産性に適した新規な構造のフリップチップ搭載用プリント配線板を得ることができた。

(もっと読む)

261 - 280 / 280

[ Back to top ]